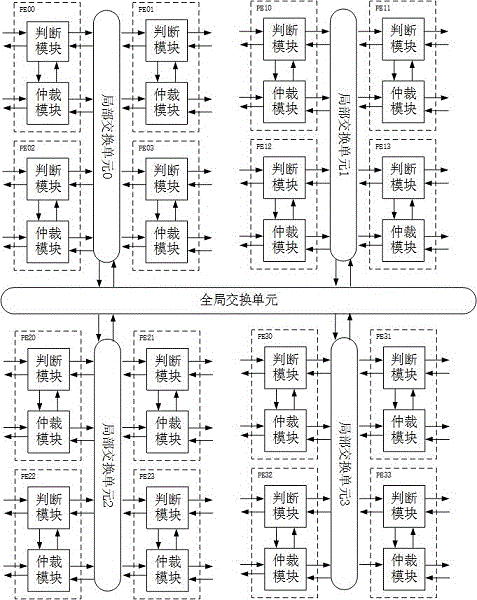

Intra-cluster storage concurrent access local-preference switching circuit in array processors

A local, block-storage technology, applied in electrical digital data processing, instruments, etc., can solve problems such as low resource utilization, long data access delay, and difficulty in meeting real-time requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

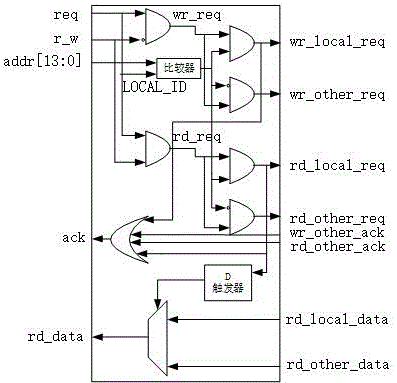

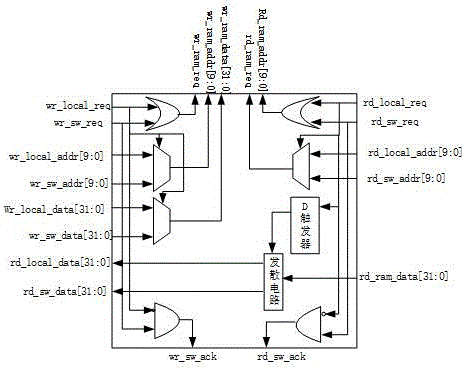

[0024] The technical solution and working principle adopted by the present invention will be described in detail below in conjunction with the accompanying drawings.

[0025] Circuit port description:

[0026] signal name Signal description meaning req out Request signal from the processor side, active high r_w out Read and write operation indication signal from the processor side, high level indicates read operation, low level indicates write operation wr_data[31:0] out Write data information from the processor side addr[13:0] out Read / write address information from the processor side ack IN Read / write response signal from processor side rd_data[31:0] IN Data information read from the processor side wr_ram_req out Write request sent to memory block, active high wr_ram_addr[9:0] out Write address information sent to the memory block wr_ram_data[31:0] out Write data information sent to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More