Preventing Dynamic Obfuscation of Scan Chain Structures Using Scan Chains to Attack Integrated Circuit Chips

An integrated circuit and scan chain technology, applied in the field of intellectual property and security protection of integrated circuit chips, can solve problems such as being breached, and achieve the effects of low additional area and power consumption, small design and test procedures, and increased test time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0061] Apply the integrated circuit chip designed by the present invention to dynamically confuse the scan chain structure for testing:

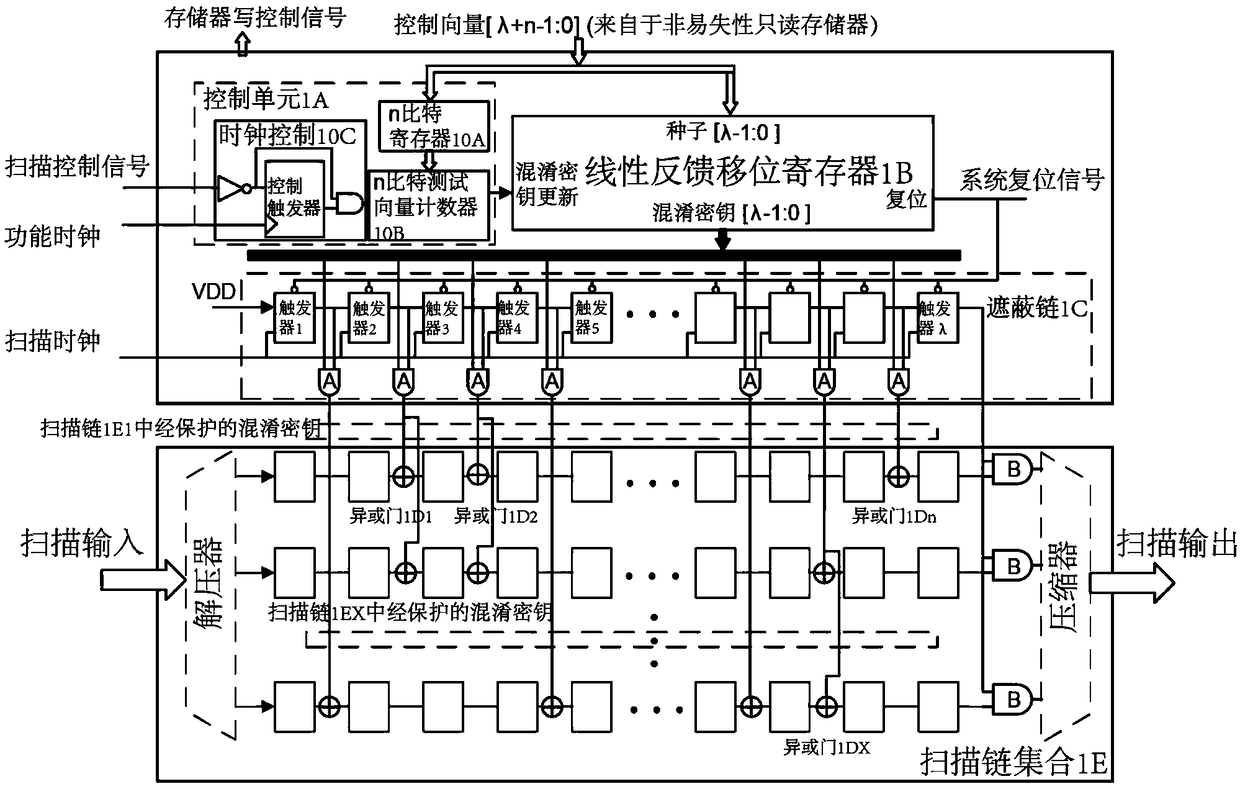

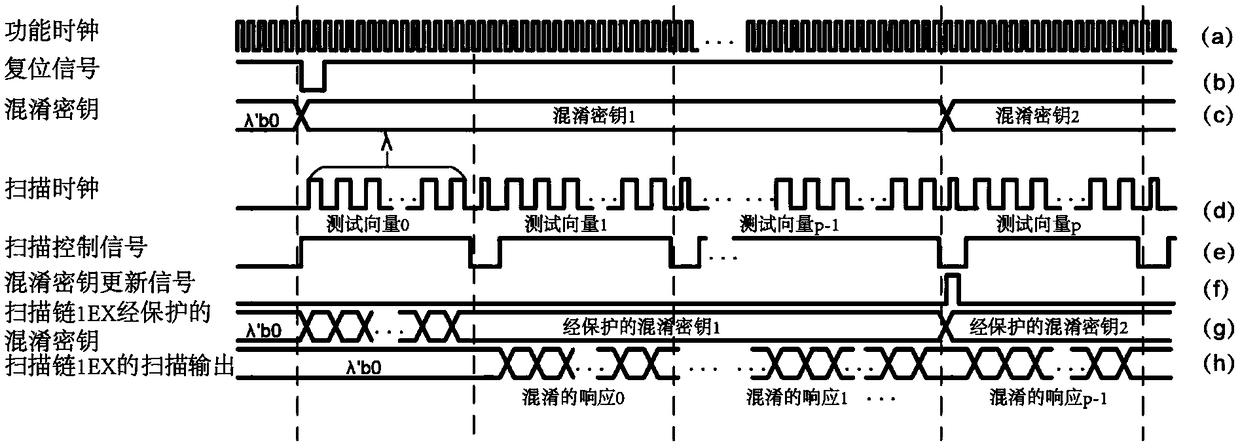

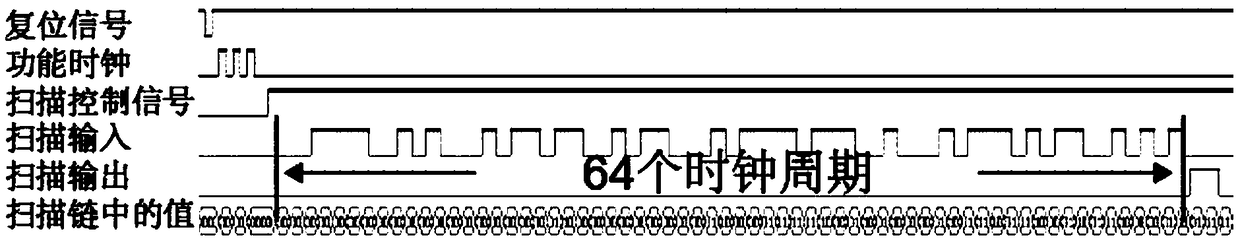

[0062] The IC chip dynamic confusion scan chain structure proposed by the present invention has been inserted into several test circuits, such as the FGU (Floating Point and Graphic Unit, floating-point calculation and image processing module) module in the OpenSPARCT2 processor, the largest in ITC'99 In the circuit b19, a 128-bit AES encryption module, and the Leonprocessor, Leon3s and VGA-LCD modules in the Gaisler chip, all the test circuits set the function clock to 100MHz and the scan clock to 10MHz during synthesis, and the scan chain The maximum length is 64 (that is, λ=64). It should be pointed out that since the number of scanning units in the integrated circuit chip is not necessarily an integer multiple of 64, the synthesis tool will automatically balance the length of each scanning chain so that the maximum length is 64. And the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More