Production method of three-dimensional ring gating semiconductor field effect transistor

A field-effect transistor and semiconductor technology, which is used in the manufacture of semiconductor/solid-state devices, semiconductor devices, electrical components, etc., to achieve the effect of suppressing corner effects, improving performance, and reducing time-consuming

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

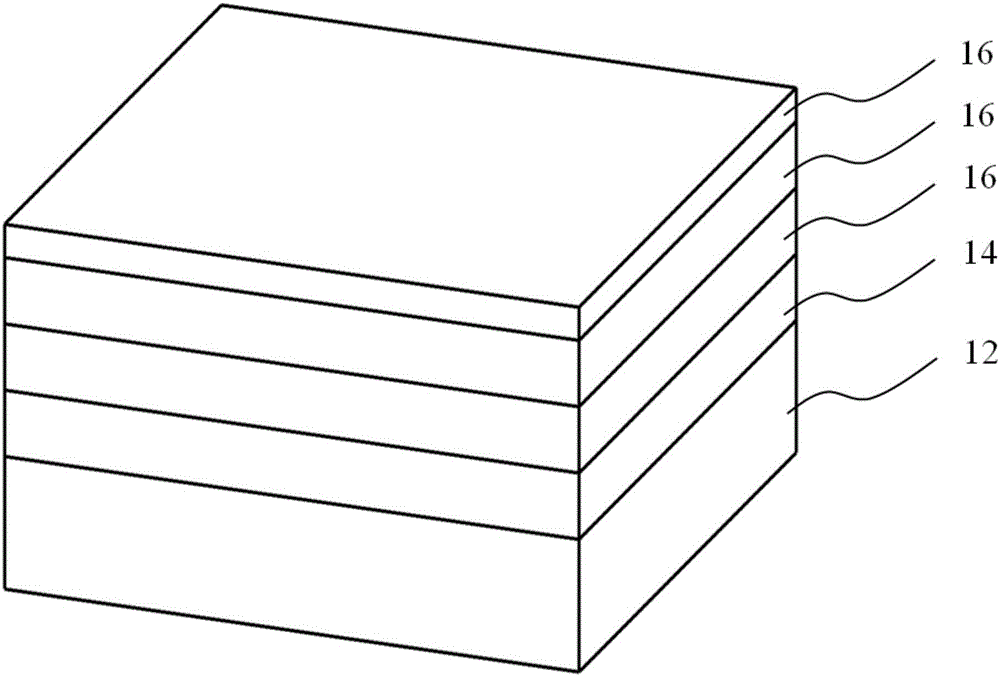

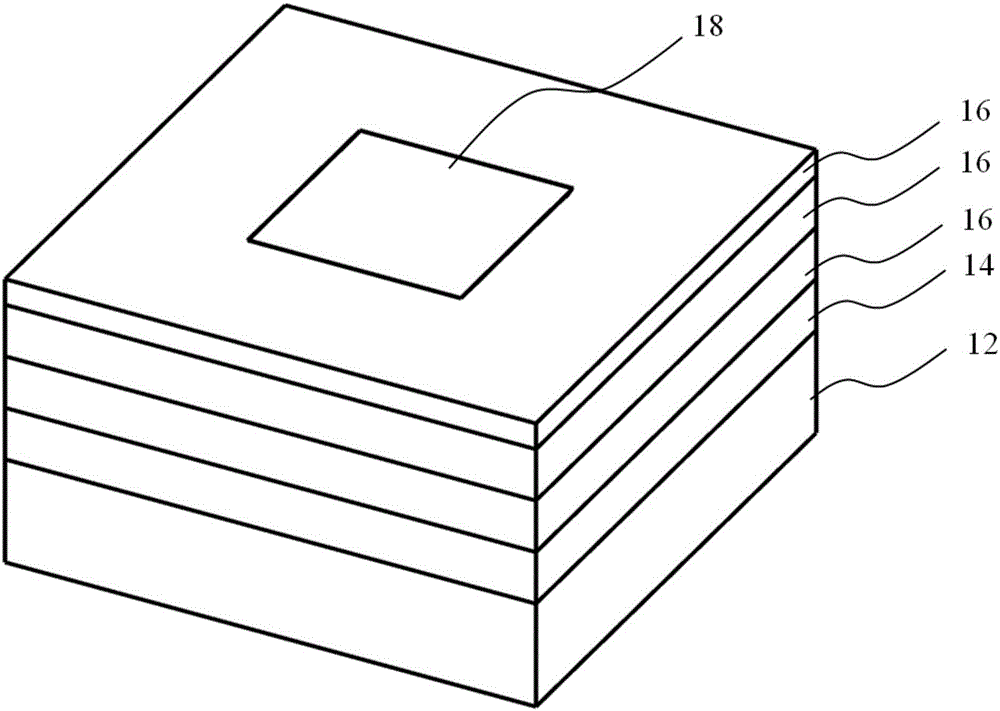

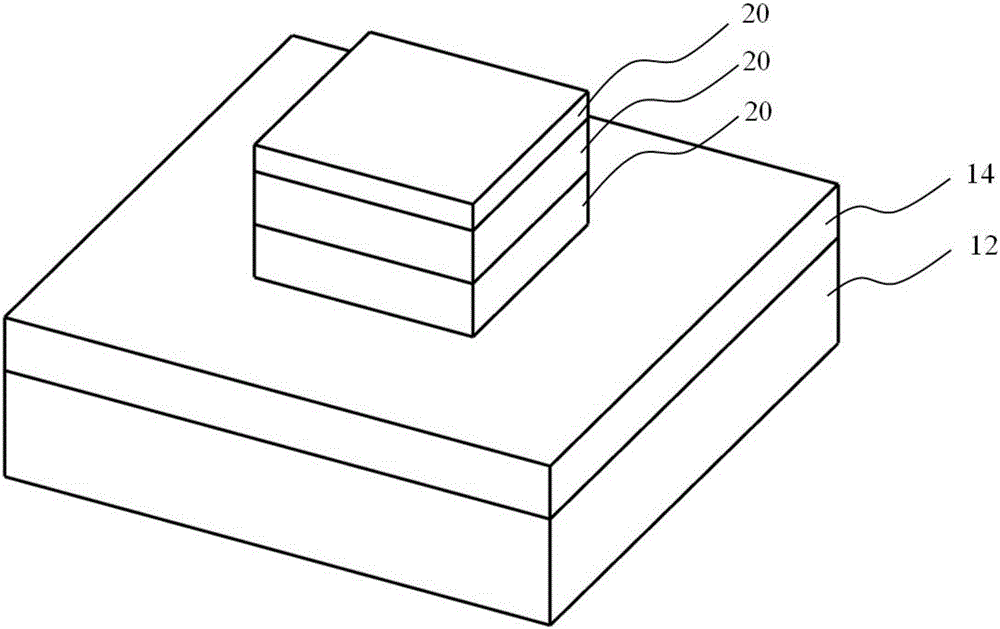

[0041] Figure 10 A schematic structural diagram of a three-dimensional gate-all-around semiconductor field effect transistor according to an embodiment of the present invention is shown. The preparation process specifically includes the preparation steps of the electrical insulation layer 14 and the functional structure layer 16 . figure 1 is a schematic diagram of preparing an electrical insulating layer 14 and a functional structural layer 16 on a substrate 12 according to an embodiment of the present invention. refer to figure 1, a silicon substrate can be selected as the supporting base 12 for the growth of the electrical insulating layer 14 and the functional structure layer 16 . The electrical insulating layer 14 can be selected from electrical insulating materials, such as silicon dioxide, undoped diamond, and the like. On the surface of the electrical insulation layer 14, one or more layers of functional structure layers 16 with different doping levels are grown. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More