Preparation method of semiconductor field effect transistor device with three-dimensional gate-all-around structure

A field-effect transistor, semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., to achieve the effect of improving performance, high flexibility, and suppressing corner effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

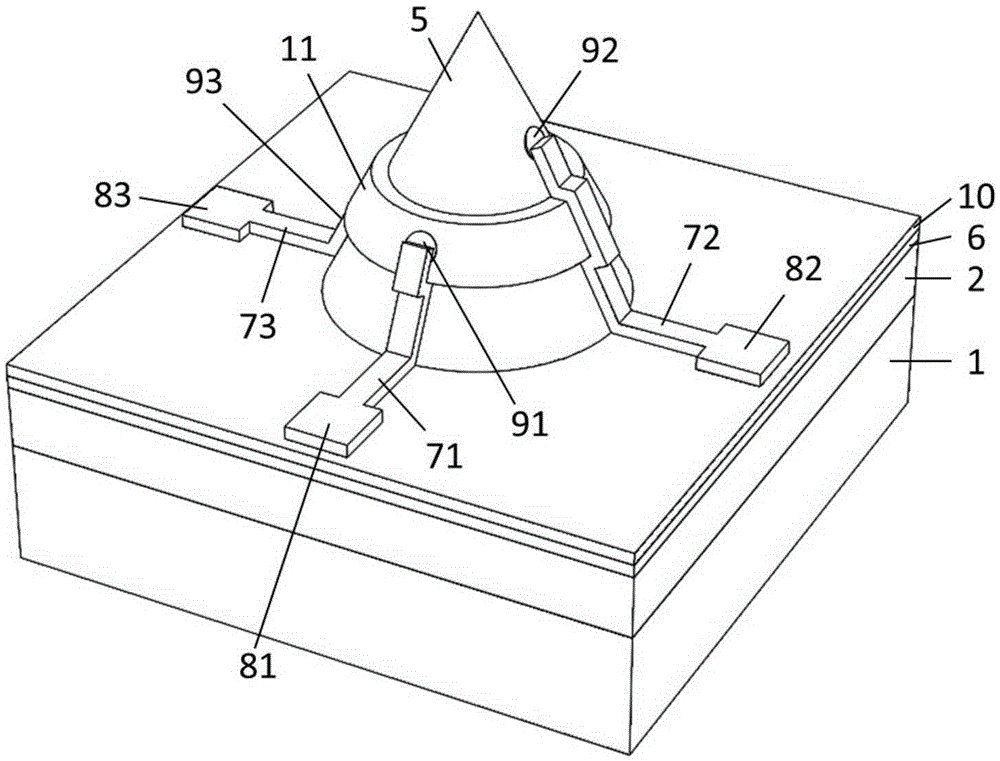

[0040] figure 1 A schematic structural diagram of a three-dimensional gate-around semiconductor field effect transistor device according to an embodiment of the present invention is shown. Its preparation process specifically comprises the following steps:

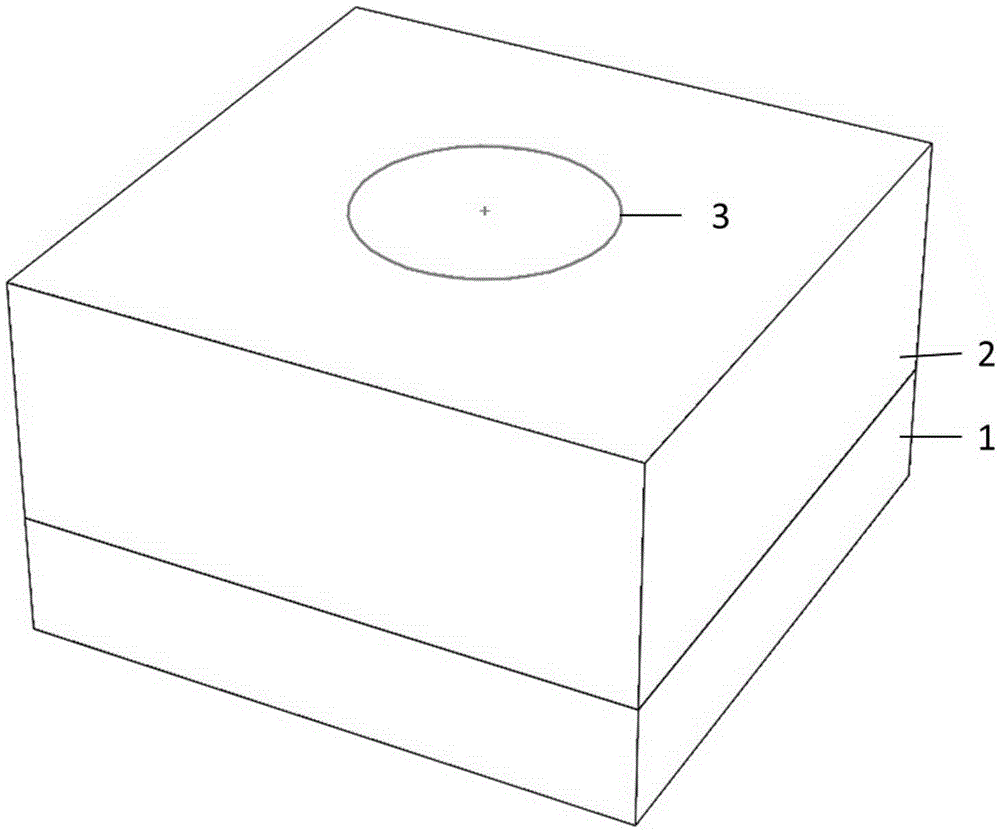

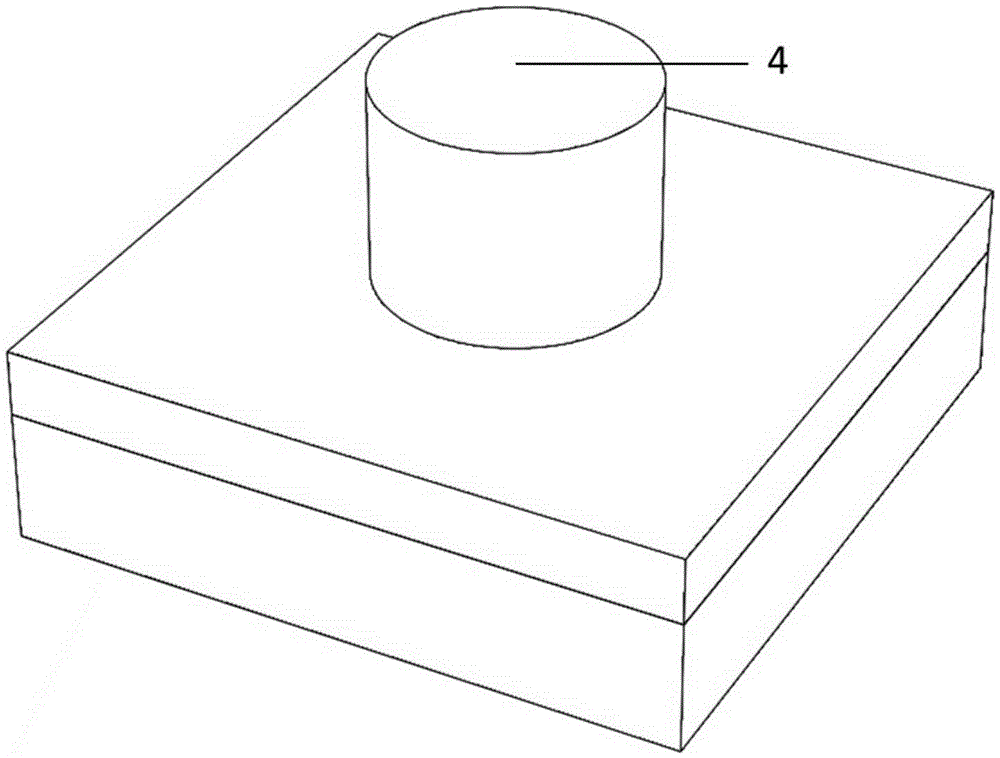

[0041] figure 2 It is a schematic diagram of the processing of the planar mask pattern according to an embodiment of the present invention, refer to figure 2 , firstly, the Si substrate 1 can be selected as the supporting substrate for the growth of the functional thin film layer, which is used for the preparation of the functional bulk material 2 on the substrate. The functional block material 2 can be selected from semiconductor materials, metal materials or electrical insulating materials. Among them, the Si substrate 1 needs to be cleaned and treated, specifically as follows: firstly, the Si substrate 1 is ultrasonically treated with acetone, ethanol, and deionized water; then the Si substrate 1 is dried with nitr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More