Jitter tolerance simulation verification method of clock data recovery circuit

A clock data recovery and jitter tolerance technology, which is applied in electrical digital data processing, CAD circuit design, special data processing applications, etc. The effect of reducing chip risk, implementing simplicity, and being easy to implement in engineering

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to make the method and advantages of the present invention clearer and easier to understand, the design scheme of the jitter tolerance simulation verification method provided by the present invention will be described in detail below, but this does not constitute a limitation to the present invention.

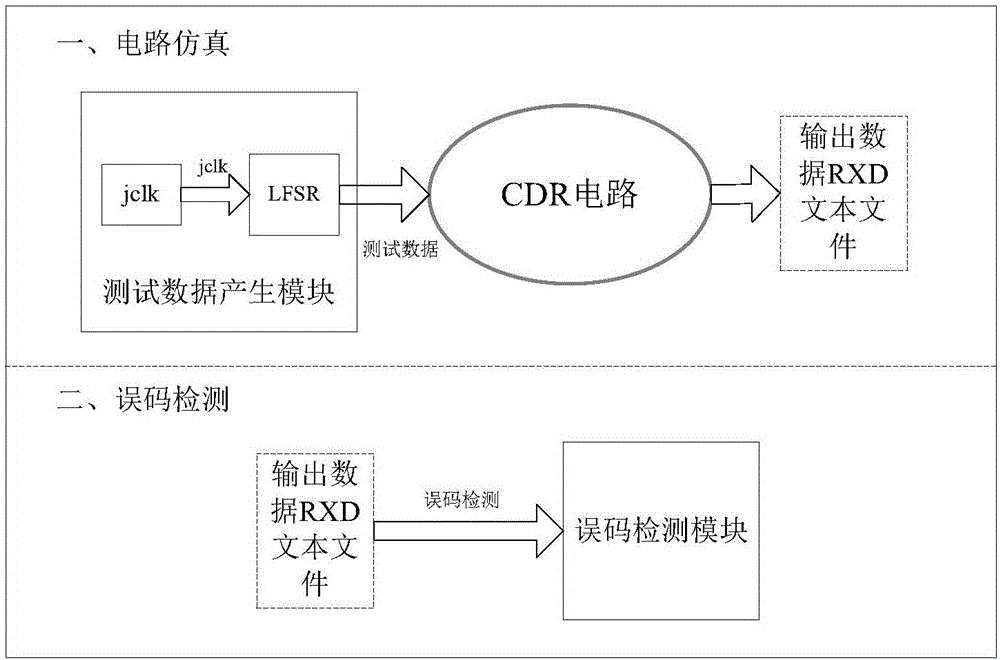

[0028] The present invention is a jitter tolerance simulation verification method of a clock data recovery circuit, and its specific implementation steps include:

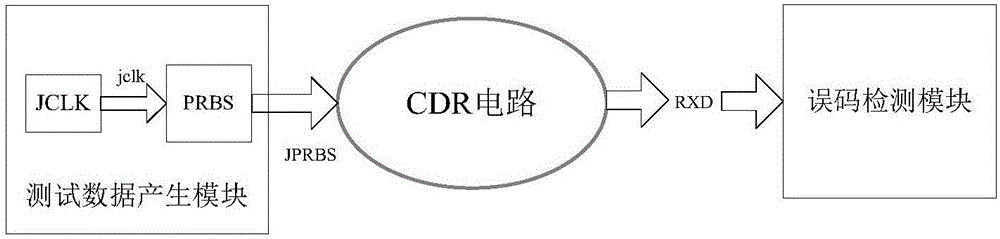

[0029] Phase 1: Verification module design for jitter tolerance.

[0030] Step1: Design the verification module of jitter tolerance. The verification module of jitter tolerance includes two parts: test data generation module and error detection module. The test data generation module is used to generate a low-voltage serial differential signal containing jitter information, including a jitter modulation clock JCLK and a pseudo-random code generation module PRBS. The jitter modulation clock is realiz...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More