Bare chip structure applied to testing and manufacturing method thereof

A manufacturing method and bare chip technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve the problem of high PCB processing accuracy and technical level requirements of bonding operators, and fixture development cycle It cannot meet the timeliness requirements of chip testing and the difficulty of effective connection, etc., and achieve the effect of good engineering application implementability, guaranteed reuse, and avoiding complicated steps and costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

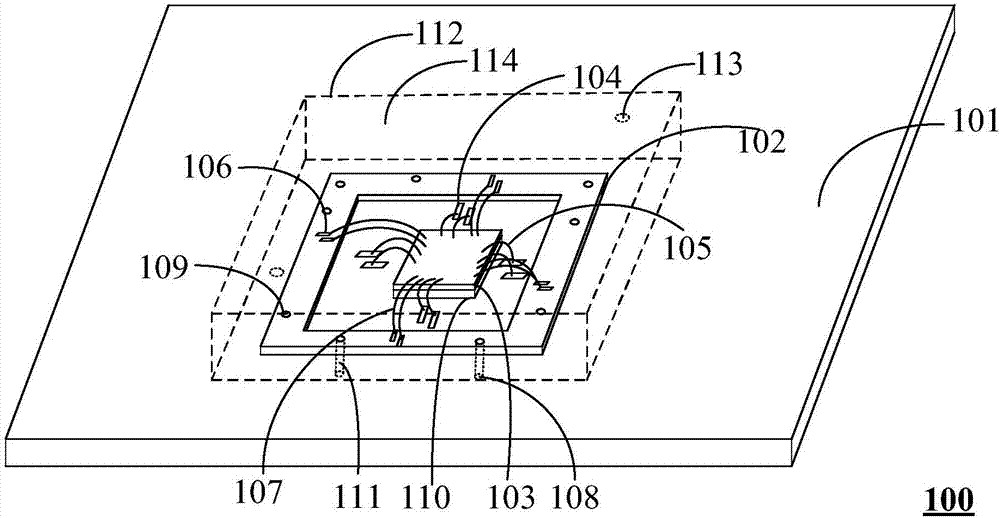

[0052] See figure 1 , figure 1 A schematic structural diagram of a bare chip structure applied to testing provided by an embodiment of the present invention, wherein the structure 100 includes: a main PCB board 101, a secondary PCB board 102, a bare chip 103, a first pad 104, a first key Aligning wire 105 , second pad 106 , second bonding wire 107 , pad 110 , metal pin header 111 , protective cover 112 and electrical insulating oil 114 .

[0053] Wherein, the pad 110 is bonded to the main PCB 101 and the bare chip 103 is bonded to the pad 110; the first solder pad 104 surrounds the bare chip 103 and is arranged On the main PCB 101 and connected to the metal PAD of the bare chip 103 through the first bonding wire 105; the secondary PCB 102 is located on the periphery of the first pad 104 and bonded to On the main PCB board 101 and realize electrical connection with the main PCB board 101 through the metal pin 111; the second pad 106 is arranged on the secondary PCB board 102 ...

Embodiment 2

[0073] See Figure 7 , Figure 7 It is a schematic flowchart of a method for manufacturing a bare chip structure applied to testing provided by an embodiment of the present invention. Wherein, the manufacturing method includes:

[0074] Making the main PCB board 101, and making the first pad 104 on the surface of the main PCB board 101;

[0075] Adhesive pads 110 at specified positions on the surface of the main PCB 101 and bond bare chips 103 on the surface of the pads 110;

[0076] Bonding both ends of the first bonding wire 105 to the metal PAD of the bare chip 103 and the first pad 104 using a bonding process;

[0077] Make the secondary PCB board 102, and make the second pad 106 on the surface of the secondary PCB board 102;

[0078] Bonding the secondary PCB board 102 on the main PCB board 101;

[0079] The two ends of the second bonding wire 107 are bonded to the metal PAD of the bare chip 103 and the second pad 106 using a bonding process, and the metal pin 111 is...

Embodiment 3

[0089] See Figure 8 , Figure 8 It is a schematic flowchart of another method for manufacturing a bare chip structure applied to testing provided by an embodiment of the present invention. Wherein, the manufacturing method includes:

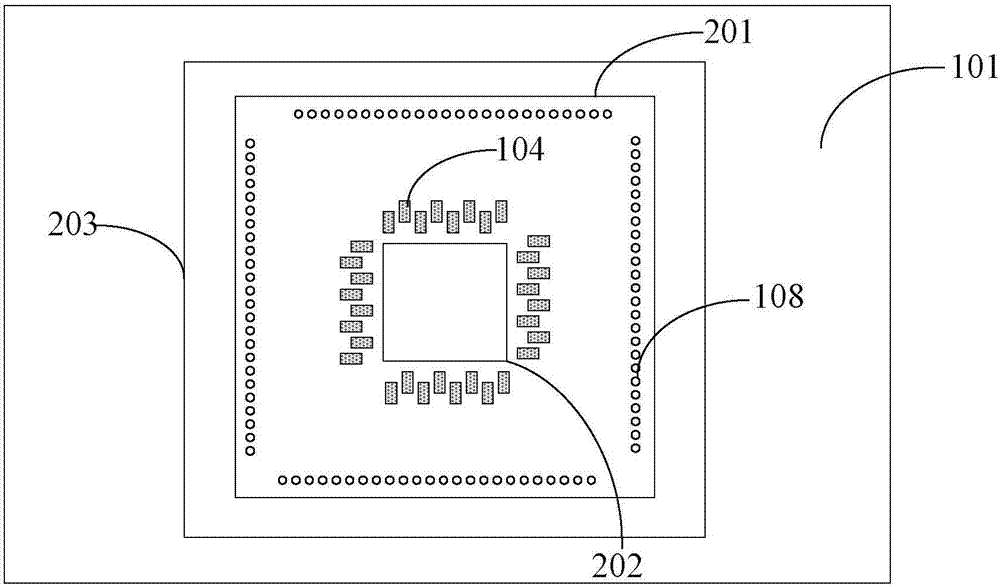

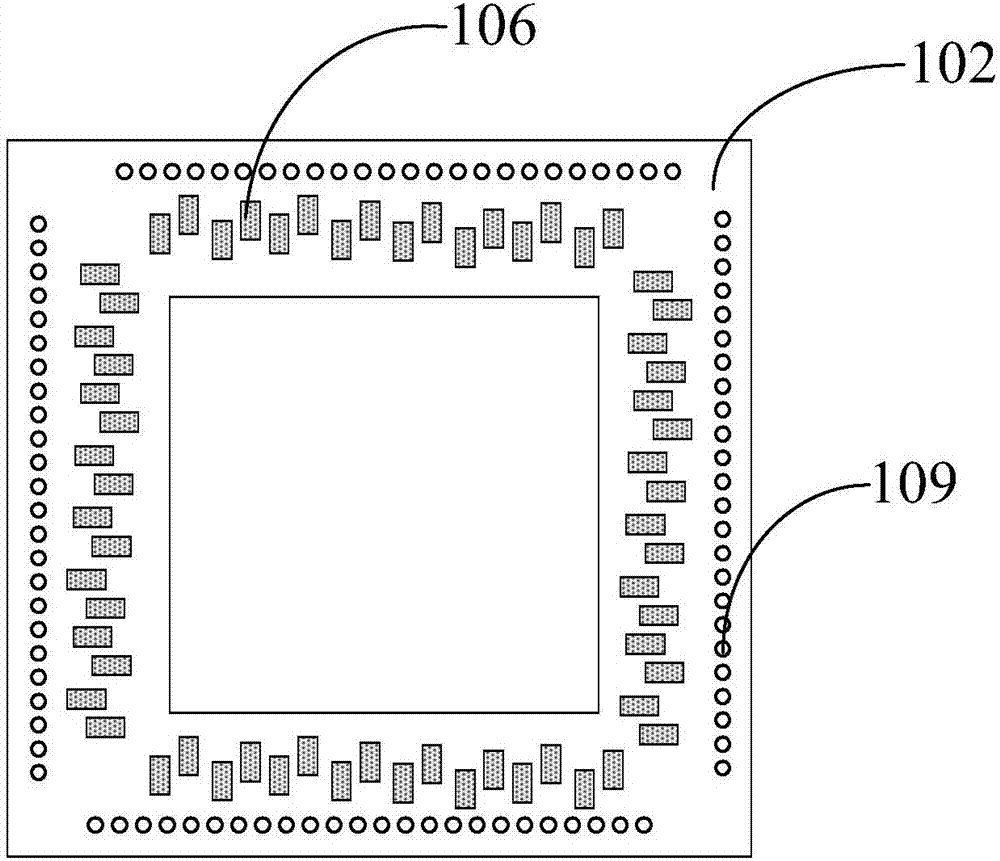

[0090] Select the main PCB board 101, and make the first boundary line 201 of the bonding secondary PCB board 102, the second boundary line 202 of the bonding gasket 110 and the third boundary line of the bonding protective cover 112 on the surface of the main PCB board 101 203; and on the surface of the main PCB 101 along the periphery of the second boundary line 202, make the first pads 104 in a staggered arrangement;

[0091] The gasket 110 is bonded on the surface of the main PCB 101 along the second boundary line 202 and the bare chip 103 is bonded on the surface of the gasket 110, and the first bonding wire 105 is used to connect all The metal PAD of the bare chip 103 and the first pad 104;

[0092] Select the secondary PCB board 102 t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More