Multifunctional special multiplier for hardware in FPGA and FPGA chip

A multiplier and multi-functional technology, which is applied in instruments, digital data processing components, and calculations using the number system.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments It is a part of embodiments of the present invention, but not all embodiments.

[0025] The invention provides a multifunctional hardware-specific multiplier in the FPGA, which can realize high-speed, high-performance multiplication operations, filter design, data comparison, especially the functions of multiplication and comparison of large-bit-width data.

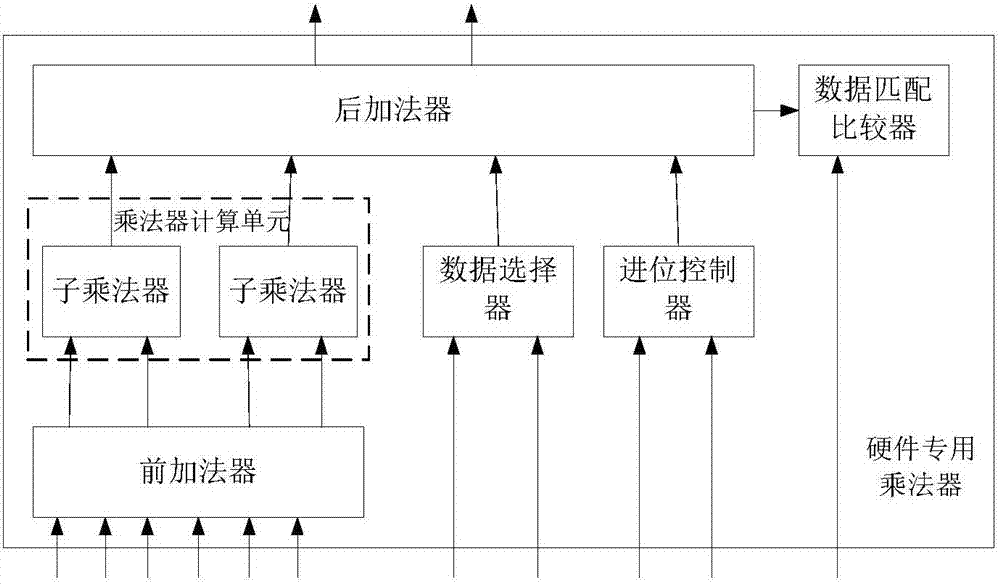

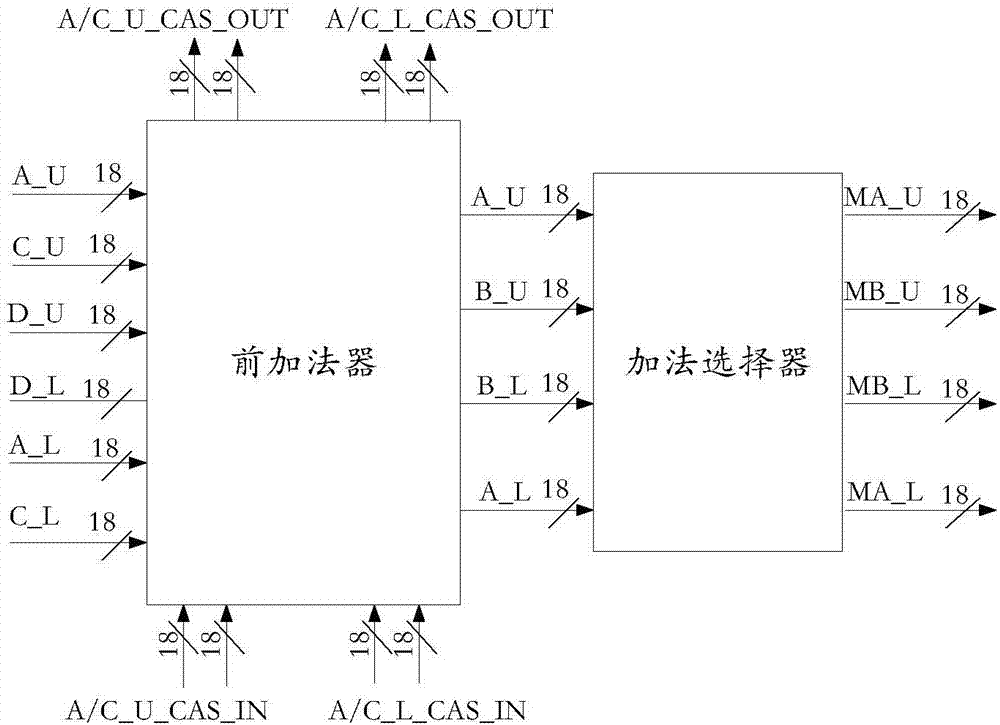

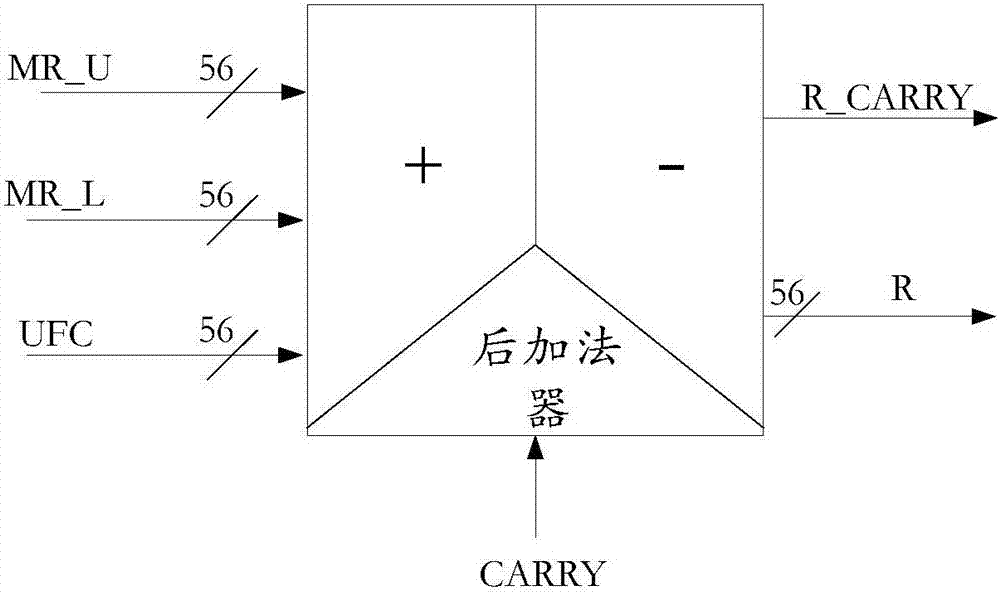

[0026] Below to figure 1 As an example, the embodiment of the present invention will be described. figure 1 A schematic diagram of a multifunctional hardware-specific multiplier in an FPGA provided by an embodiment of the present invention.

[0027] Such as figure 1 As s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More