Ultra-fast biasing temperature instability test system and method applied to semiconductor device

A technology of bias temperature and instability, which is applied in the direction of single semiconductor device testing, instrumentation, and electrical measurement. It can solve the problems of slow recovery effect and inability to accurately characterize the BTI characteristics of devices, so as to achieve accurate measurement and high test sensitivity. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The following introductions are some of the possible embodiments of the present invention, which are intended to provide a basic understanding of the present invention, and are not intended to identify key or decisive elements of the present invention or limit the scope of protection. It is easy to understand that, according to the technical solution of the present invention, those skilled in the art may propose other alternative implementation manners without changing the essence and spirit of the present invention. Therefore, the following specific embodiments and drawings are only exemplary descriptions of the technical solution of the present invention, and should not be regarded as the entirety of the present invention or as a limitation or limitation on the technical solution of the present invention.

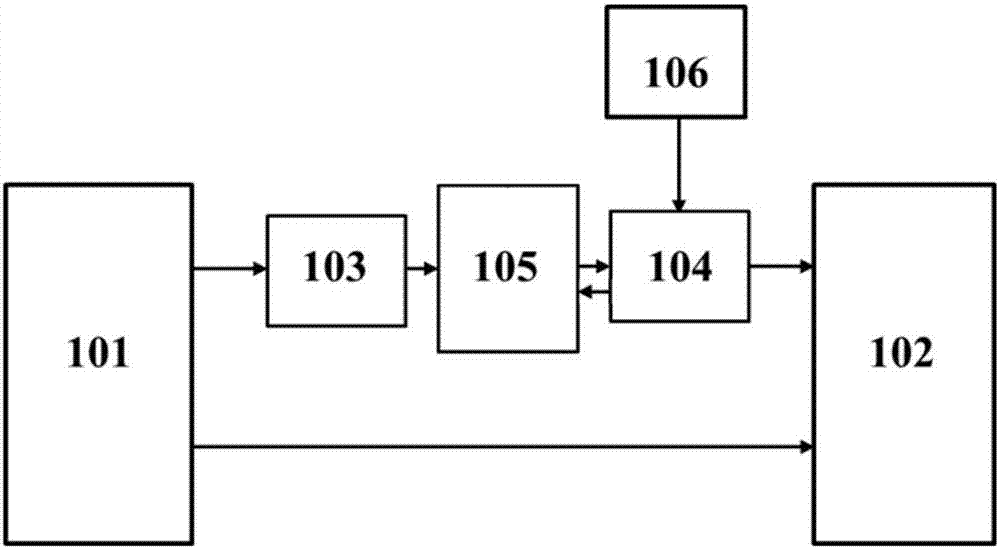

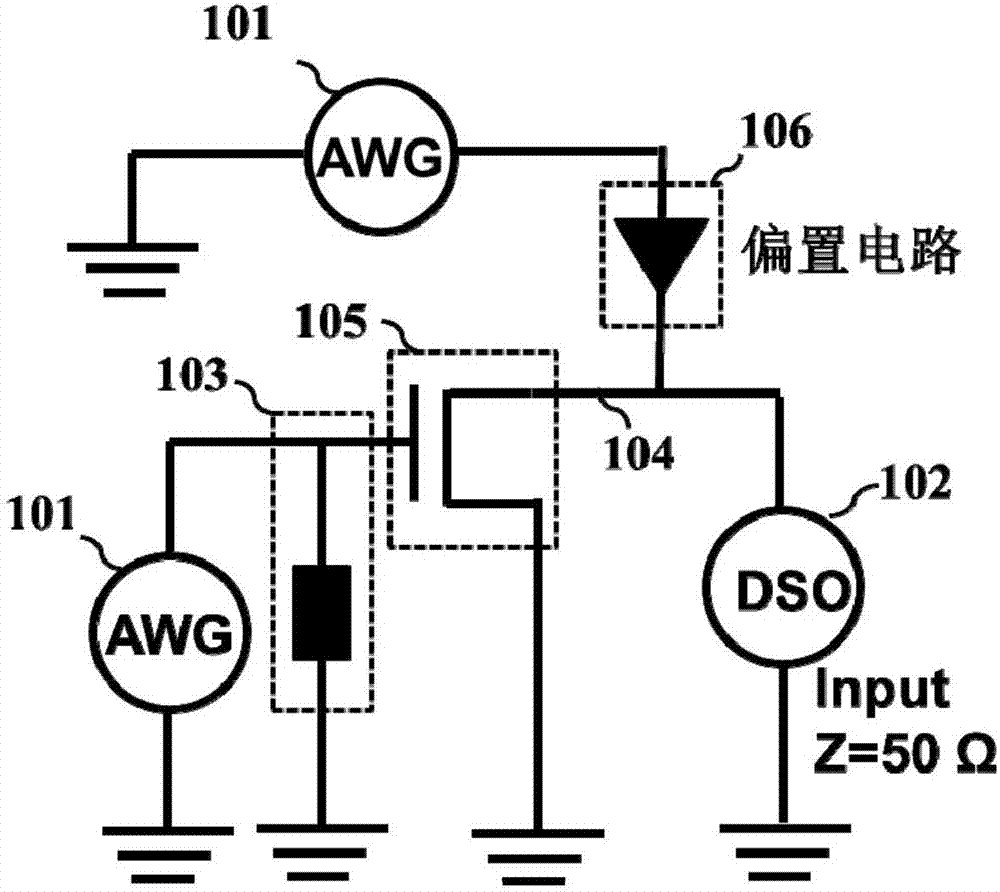

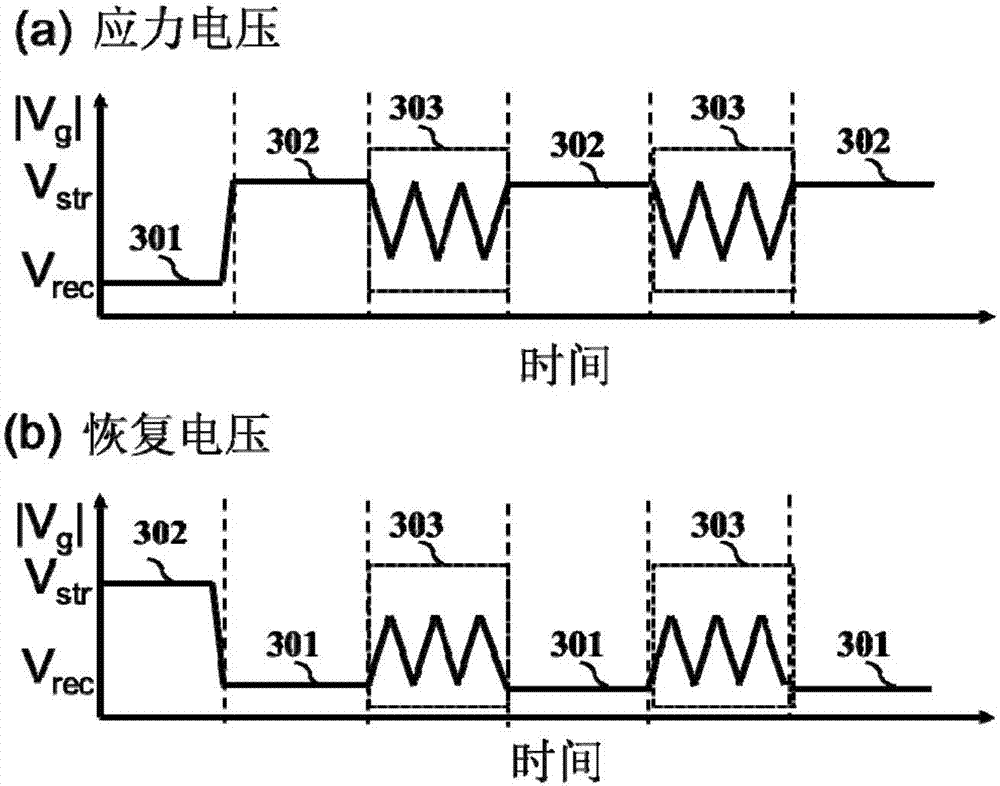

[0025] Such as figure 1 As shown, an ultra-fast bias temperature instability test system applied to semiconductor devices includes an arbitrary waveform generator ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More