Metal layer of compound semiconductor and preparation method thereof

A metal layer and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as residue on the bottom of the photoresist, metal wire falling off, reliability failure, etc., to avoid peeling off, increase gas Tightness, improve the effect of reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

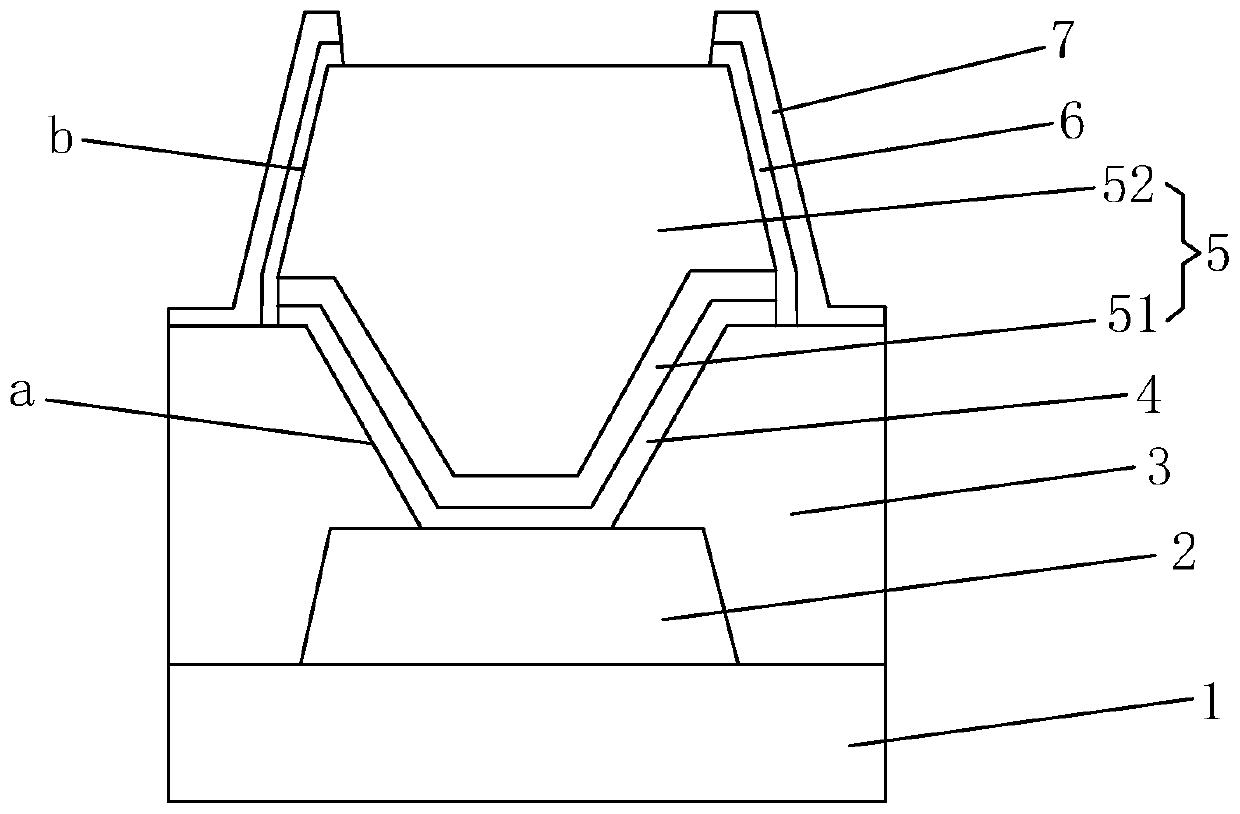

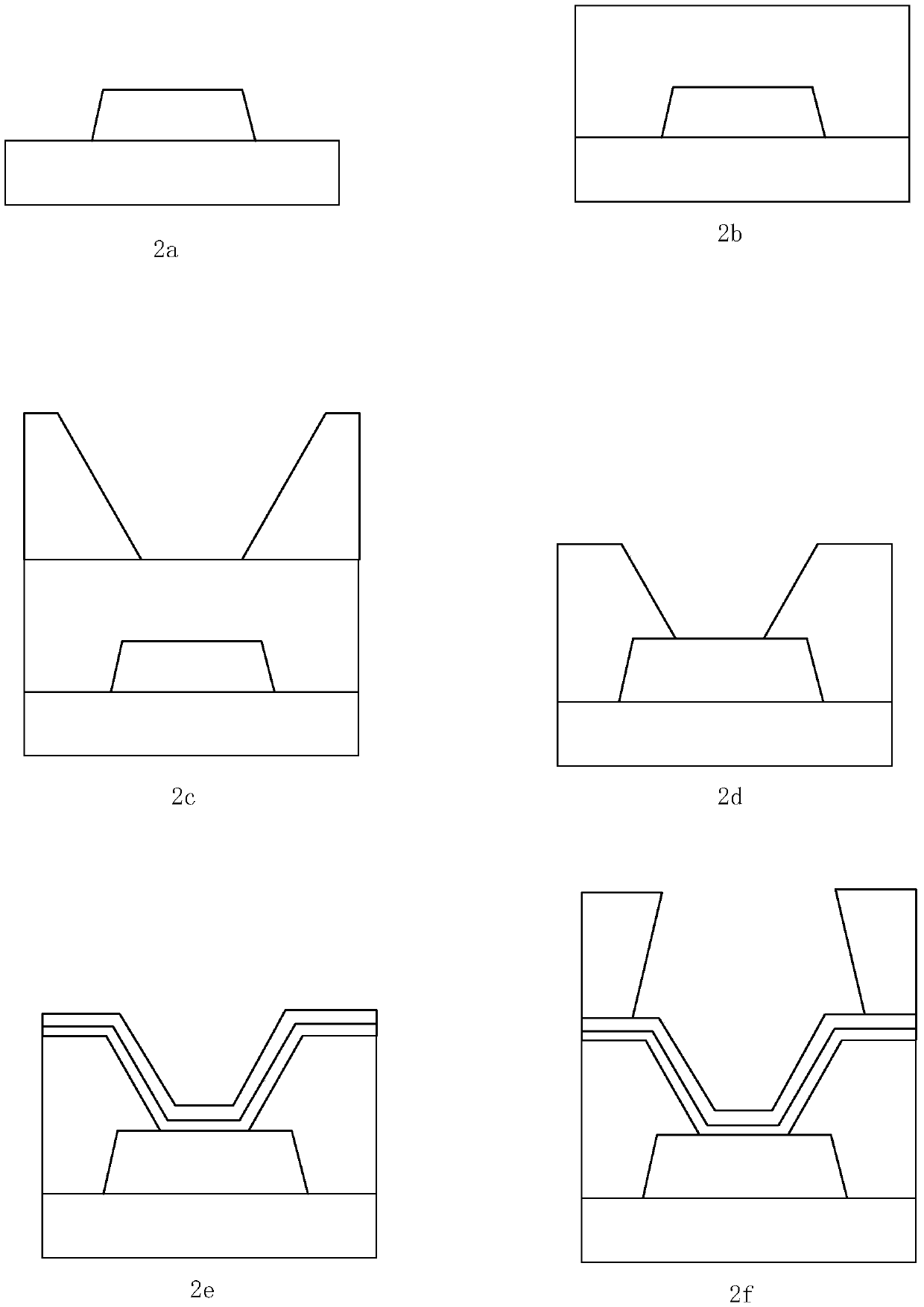

[0034] refer to figure 1 A compound semiconductor metal layer structure includes a first metal layer 2 , an insulating layer 3 , a TiW layer 4 , a second metal layer 5 , a Ti layer 6 and a protective layer 7 disposed on a compound semiconductor wafer 1 . The first metal layer 2 is arranged on the compound semiconductor wafer 1, and the insulating layer 3 covers the first metal layer 2 and the surface of the compound semiconductor wafer 1. The insulating layer 3 is provided with an opening above the first metal layer 2, and the two sides of the opening are directed toward Inward slope 45° to 75°. The TiW layer 4 covers the bottom and sidewalls of the opening 31 and extends to the top surface of the surrounding insulating layer 3 . The second metal layer 5 is formed on the TiW layer 4, fills up the opening and protrudes above the opening, wherein the two sides b of the protruding part are inclined outward by 75° to 85°; the Ti layer 6 covers the TiW layer 4 The sidewall and th...

Embodiment 2

[0058] In Example 1 of figure 2 After the structure of k, repeat figure 2 b to figure 2 The step of k to form the third, fourth and above metal layers on the second metal layer, and then return to figure 2 l step, thereby forming a laminated structure of multiple metal layers.

Embodiment 3

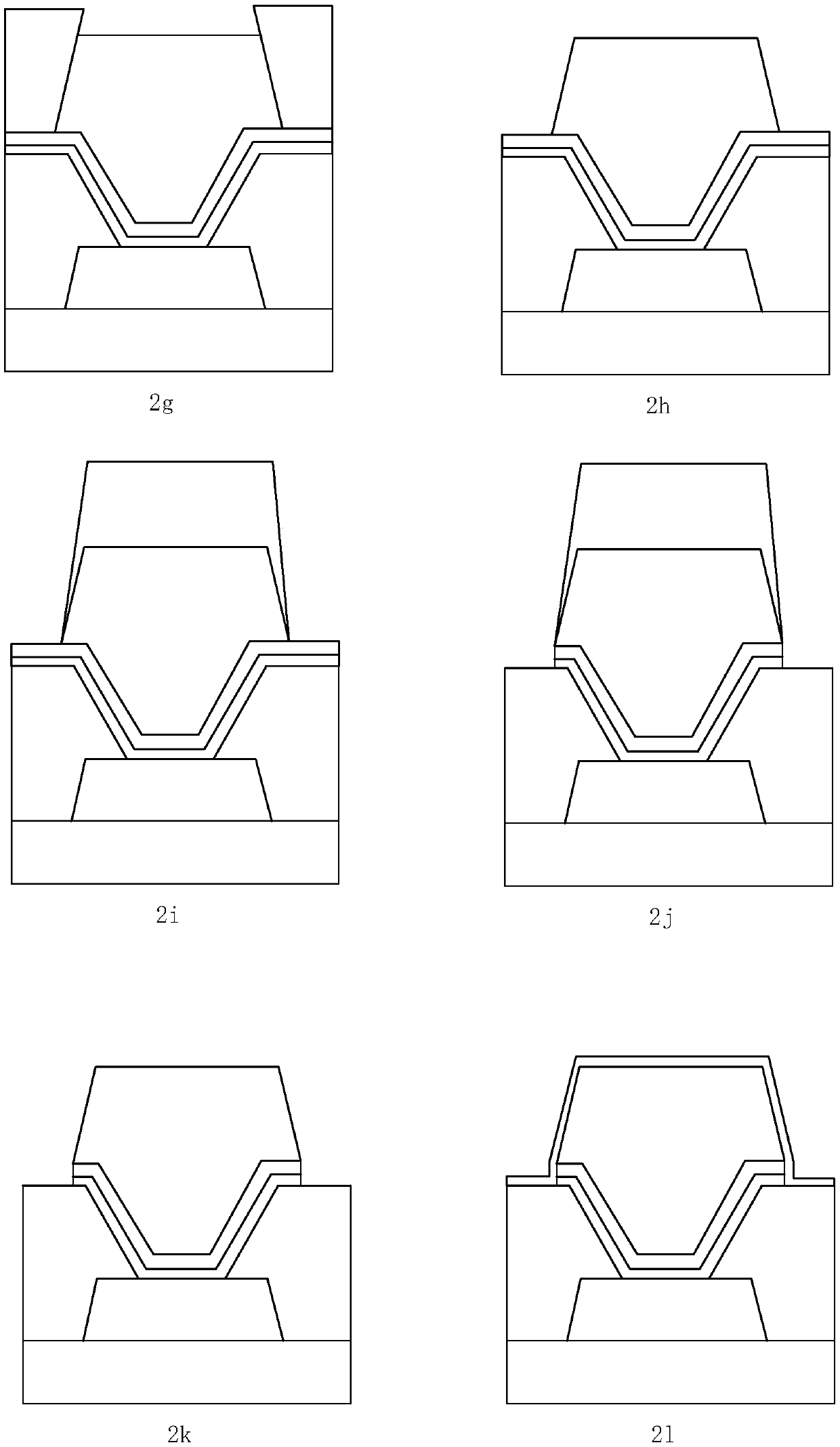

[0060] refer to image 3 , another compound semiconductor metal layer structure, which is different from Embodiment 1 in that it also includes a dielectric layer 8, the dielectric layer 8 covers the first metal layer 2 and the surface of the wafer 1, and the insulating layer 3 is set on the dielectric layer 8. The dielectric layer can be SiN with a thickness of 0.05-0.5 μm, and refer to Example 1 for other structures. This structure is applied to capacitance. Correspondingly, its preparation method is in figure 2 a and figure 2 Add a step between b: deposit an upper dielectric layer on the first metal layer by means of PECVD, and then form an insulating layer.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More