Comb-shaped micro-sensor for measuring strong magnetic field, and preparation method for comb-shaped micro-sensor

A micro-sensor, comb-shaped technology, applied in the field of micro-sensors, can solve the problems of large temperature dependence, lower sensor quality factor, unsuitable for Tokamak high temperature, strong radiation environment, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0054] A comb-tooth microsensor for measuring a strong magnetic field comprises a substrate, a sensor body and a cover connected in sequence.

[0055] The substrate is a single-sided polished wafer 1 with a thickness of 500 um, wherein a cavity with a depth of 1 um is etched by a deep reactive ion etching technique on the polished side, and a lift-off technique is used to grow the entire polished surface provided with a cavity The first silicon oxide layer 2 .

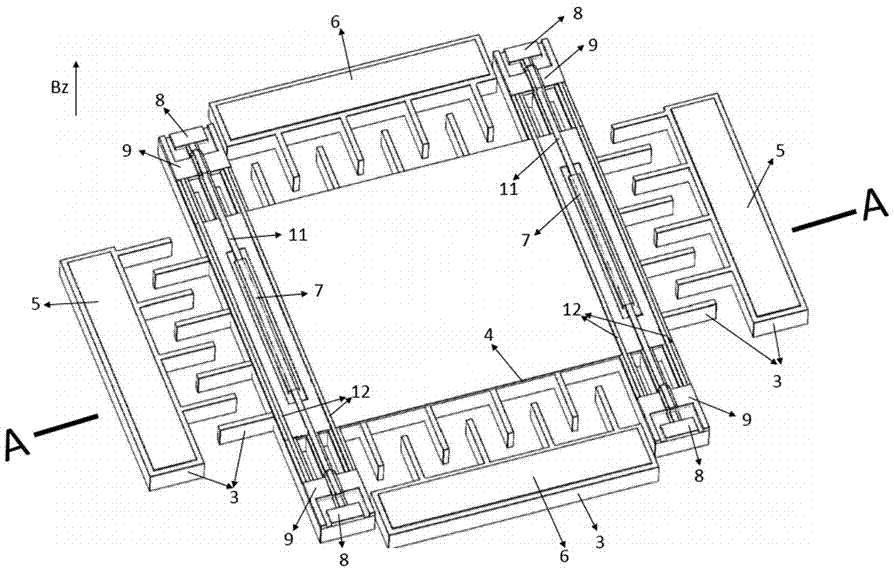

[0056] see figure 1 , the sensor body includes an SOI wafer, the SOI wafer is divided into a main body, a pair of measuring electrode bodies and a pair of driving electrode bodies, a pair of measuring electrode bodies are located on both sides of the main body in the X direction, and a pair of driving electrode bodies are located on the Y side of the main body The two sides of the direction; a pair of measuring electrode bodies and the main body have a tooth-shaped interlaced fit structure, and a pair of driving elect...

Embodiment 2

[0069] The steps of preparing a comb-shaped microsensor for high magnetic field measurement are as follows:

[0070] (1). See Figure 4On the polished side of a 500um thick single-sided polished wafer 1, a 1um deep cavity was etched by deep reactive ion etching technology, and the first oxide was grown by lift-off technique on the entire polished surface provided with the cavity. Silicon layer 2.

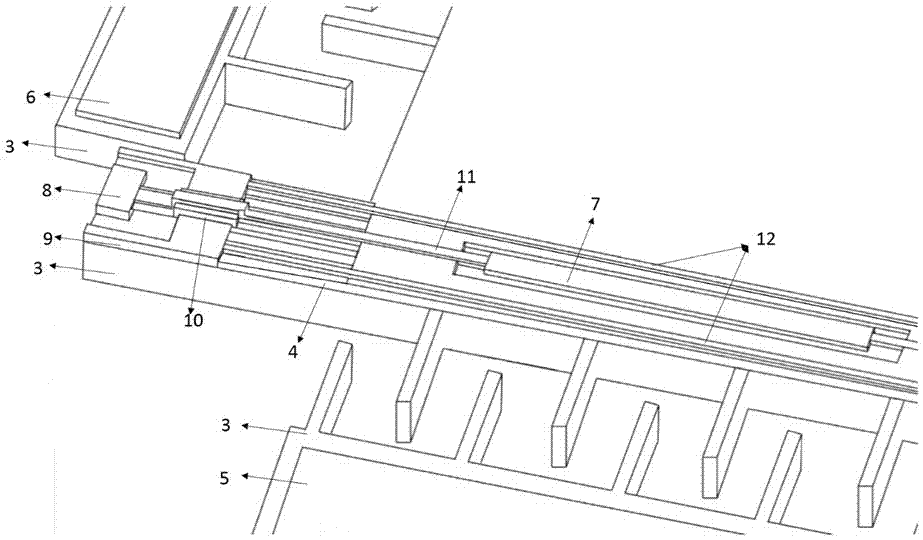

[0071] (2). See Figure 5 , at a temperature of 200° C., the 20um thick silicon material layer 3 of the SOI wafer is directly bonded to the first silicon oxide layer 2 of the single-side polished wafer 1 .

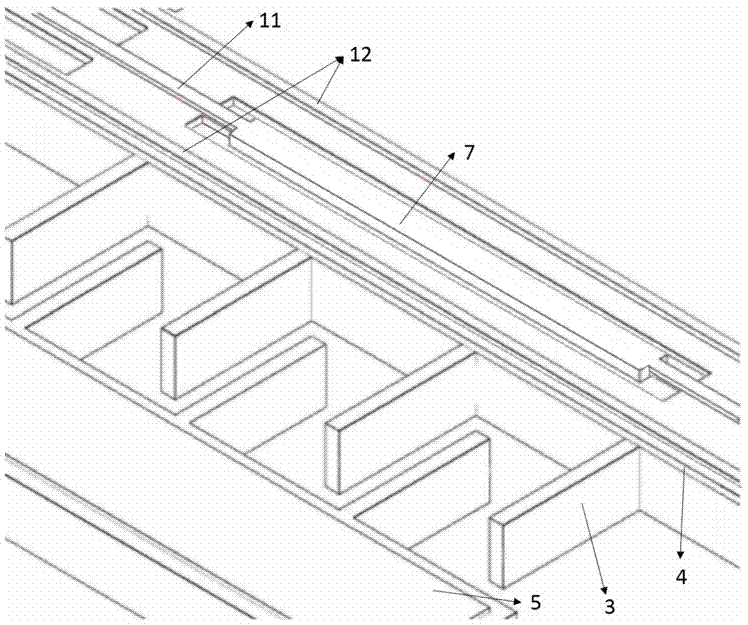

[0072] (3). See Image 6 , using deep reactive ion etching to remove the 380um silicon layer 16 on the SOI wafer, and patterning the exposed 1um silicon oxide layer 4 to be etched and removed, and the patterned part exposes a 20um thick silicon material layer 3 , the part of the unpatterned 1um thick silicon oxide layer 4 is in a raised state.

[0073] (4). See Figure 7 A...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More