SoC (System on a Chip) chip resetting method and resetting system

A reset method and chip technology, applied in the field of power transmission, can solve problems such as poor reset reliability of SoC chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

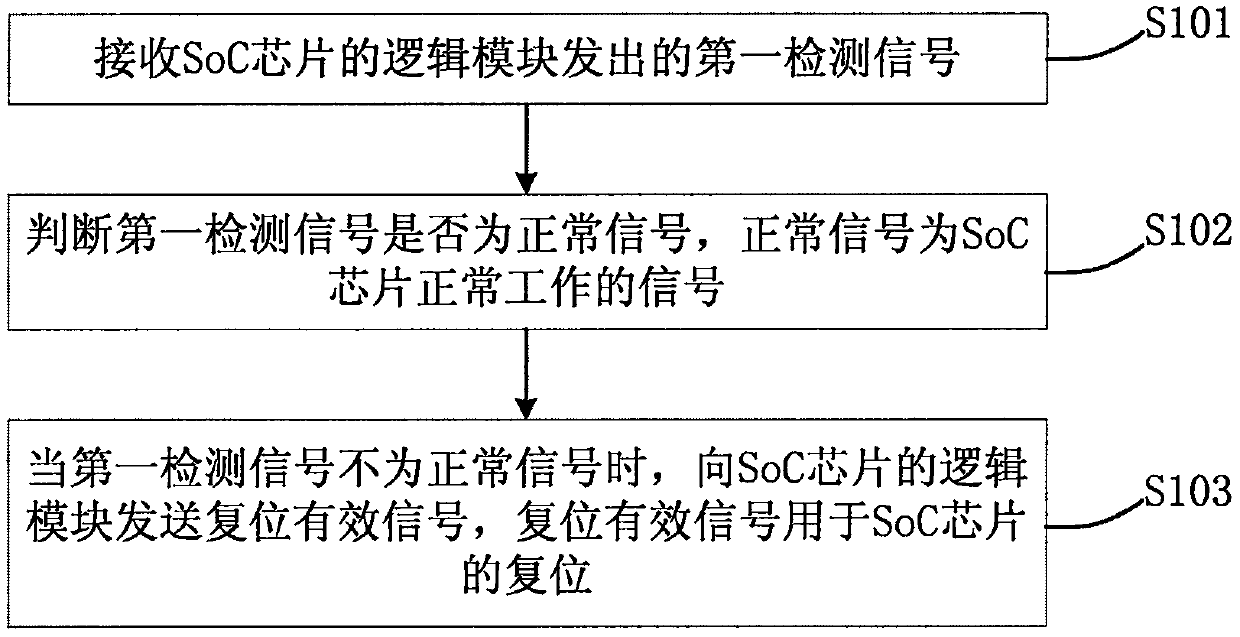

Embodiment 1

[0036] This embodiment provides a SoC chip reset method, which has strong anti-interference ability and high reset reliability. The normal operation of the module and even the DC transmission system plays a vital role. As the core control part of the SMC, the SoC (System on Chip) chip is normally and reliably reset in the strong electromagnetic field environment of the flexible DC transmission converter valve hall. Particularly important.

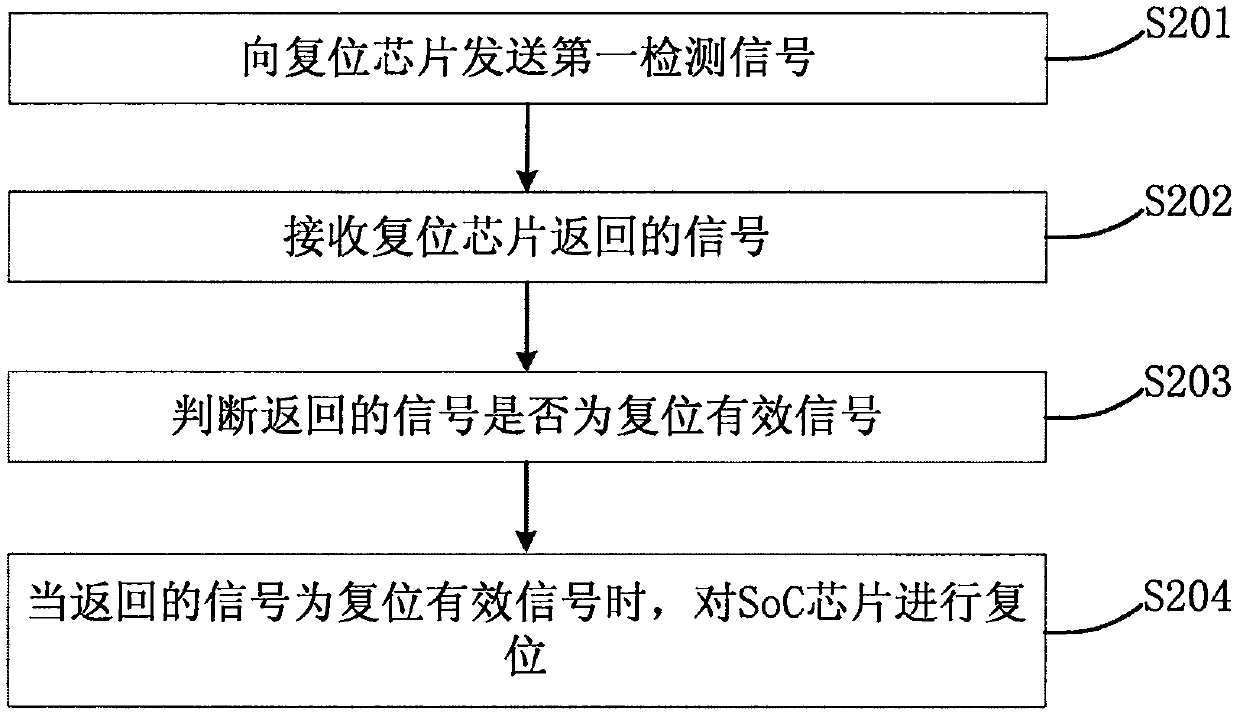

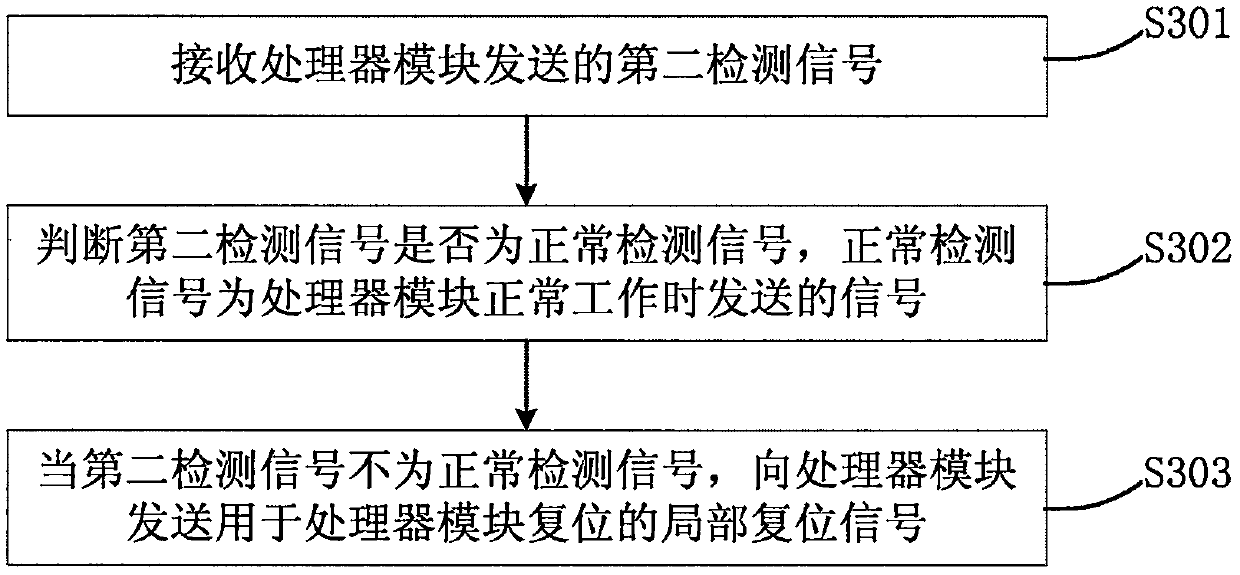

[0037] The SoC chip includes a logic module and a processor module. In this embodiment, the logic module is an FPGA module, and the processor module is an ARM processor module. The FPGA module and the ARM processor module constitute the SOC chip. In order to reset the SOC chip, avoiding ARM's poor anti-interference ability in a strong electromagnetic field environment, there may be problems such as crashes, which will cause the chip to fail to reset normally and endanger the normal operation of the sub-module. In this embodiment, a reset ch...

Embodiment 2

[0060] This embodiment provides a SoC chip reset system, which is used to implement the embodiment and preferred implementation mode in Embodiment 1, and what has been explained will not be repeated. As used below, the term "module" may be a combination of software and / or hardware that realizes a predetermined function. Although the systems described in the following embodiments are preferably implemented in software, implementations in hardware, or a combination of software and hardware are also possible and contemplated.

[0061] Figure 5 It is a system block diagram of the SoC chip reset system according to the embodiment of the present invention, which is applied to the reset chip, and the reset chip is connected to the SoC chip. The SoC chip includes a logic module and a processor module. In this embodiment, the logic module is an FPGA module. The processor module is an ARM module, and the first detection signal includes a square wave signal sent by the FPGA module. The...

Embodiment 3

[0070] The embodiment of the present invention also provides a computer-readable storage medium, on which computer-executable instructions are stored, and the computer-executable instructions can execute any of the logic modules used in the SoC chip in the first embodiment above. SoC chip reset method. Wherein, the storage medium can be a magnetic disk, an optical disk, a read only memory (Read Only Memory, ROM), a random access memory (Random Access Memory, RAM), a flash memory (FlashMemory), a hard disk (Hard Disk Drive, Abbreviation: HDD) or solid state disk (Solid State Drive, SSD), etc.; the storage medium may also include a combination of the above types of storage.

[0071] This embodiment also provides a reset chip, which can be combined with Figure 5 The described system is used to realize a kind of SoC chip reset method, promptly is used to realize such as figure 1 The SoC chip reset method in the embodiment.

[0072] see Figure 8 , Figure 8 It is a schematic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More