Semiconductor die package and method of producing the package

A semiconductor tube and die technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of not allowing independent packaging and simple testing of logic dies, and reduce the overall package size. and the effect of interconnect length, cost reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

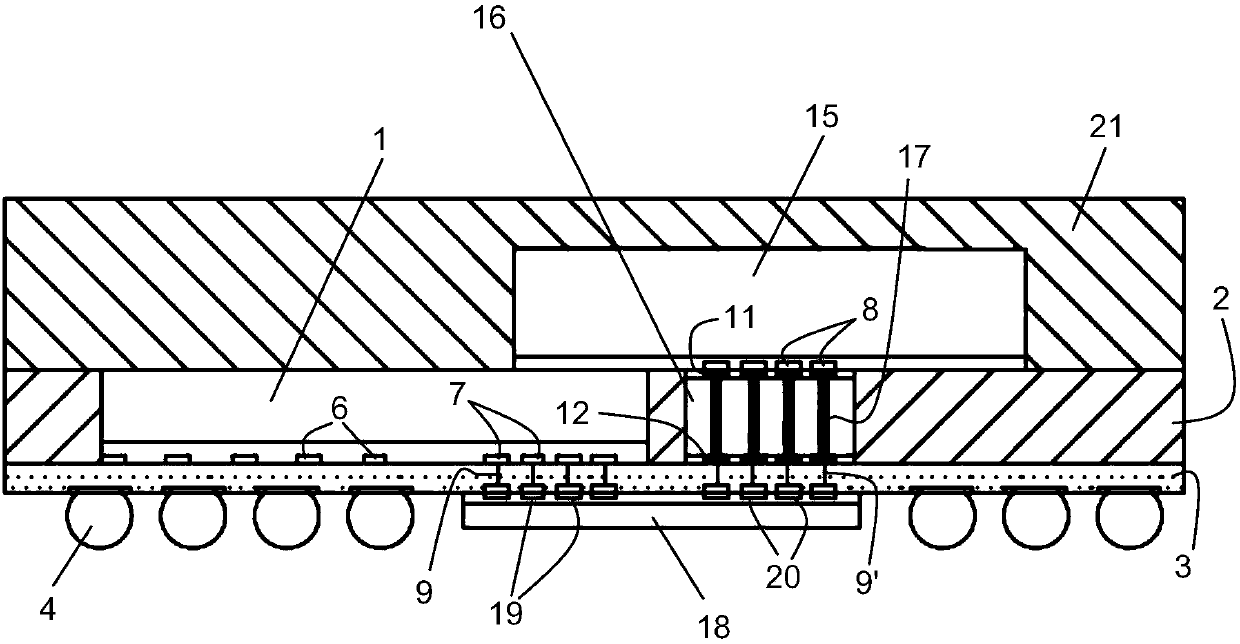

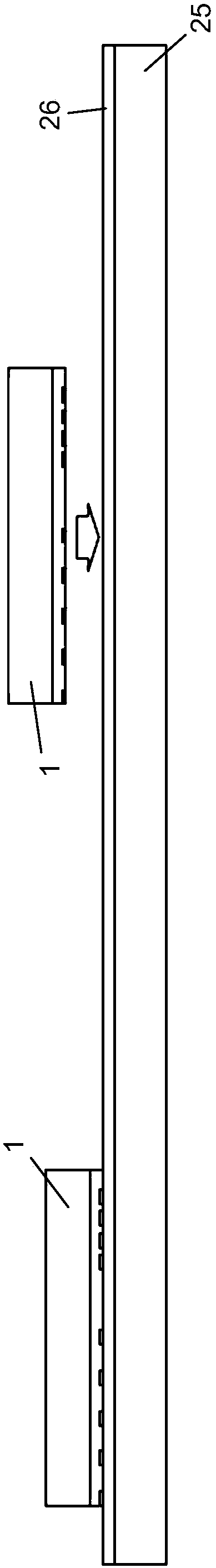

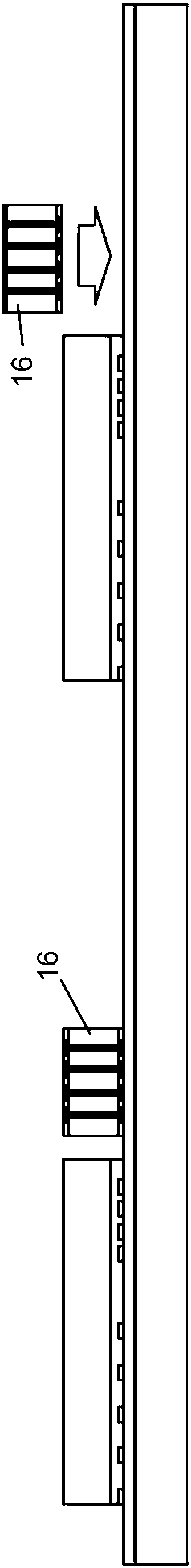

[0033] figure 1 The package shown includes logic die 1 and memory die 15 with interconnected I / O contact arrays 7 / 8. For example, memory die 15 may be a DRAM die configured according to a wide I / O standard. Both contact arrays 7 and 8 are in this case configured according to this standard, ie each array comprises 4 groups of 6x73 contact pads with a pitch of 40 μm. However, the invention is not limited to such devices, and figure 1The embodiments are to be understood as merely exemplifying typical fields of application of the invention. The logic die 1 is embedded in a substrate 2 formed of a mold material and comprises a redistribution layer (RDL) 3 on the front side of the substrate. Package-level solder balls 4 are mounted on contact pads 5 provided on the surface of the RDL 3 for establishing connections to the front side of the logic die 1 by circuitry (not shown) contained in the RDL 3. on the contact terminal 6 provided on the connection. The front side of the logi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com