Top gate self-alignment metal oxide semiconductor TFT and manufacturing method therefor

A technology of oxide semiconductor and fabrication method, applied in semiconductor/solid-state device manufacturing, semiconductor device, transistor and other directions, can solve the problems of unstable TFT operation, easy to be affected by voltage on other charged structure layers, etc., and achieve good working stability performance, improve working stability, and avoid the effect of floating gate effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] In order to further illustrate the technical means adopted by the present invention and its effects, the following describes in detail in conjunction with preferred embodiments of the present invention and accompanying drawings.

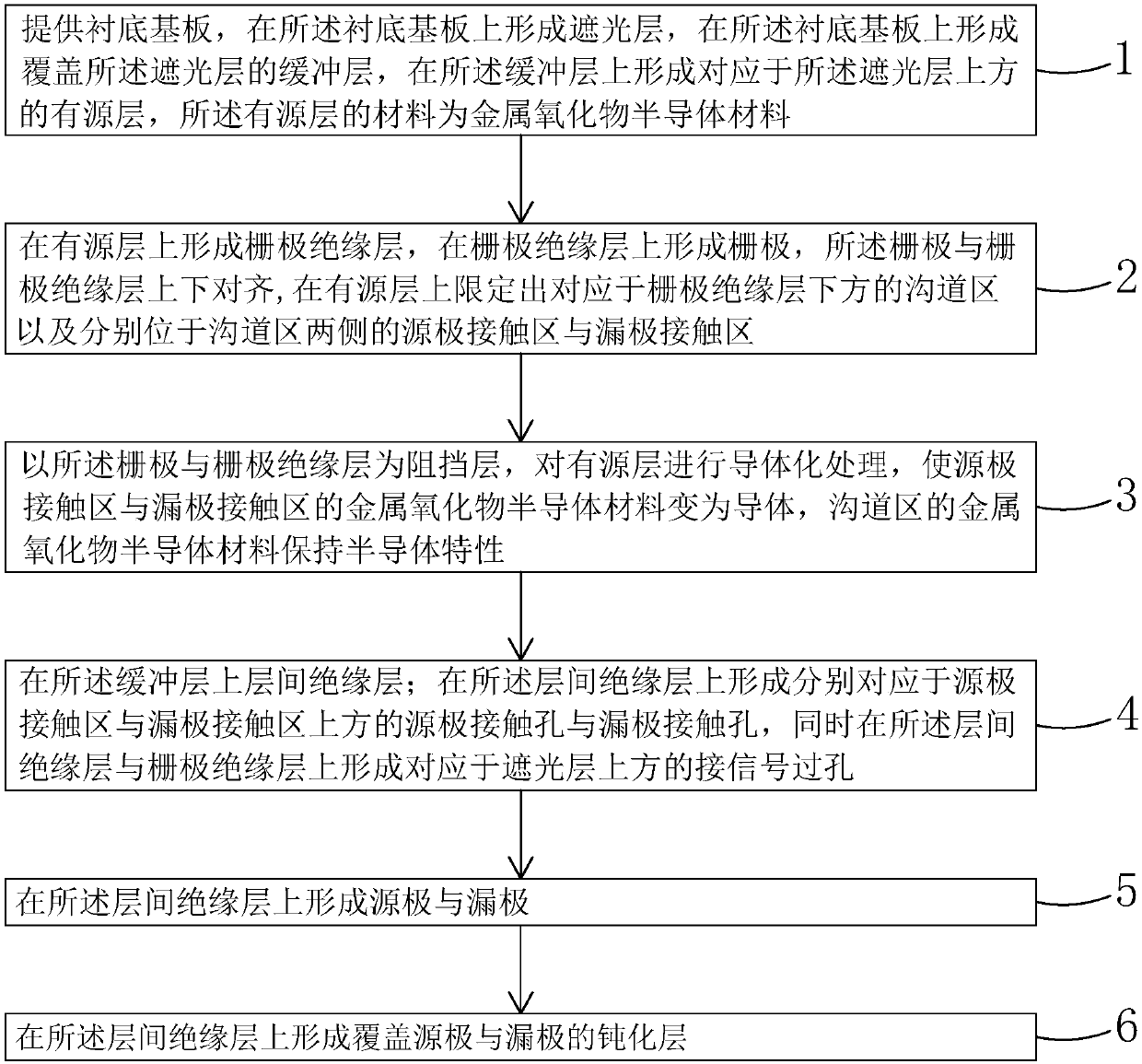

[0044] see figure 1 , the invention provides a method for fabricating a top-gate self-aligned metal-oxide-semiconductor TFT, comprising the following steps:

[0045] Step 1, such as figure 2 As shown, a base substrate 10 is provided, and a light shielding layer 20 is formed on the base substrate 10, such as image 3 As shown, a buffer layer 30 covering the light-shielding layer 20 is formed on the base substrate 10, as Figure 4 As shown, an active layer 40 corresponding to the top of the light shielding layer 20 is formed on the buffer layer 30 , and the material of the active layer 40 is a metal oxide semiconductor material.

[0046] Specifically, before the light-shielding layer 20 is fabricated, the base substrate 10 also needs to be c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More