A kind of preparation method of array substrate

An array substrate and substrate technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of narrow signal line width, achieve the effects of improving yield, improving driving effect, and reducing resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] In order for those skilled in the art to better understand the technical solution of the present invention, a method for preparing an array substrate provided by the present invention will be described in detail below with reference to the accompanying drawings.

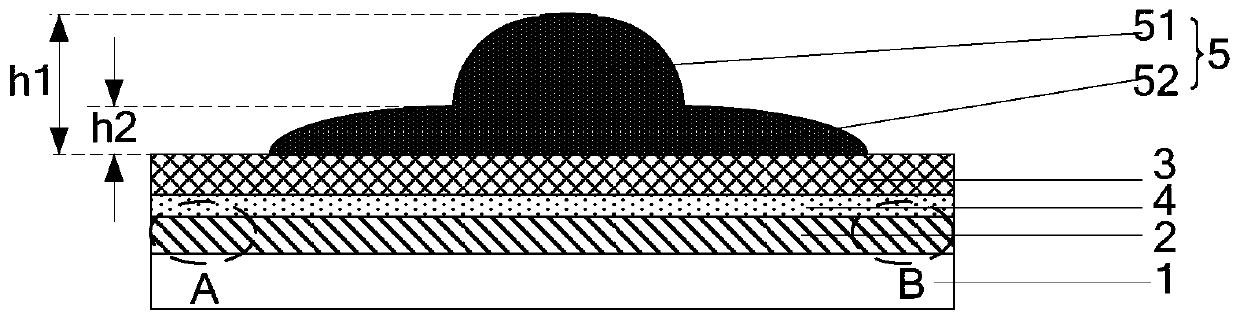

[0043] An embodiment of the present invention provides a method for preparing an array substrate, combining Figure 1a to Figure 3d As shown, the method includes: forming an active layer pattern 2 on a substrate 1 , and forming a gate film 3 on the active layer pattern 2 . Further, an insulating layer film 4 may also be formed between the active layer pattern 2 and the gate film 3 , and the insulating layer film 4 is used to isolate the active layer pattern 2 and the gate film 3 . It should be noted that the method for forming the active layer pattern 2, the gate film 3 and the insulating layer film 4 on the substrate 1 is the same as that of the prior art, and will not be repeated here.

[0044] The method a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More