An Automatic Node Removal Method for Approximate Computation of Circuits

A technology of approximate calculation and node deletion, applied in calculation, computer-aided design, electrical digital data processing, etc., can solve the problems of no node deletion process, failure to take into account errors, circuit delays, power consumption, etc., to improve design efficiency, The effect of expanding the scope of application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

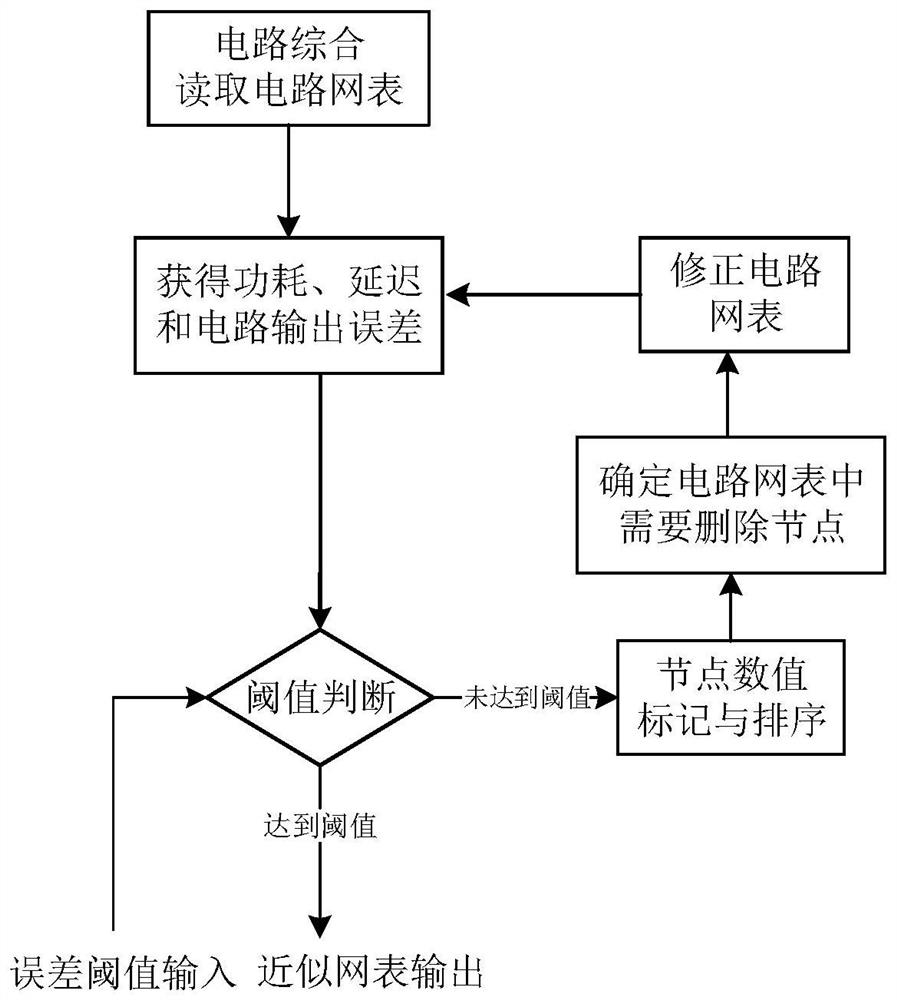

[0030] The present invention provides an automatic node deletion method for circuit approximation calculation, after a short period of iteration and simulation, the optimal approximation calculation is achieved by adopting a cell sorting method with an optimal energy-delay product and error ratio .

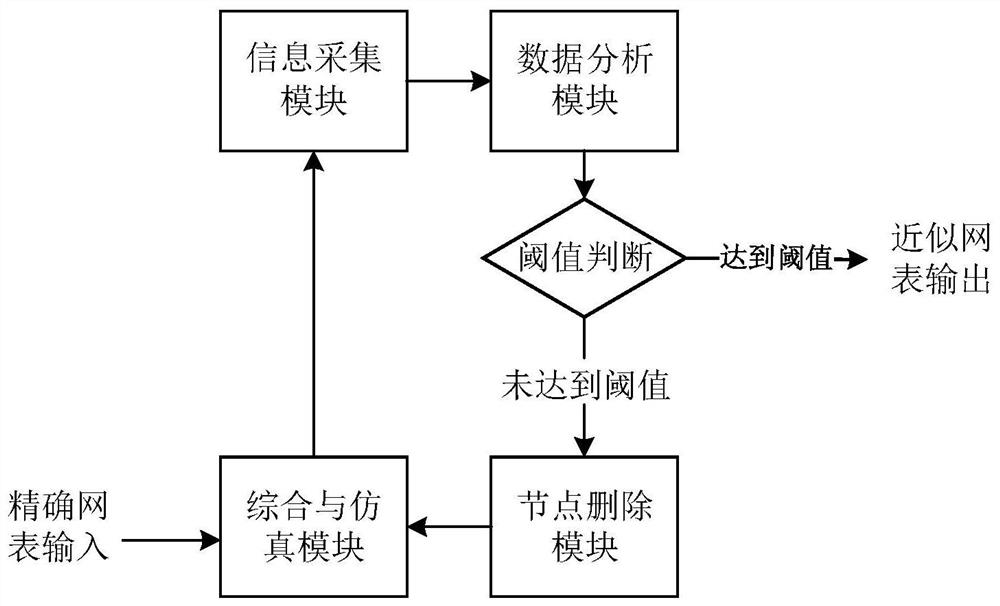

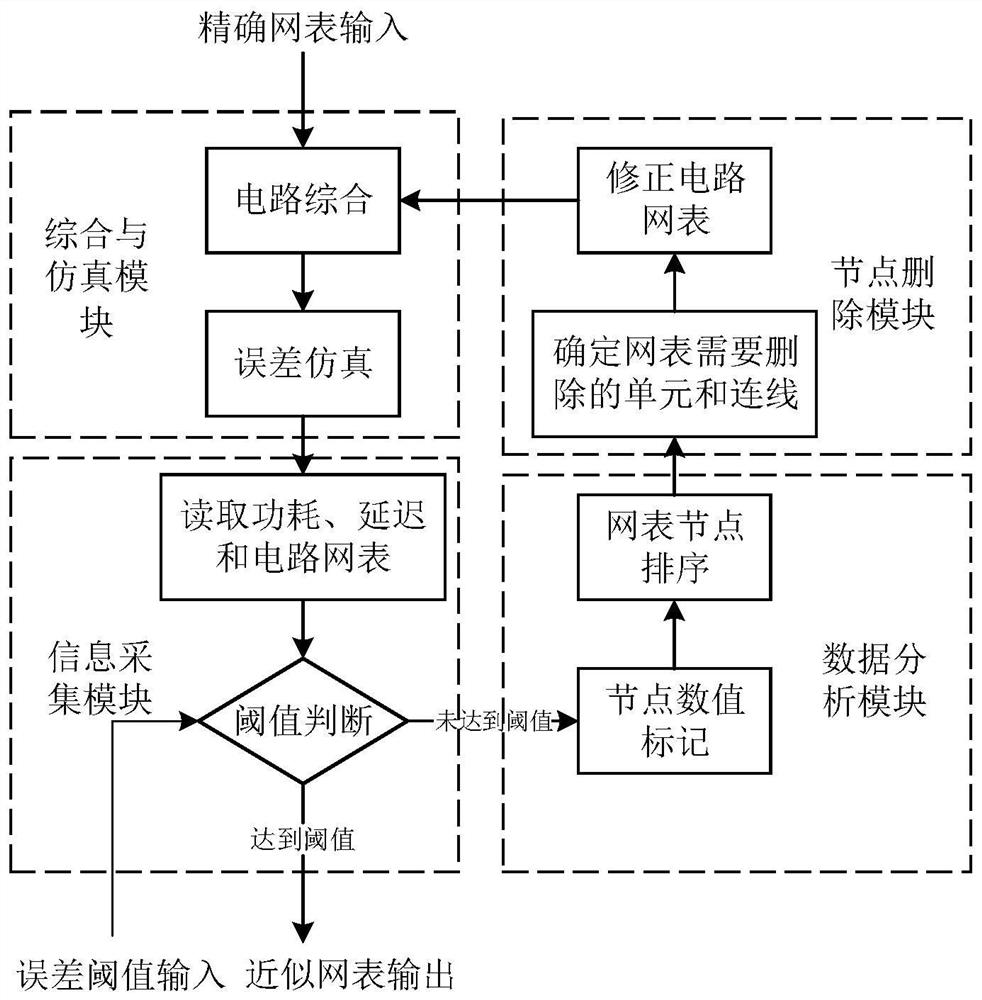

[0031] Such as figure 2 Shown is the structural diagram of applying the automatic node deletion method provided by the present invention to realize approximate calculation in the embodiment, including an information collection module, a data analysis module, a node deletion module and a synthesis and simulation module, and the information collection module is used to collect the synthesis and simulation module The circuit data information generated in and passed to the data analysis module; the data analysis module is used to analyze, process a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com