Link-layer verification platform and method of using binary to save excitation and simulation results

A verification platform and verification method technology, applied in the direction of design optimization/simulation, special data processing applications, instruments, etc., can solve the problems of different results, low verification efficiency, and a large number of test incentive contents, so as to simplify the operation and improve the verification effect. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

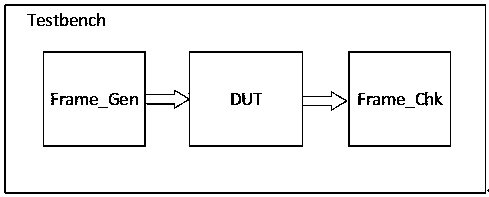

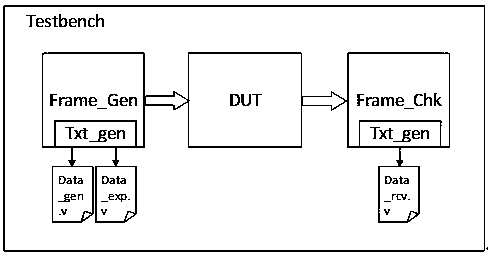

[0037] This embodiment proposes a link layer verification platform that uses binary storage for incentives and simulation results. The verification platform (Testbench) is written in Verilog language, as shown in the attached figure 2 As shown, its structure includes:

[0038] The message generation module Frame_Gen is used to generate test stimulus messages;

[0039] Specifically, the message generation module contains a TXT_GEN module, which is used to save the stimulus file as a binary file, and use the generated binary file to verify the link layer function of the chip; binary is the most common file format, mainly storing text Information, that is, text information; most operating systems today use Notepad and other programs to save, and most software can view it, such as Notepad, browsers, etc.;

[0040] The TXT_GEN module saves Data_gen.v (original file) and Data_exp.v (expected file); Data_gen.v is used to save the original message generated by the message, and Data_...

Embodiment 2

[0053] The link layer verification platform using binary storage of incentives and simulation results proposed in this embodiment, on the basis of the link layer verification platform in Example 1, takes the design under test as a link layer interface module of the QPI protocol, and provides a For specific implementation, learn more about the technical solutions and technical advantages of the link layer verification platform.

[0054] Described design DUT to be tested adopts the link layer interface module of QPI agreement, is used for processing incentive message, realizes utilizing the link layer function of binary file verification QPI agreement; QPI: the QuickPath Interconnect of Intel, is translated as fast channel interconnection; In fact, its official name is CSI, Common System Interface, which is used to realize direct interconnection between chips.

[0055] Since the link layer interface module usually has multiple channels, and each channel is distinguished by a spe...

Embodiment 3

[0067] The link layer verification platform that uses binary storage of incentives and simulation results proposed in this embodiment, on the basis of the link layer verification platform in Embodiment 2, uses the message generation module Frame_Gen according to the link layer data format of the QPI protocol to generate multiple Taking a Flit message as an example, to further introduce the technical solution and technical advantages of the QPI protocol link layer verification platform in detail.

[0068] The message generation module Frame_Gen generates various Flit messages (for example, six types of Flit messages, specifically HOM, SNP, NDR, DRS, NCB, and NCS) according to the link layer data format of the QPI protocol. While generating the above-mentioned various Flit messages, generate the Data_gen.v file in order to record the production of the messages; according to the above-mentioned various Flit messages after the processing and expectations of the CUT to be tested, wr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More