A kind of DC offset elimination circuit and method

A technology for DC offset and circuit elimination, applied in electrical components, transmission systems, etc., can solve problems such as power consumption, large storage space, consumption, etc., to achieve the effect of improving speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

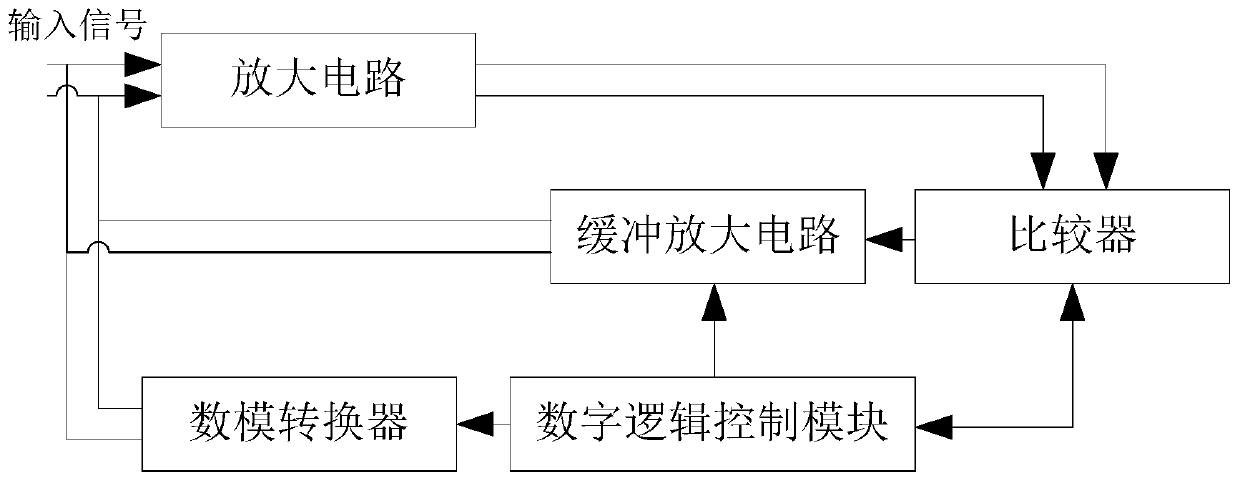

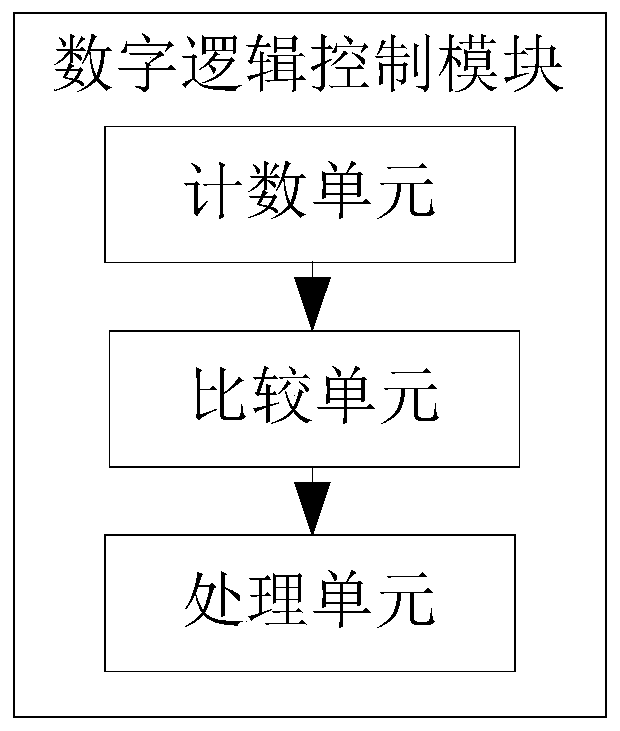

[0047] Such as figure 1 As shown, a DC offset elimination circuit includes: an amplifier circuit, a comparator, a digital logic control module, a digital-to-analog converter and a buffer amplifier circuit.

[0048] The two input terminals of the amplifying circuit are respectively connected to two input signals for amplifying the voltages of the two input signals and outputting two differential signals.

[0049] The two input terminals of the comparator are respectively connected to the two output terminals of the amplifying circuit for comparing the two differential signals and obtaining corresponding digital signals according to the comparison results.

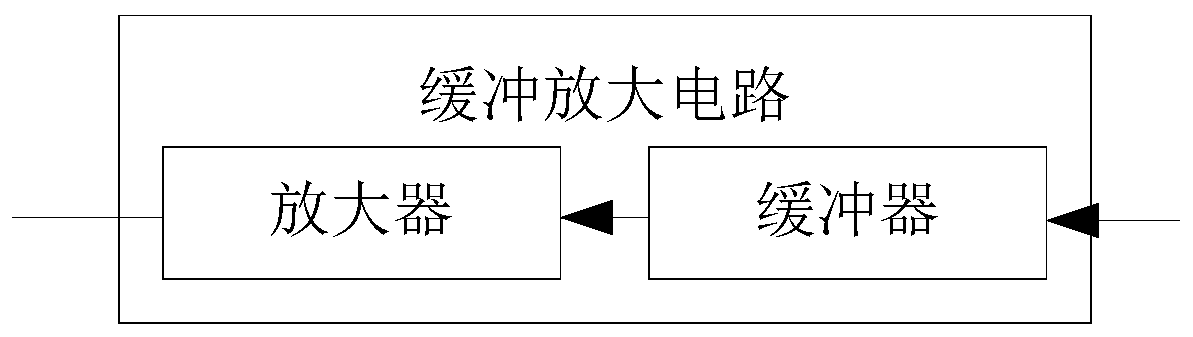

[0050] The input end of the buffer amplifier circuit is con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More