NandFlash address mapping and block management algorithm

A technology of address mapping and block management, which is applied in computing, electrical digital data processing, and input/output process of data processing, etc. It can solve problems such as slowing down disk read and write speed, hidden dangers of data reliability, and limited erasure times

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

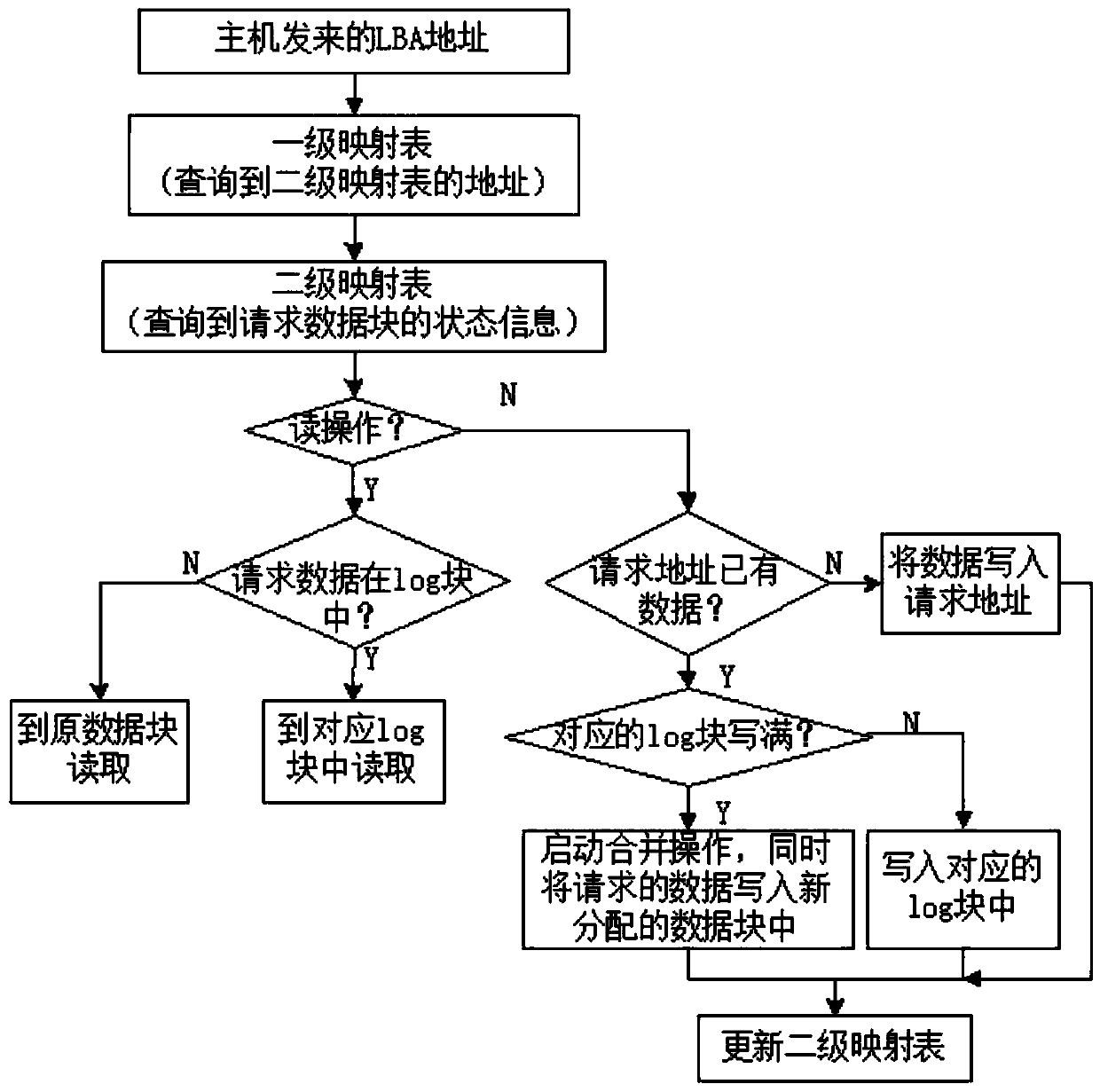

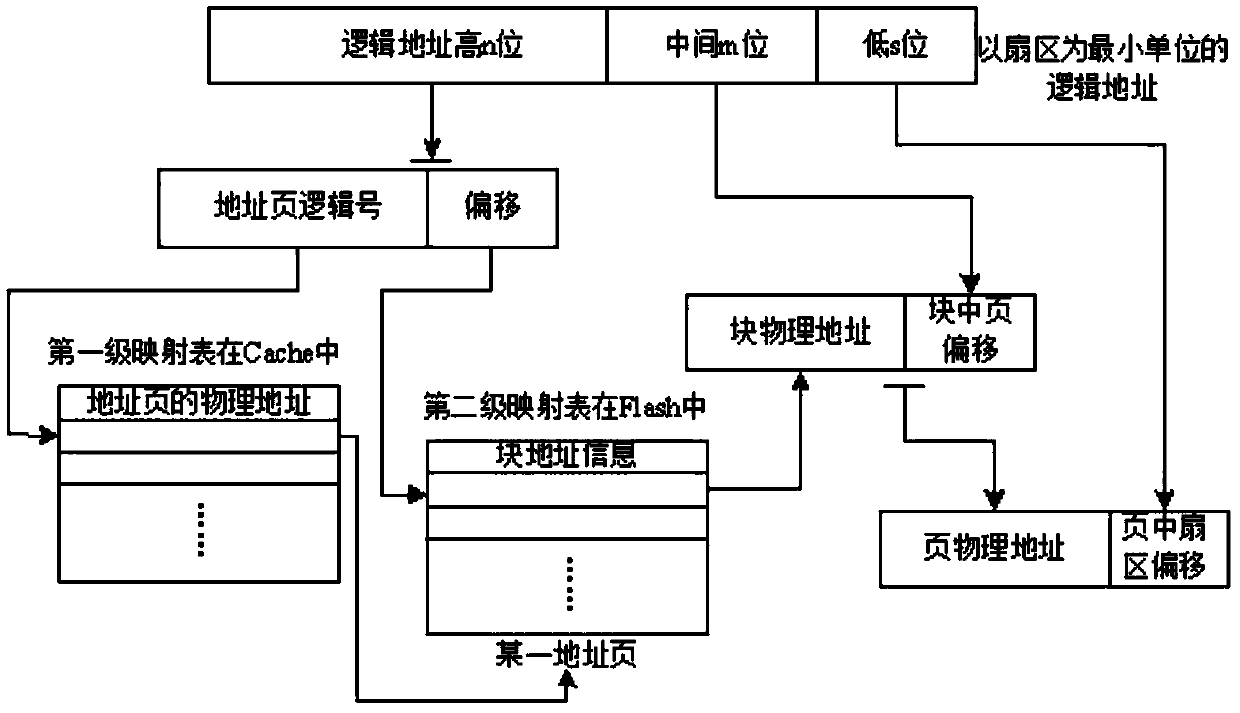

[0049] NandFlash address mapping provided by the invention and block management algorithm comprise the following steps:

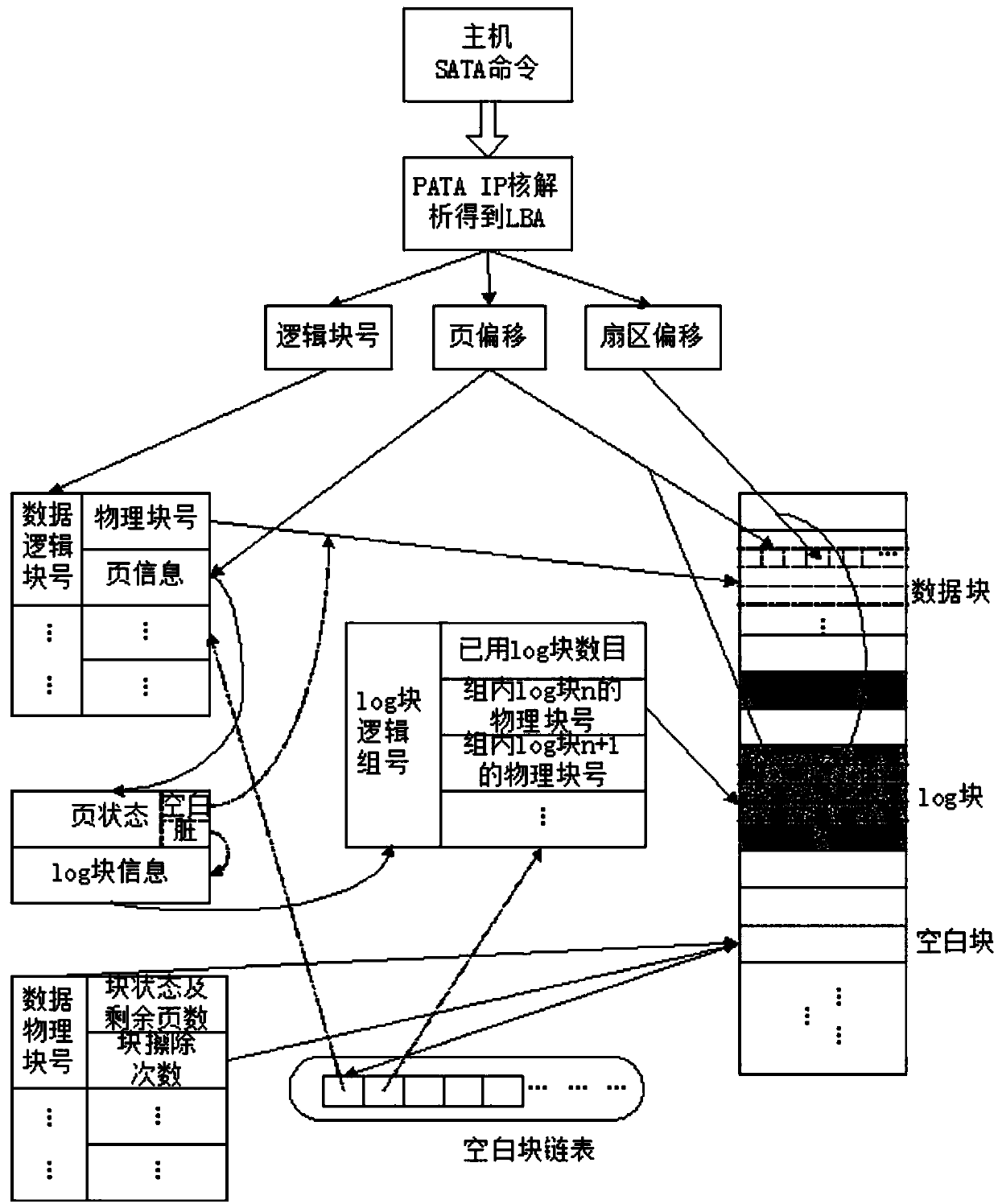

[0050] (1) The entire NandFlash chip space is functionally divided into three parts: the storage mapping table information part, the user data storage part and the blank part. The data operation of the three parts is performed using the block management algorithm. The block management algorithm divides the entire NandFlash array according to the physical space and logic space management;

[0051] The physical space is the actual NandFlash storage medium, and each storage block unit of the NandFlash chip is called a physical block, and is numbered sequentially; the physical block without storing data corresponds to a blank part;

[0052] The logical space includes: 1) data logic block, used to store user data, and convert the sector address sent by the host into a corresponding block number according to the block size of the NandFlash chip, called the logica...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com