NMOS transistor structure and forming method thereof

A transistor and gate structure technology, applied in the manufacture of transistors, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problems of deteriorating the threshold voltage of transistor devices, shortening the channel length, and the device cannot be turned off, and achieves a process result that can be Strong controllability, improved on-current, and optimized device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] In order to make the purpose, technical solutions and advantages of the present invention more clearly understood, the specific embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings.

[0019] The present invention may be embodied in many different forms and should not be construed as limited to the embodiments described herein. It will be understood that when an element such as a layer, region, or substrate is referred to as being "formed on" or "disposed on" another element, it can be directly on the other element or be directly on the other element. There are intermediate elements.

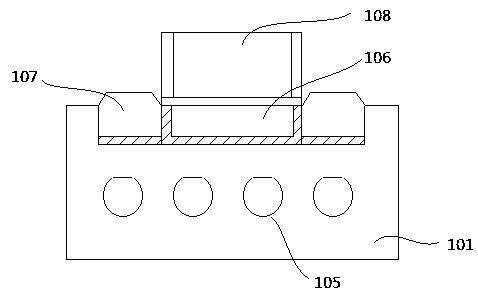

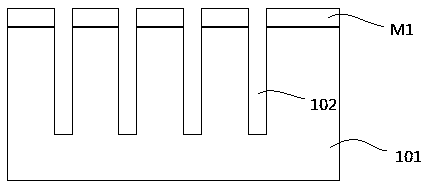

[0020] Such as figure 1 As shown, the NMOS transistor structure of the present invention includes: a substrate 101, a spherical blocking device 105 located in the substrate, the spherical blocking device can effectively weaken the coupling capacitance between the source and the drain, and reduce the The current leaka...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More