HKMG-contained NMOS and PMOS integrated manufacturing method

A technology of manufacturing method and process method, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as electrochemical reaction defects, achieve the effects of reducing defects, improving reliability, and increasing the process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

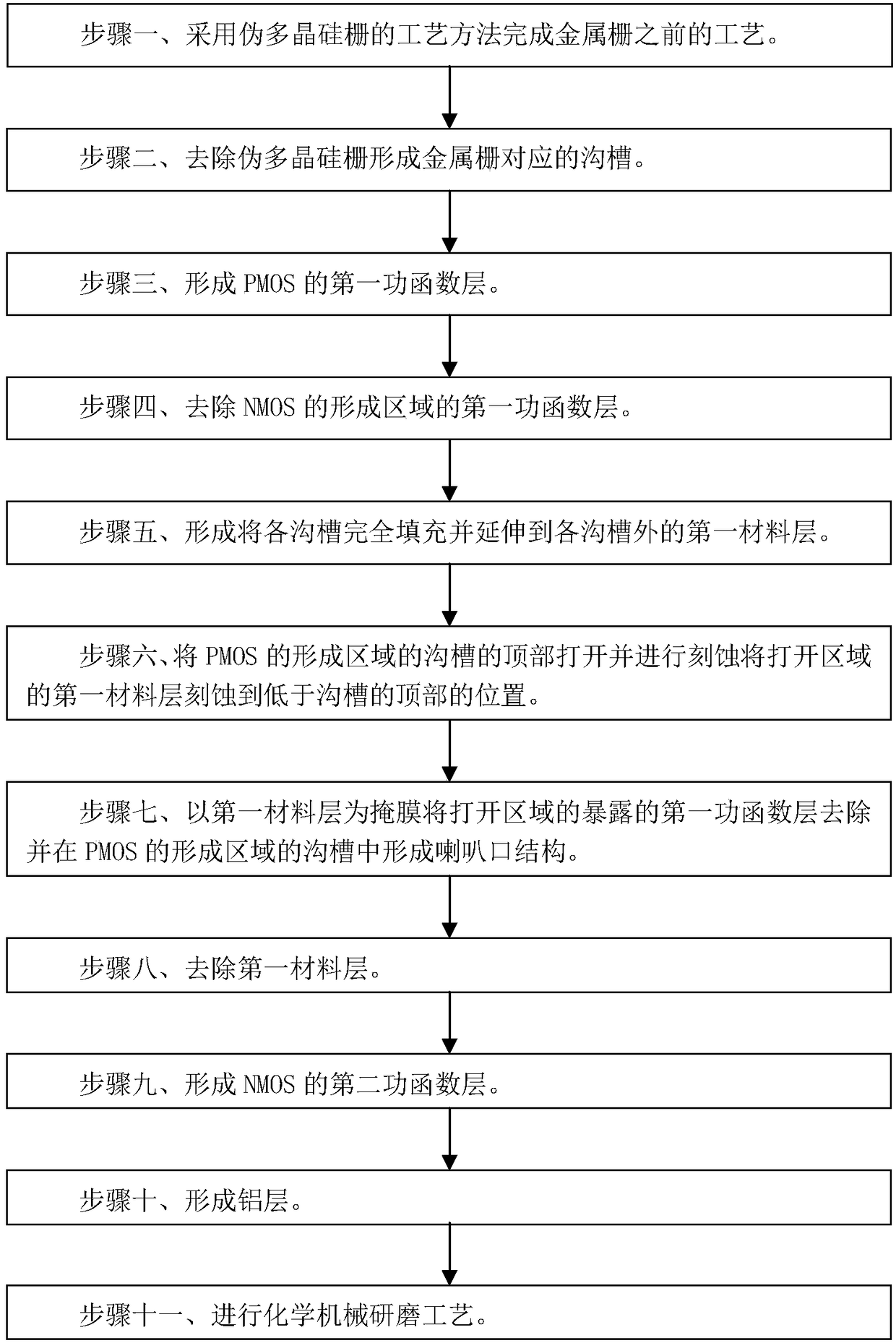

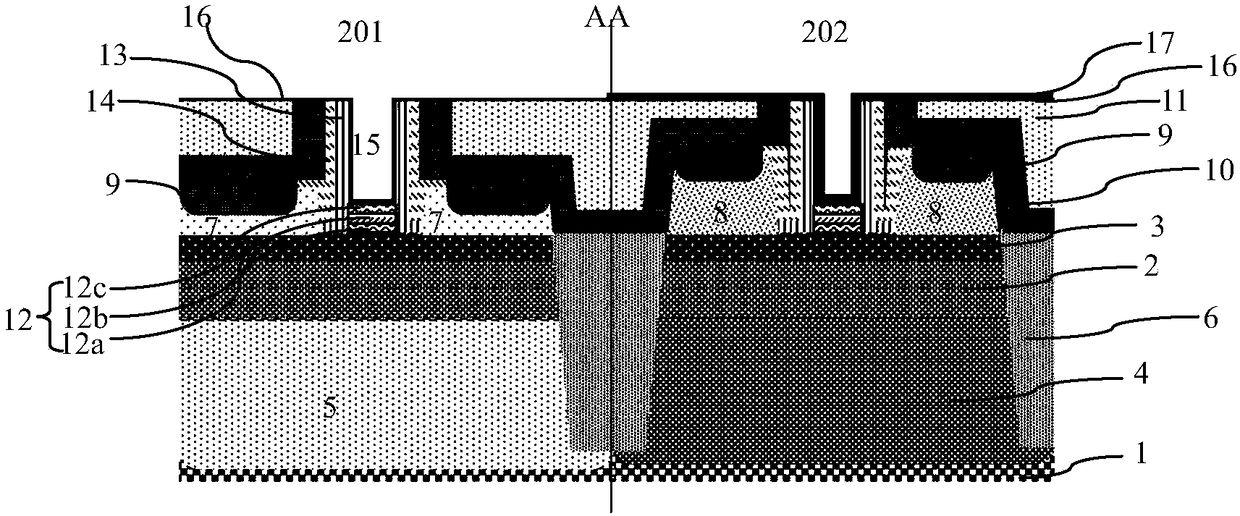

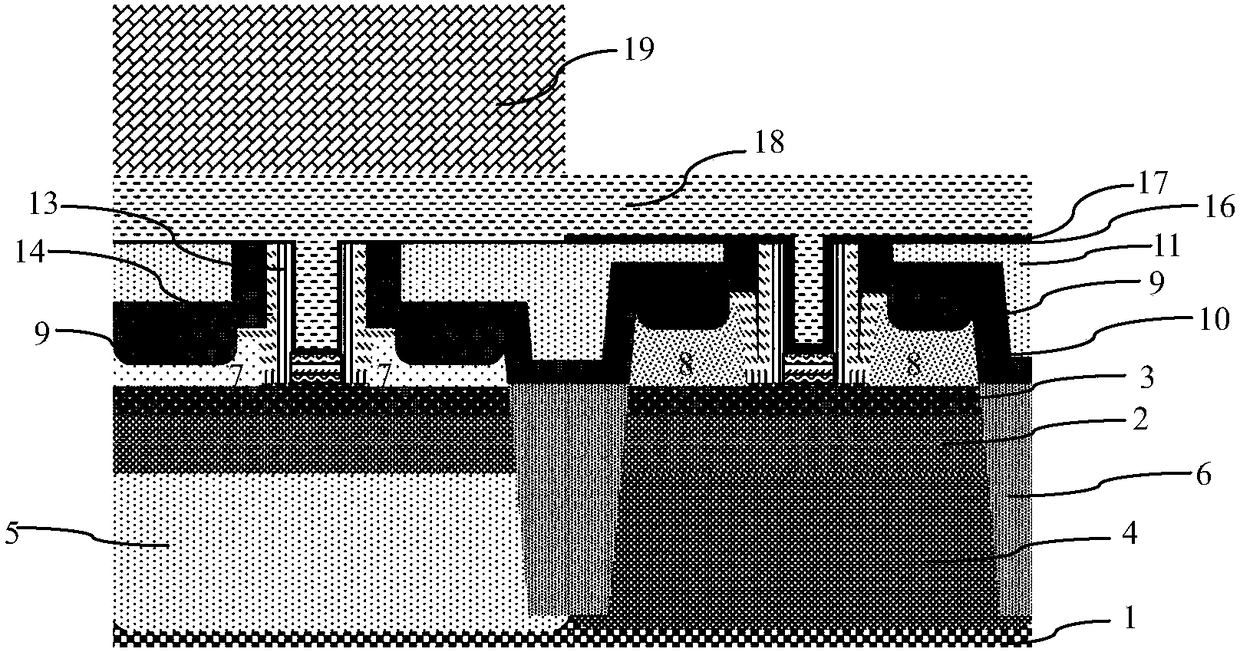

[0040] Such as figure 1 Shown is the flow chart of the manufacturing method of the embodiment of the present invention HKMG; as Figure 2A to Figure 2F As shown, it is a device structure diagram in each step of the method of the embodiment of the present invention. The integrated manufacturing method of NMOS and PMOS with HKMG in the embodiment of the present invention includes the following steps:

[0041] Step 1, such as Figure 2A As shown, the process before the metal gate is completed on the semiconductor substrate by using the process method of the pseudo polysilicon gate.

[0042] The process before the metal gate is the same as the existing steps, which are described as follows:

[0043] figure 1 In the figure, the NMOS formation area is the area 201 on the left side of the AA line, and the PMOS formation area is the area 202 on the right side of the AA line. The technology nodes of the NMOS and the PMOS are below 22nm.

[0044] In the embodiment of the present in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More