Strain PMOSFET with surface stress modulation structure

A technology of surface stress and surface contact, which is applied in semiconductor/solid-state device manufacturing, electrical components, transistors, etc., can solve the problems of PMOSFET performance degradation, process complexity increase, process cost increase, etc., so as to suppress performance decline and decrease Complexity, effects of avoiding etch process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The technical solution of the present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

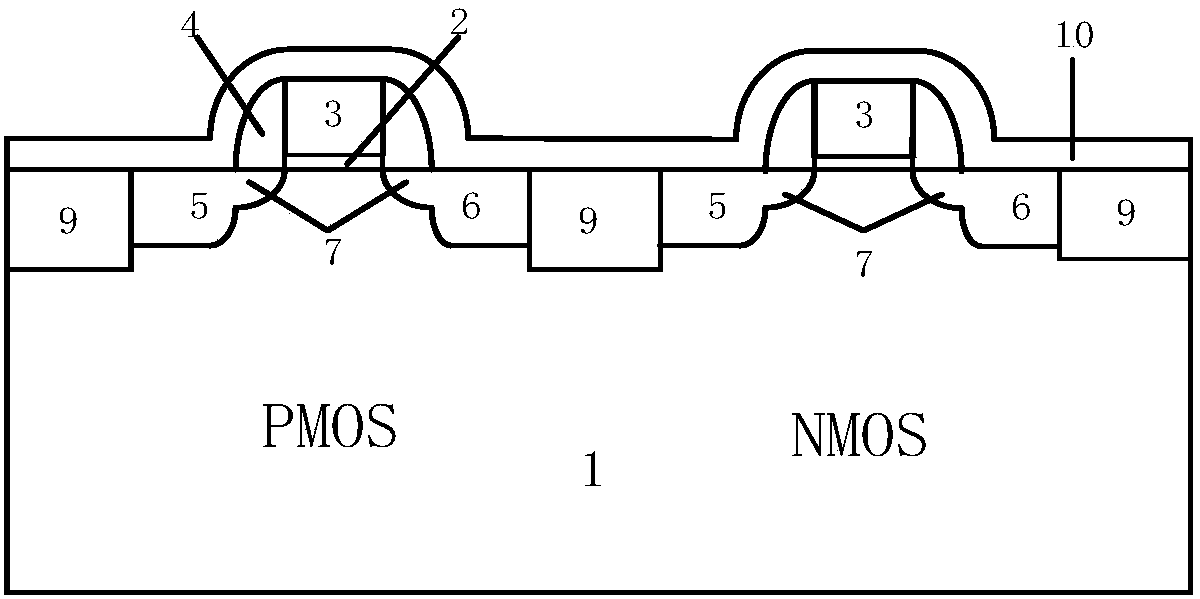

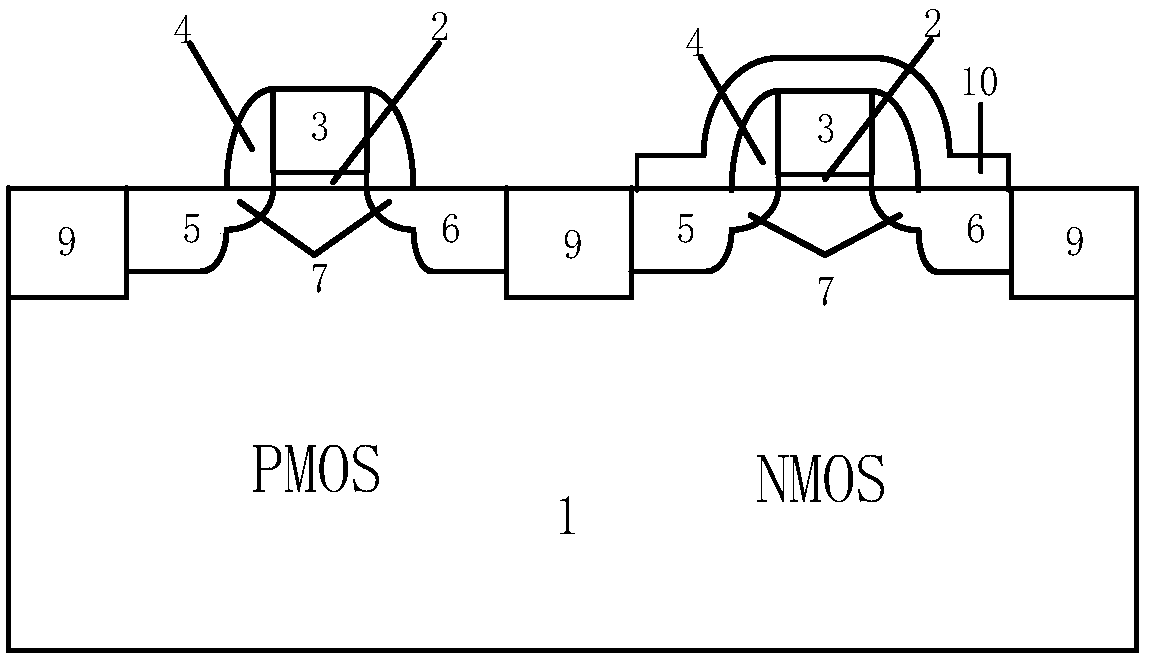

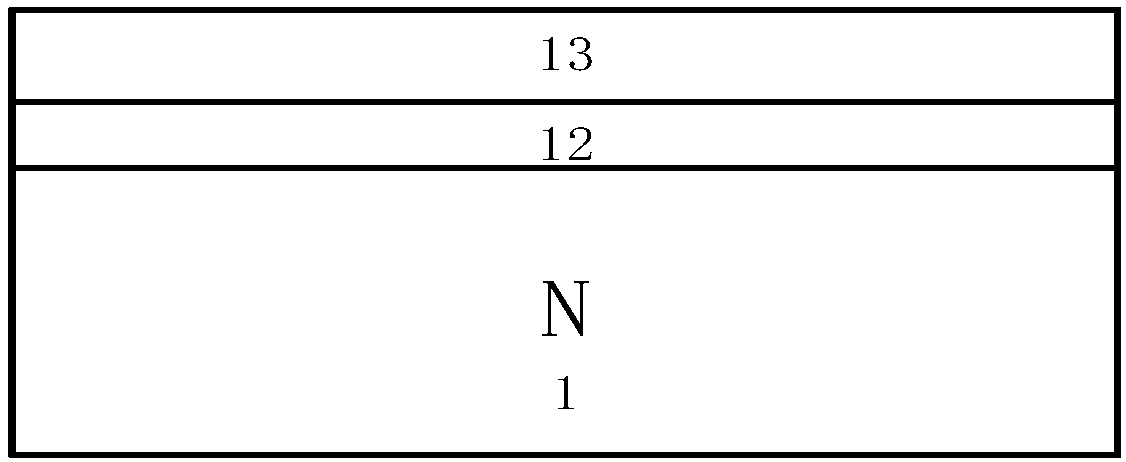

[0035] A strained PMOSFET with a surface stress modulation structure provided by the present invention includes a semiconductor substrate 1, a gate oxide layer 2, a gate 3, a source electrode, a drain electrode and two heavily doped regions, and the semiconductor substrate 1 starts from the bottom The gate oxide layer 2 and the gate 3 are arranged in sequence on the top. Two heavily doped regions are arranged in the semiconductor substrate 1 and located on both sides of the gate 3. The two heavily doped regions are the source region 5 and the drain region 6 respectively. The pole is arranged on the source region 5 and contacts the source region 5, the drain is arranged on the drain region 6 and contacts the drain region 6, and at least one insulating dielectric layer 8 is arranged on the semiconductor substrate 1, and the insu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More