Manufacturing method of semiconductor element

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of manufacturing process technology bottlenecks, high costs, etc., and achieve the goal of increasing mobility, reducing parasitic capacitance, and increasing drive current Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

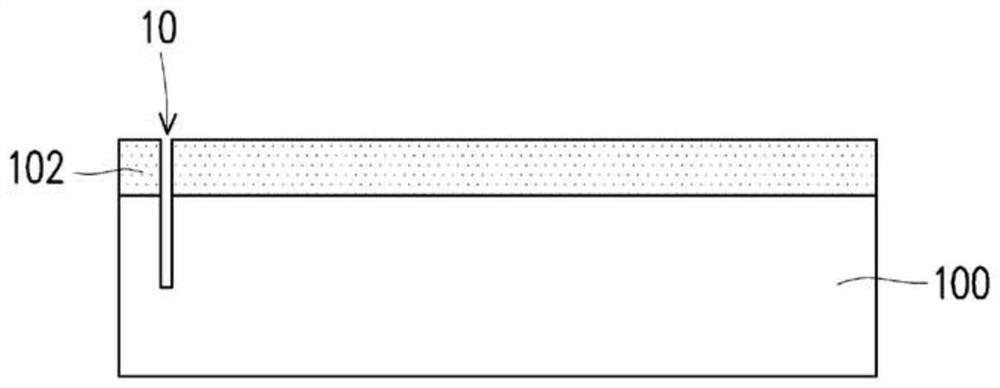

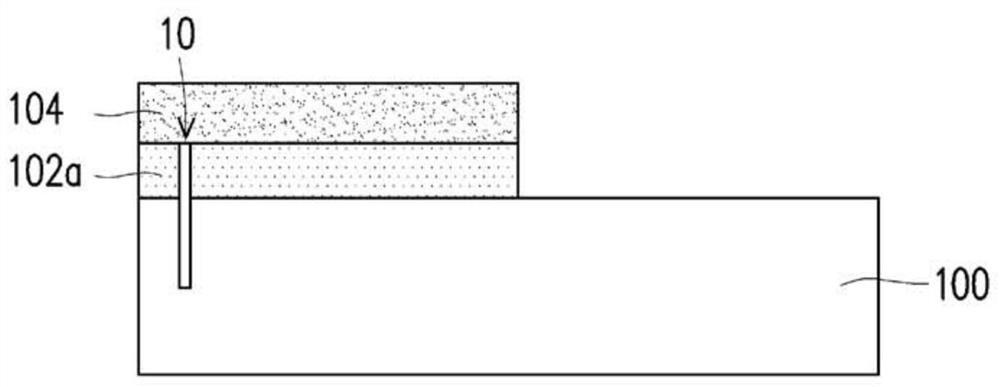

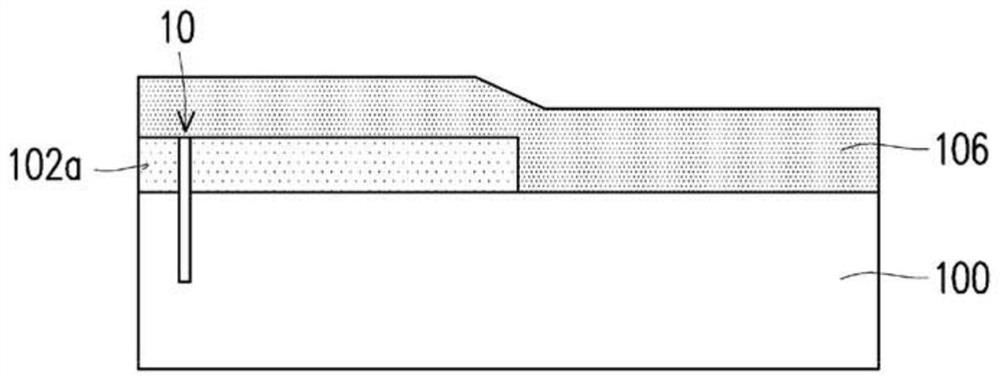

[0056] In the following embodiments, when the first stress layer is a tensile stress layer, the second stress layer is a compressive stress layer; when the first stress layer is a compressive stress layer, the second stress layer is a tensile stress layer. In this embodiment, it is illustrated by taking the first stress layer as a tensile stress layer and the second stress layer as a compressive stress layer as an example, but the present invention is not limited thereto.

[0057] In addition, the thicknesses of layers and regions in the drawings may be exaggerated for clarity. The same or similar reference numbers indicate the same or similar elements, and the following paragraphs will not repeat them one by one.

[0058] In addition, in order to easily describe the relationship between one component or feature and another component or feature depicted in the drawings, for example, "under", "under", "lower part", "under", etc. may be used herein. Spatially relative terms for...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| tensile stress | aaaaa | aaaaa |

| compressive stress | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More