Calibration circuit applied to signal chain analog gain and calibration method thereof

A technology of analog gain and calibration circuit, which is applied in the direction of analog/digital conversion calibration/test, electrical components, analog/digital conversion, etc. It can solve problems affecting chip cost, operational amplifier bandwidth and stability, etc., and achieve outstanding substantive features , avoid performance impact, and reduce the effect of area requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

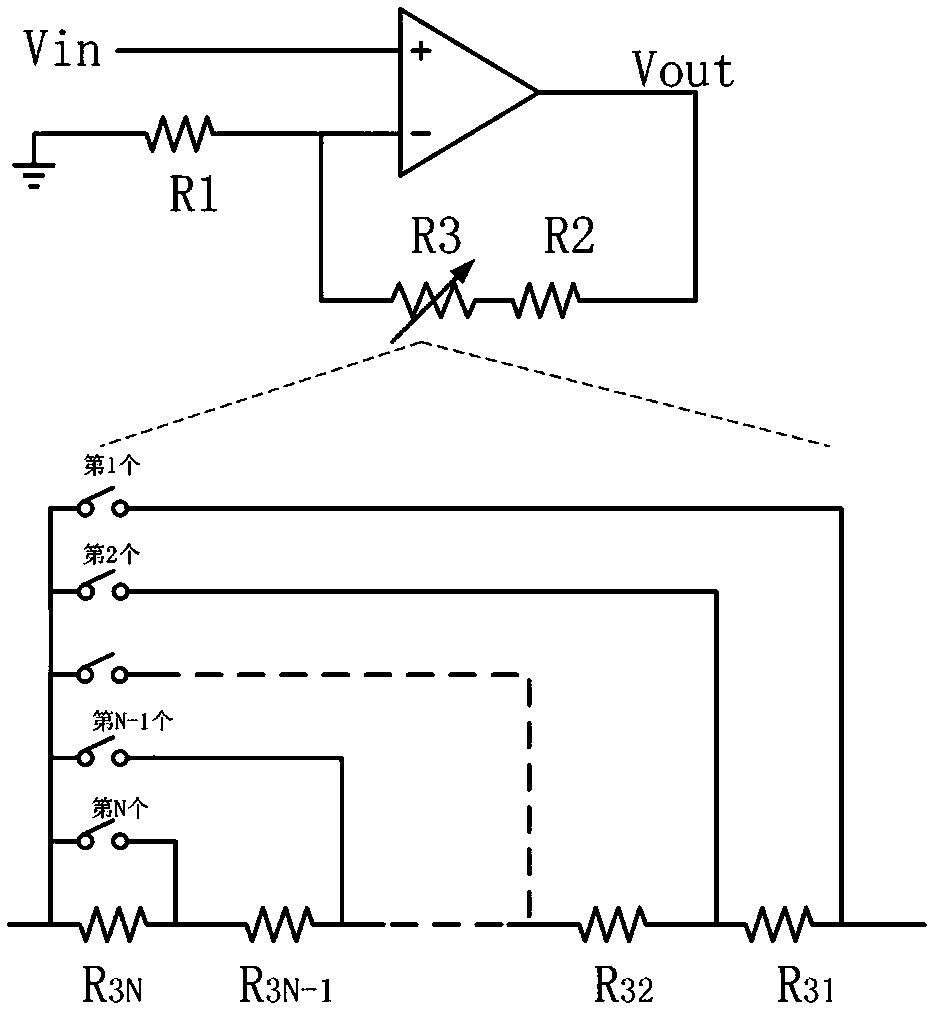

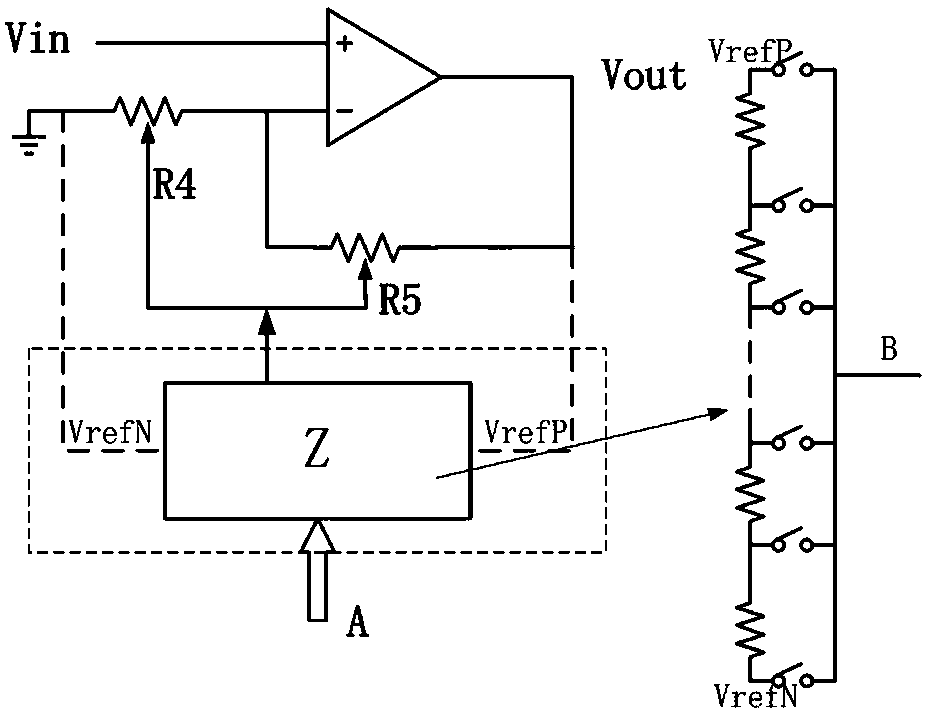

[0017] The specific implementation of the present invention will be described in further detail below in conjunction with the accompanying drawings of the embodiments, so as to make the technical solution of the present invention easier to understand and grasp, so as to define the protection scope of the present invention more clearly.

[0018] Aiming at the deficiencies in the calibration of the analog gain of the existing signal chain, the designers of the present invention have integrated years of experience in this industry, and are committed to proposing a breakthrough in the technical improvement of the calibration resistor link of the analog gain.

[0019] In order to facilitate the understanding of the practicability and advantages of the innovative solution of the present invention, a brief introduction of the Poly resistor on which the technical solution of the present invention is implemented is firstly introduced. Poly resistors are a unique type of resistors in CMO...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More