Fault injection design and verification method of memory with EDAC error tolerance

A technology of fault injection and verification method, which is applied in the direction of static memory, general-purpose stored program computer, and architecture with a single central processing unit, etc. It can solve undiscovered problems, ensure consistency, improve reliability, and simple fault injection method clear effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

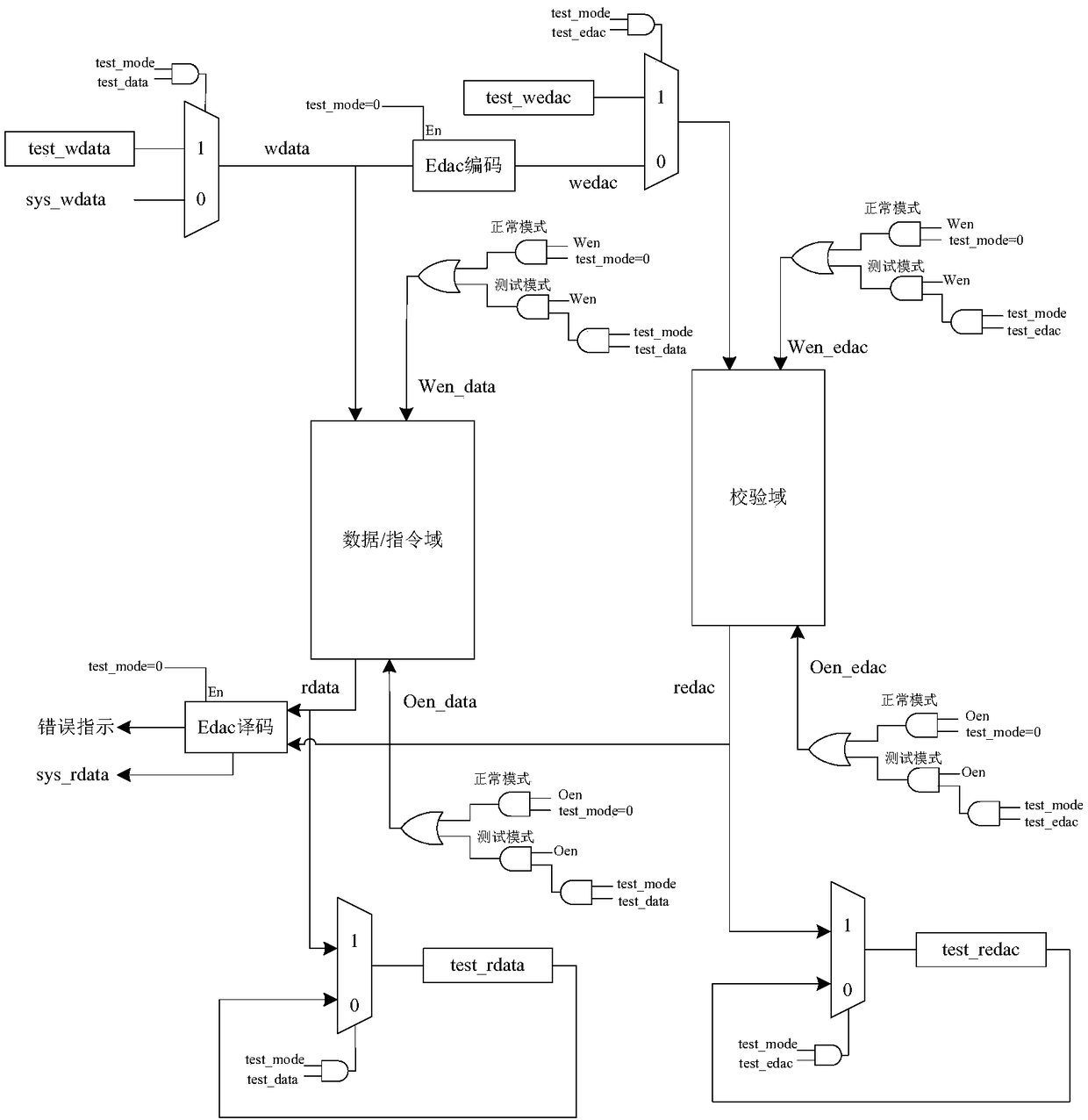

[0032] The invention provides an EDAC fault-tolerant memory fault injection design and verification method, which is used for independently realizing fault injection and verification of the data / instruction domain and the check domain of the fault-tolerant memory.

[0033] A kind of memory fault injection design and verification method with EDAC fault tolerance of the present invention, comprises the following steps:

[0034] S1. For the read and write access of the data / command field and the check field, the working mode is divided into different controls;

[0035] In normal working mode, the data / command field and the check field read and write access control signals and control timing are consistent, and there is no need to set an independent access control signal for the check field, and it is not necessary to allocate additional The access address, the data / instruction field and the verification field are in one-to-one correspondence, just use the same address as the data...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More