Semiconductor structures and methods of forming them

A technology of semiconductor and gate structure, which is applied in the field of semiconductor structure and its formation, can solve the problems such as the decline of electrical performance of semiconductor devices, and achieve the effects of avoiding adverse effects, increasing device speed, and improving electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] It can be known from the background technology that the introduction of a polysilicon interconnection layer easily leads to a decrease in the electrical performance of the formed semiconductor device. Now combine an invented semiconductor structure formation method to analyze the reasons.

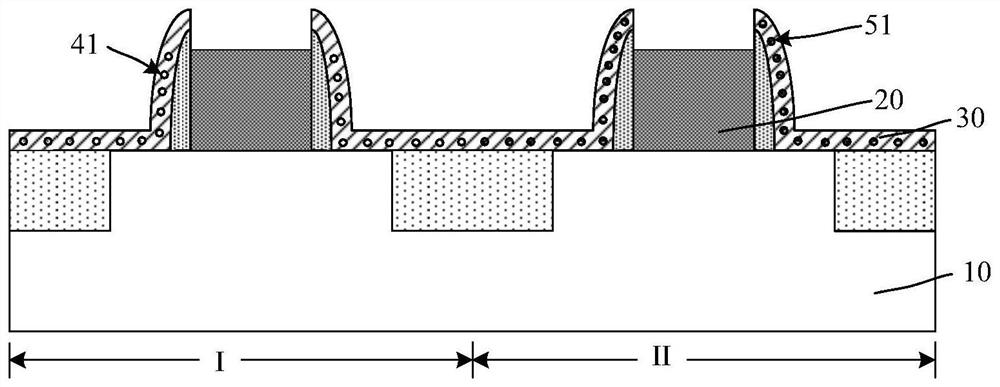

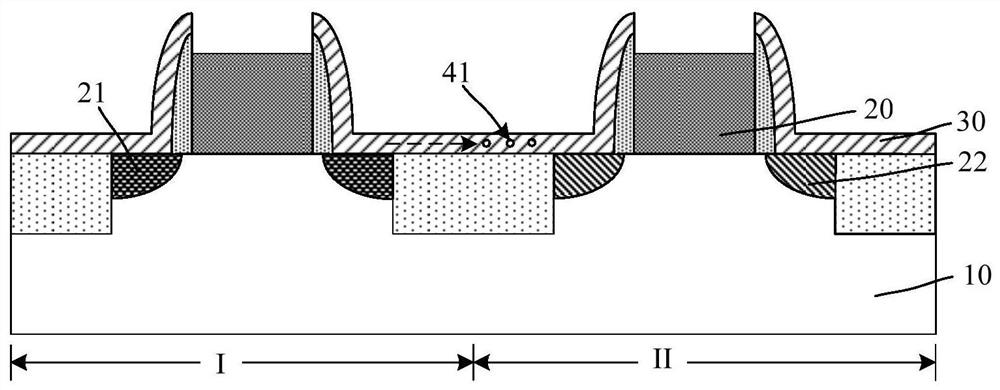

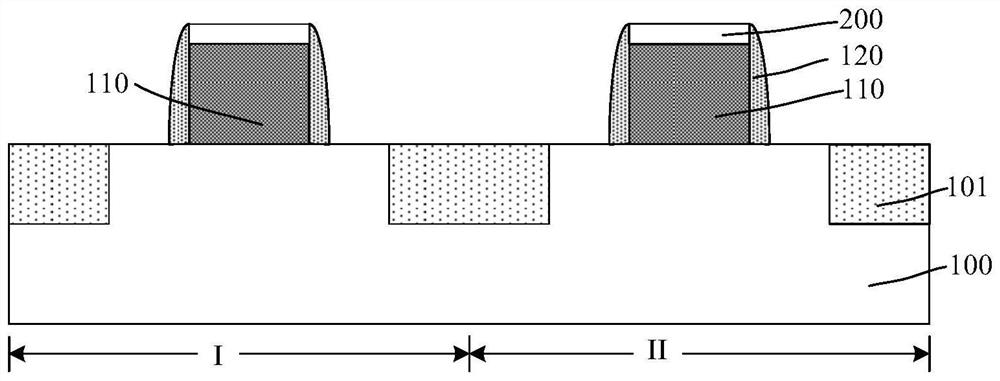

[0033] Combined reference figure 1 with figure 2 , Shows a schematic structural diagram corresponding to each step in a method for forming a semiconductor structure.

[0034] reference figure 1 , A substrate 10 is provided, the substrate 10 includes adjacent NMOS regions I and PMOS regions II; a gate structure 20 is formed on the substrate 10 of the NMOS region I and the PMOS region II; A polysilicon interconnection layer 30 is formed on the sidewalls of the structure 20 and the substrate 10 exposed by the gate structure 20; N-type ions 41 are doped into the polysilicon interconnection layer 30 of the NMOS region I; The polysilicon interconnect layer 30 is doped with P-type ions 51.

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More