Hole forming method

An amorphous carbon and material layer technology, applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of storage electron density limit, development technology limit, etc., to avoid the difference between the bottom size and the top size Large variance, cost reduction, and improved effect of inconsistent aperture roundness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

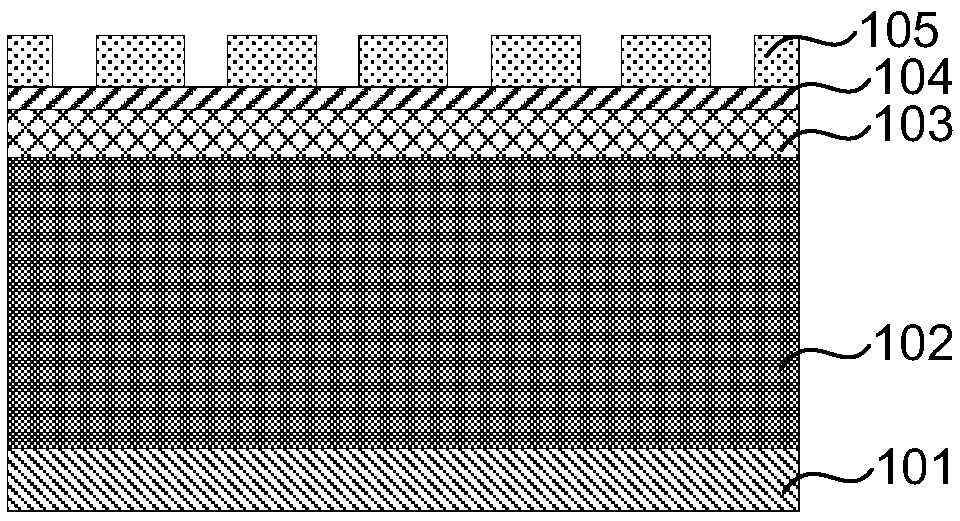

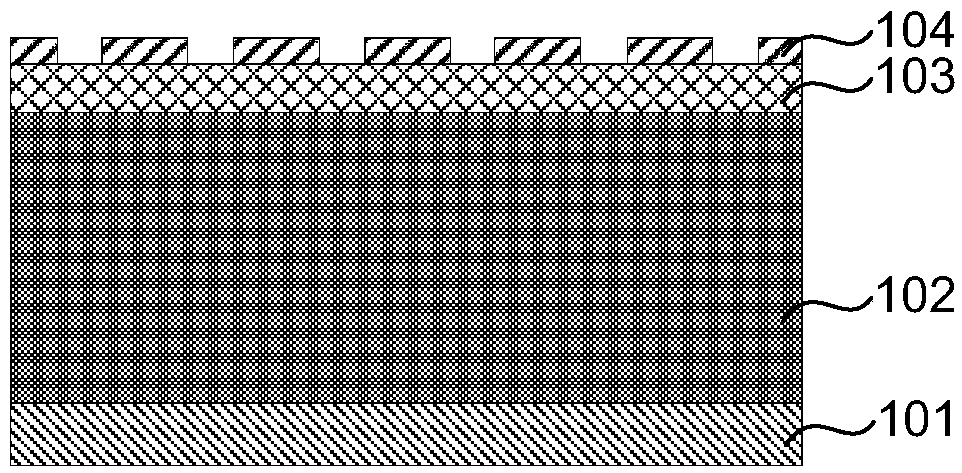

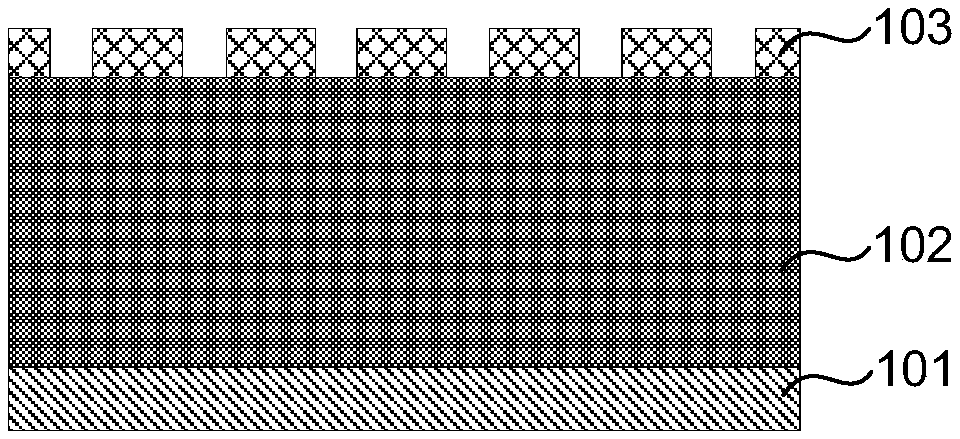

[0038] image 3 is a process flow diagram of the hole forming method according to the embodiment of the present invention. 4(A) to 4(J) show cross-sectional views at different stages of the hole forming method according to the embodiment of the present invention.

[0039] The hole forming method of the present embodiment generally includes the following steps:

[0040] S1: providing a substrate and a layer to be etched arranged on the substrate;

[0041] S2: forming a first etching material layer on the layer to be etched;

[0042] S3: Etching the first etching material layer to form a first mask layer;

[0043] S4: forming an auxiliary mask layer in the gap of the first mask layer; and

[0044] S5: Etching the layer to be etched by using the first mask layer and the auxiliary mask layer as masks to form holes.

[0045] Specifically, in step S1, for example as shown in FIG. 4(A), a substrate 101 is provided, and a layer 102 to be etched is formed on the substrate 101.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More