Manufacturing method of CMOS thin film transistor and manufacturing method of LTPS array substrate

A technology of thin-film transistors and manufacturing methods, which is applied in the display field, can solve problems such as increased manufacturing costs, complex production processes, and large investment in equipment, and achieve the effects of reducing manufacturing costs, reducing the number of photomasks, and increasing production capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] In order to make the purpose, technical solution and effect of the present application more clear and definite, the present application will be further described in detail below with reference to the accompanying drawings and examples.

[0022] This application provides a method for manufacturing CMOS thin film transistors and LTPS array substrates. In this method, by changing the design of the mask, two doping processes can be realized with one mask process, which can reduce the number of masks in the manufacturing process. , shorten the production cycle, reduce the production cost, and increase the production capacity of the array substrate.

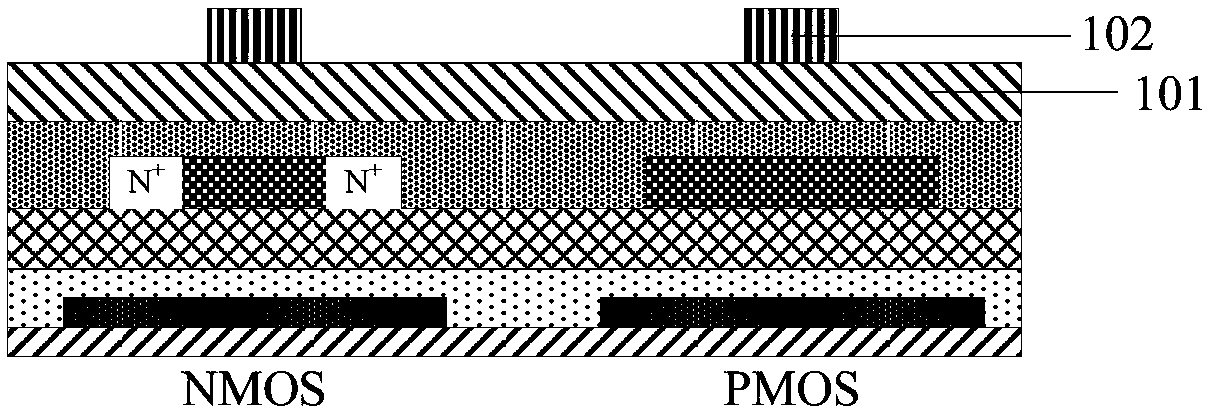

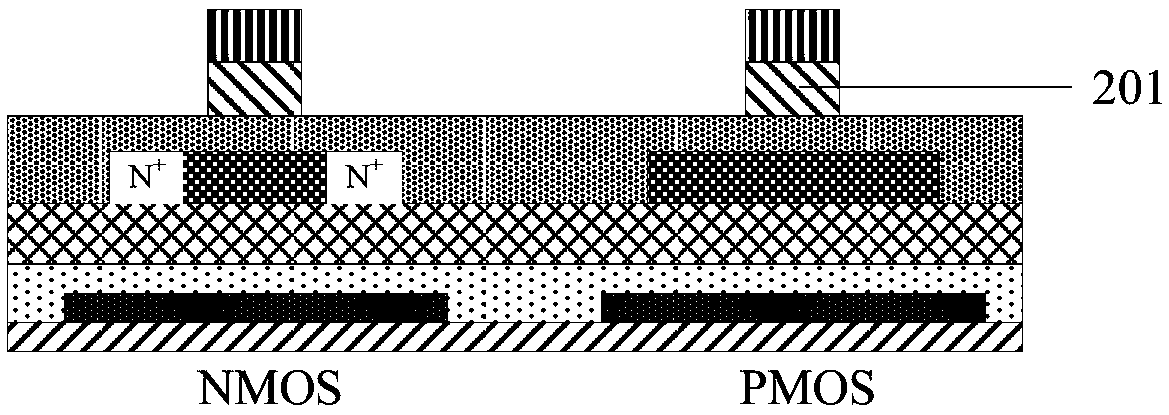

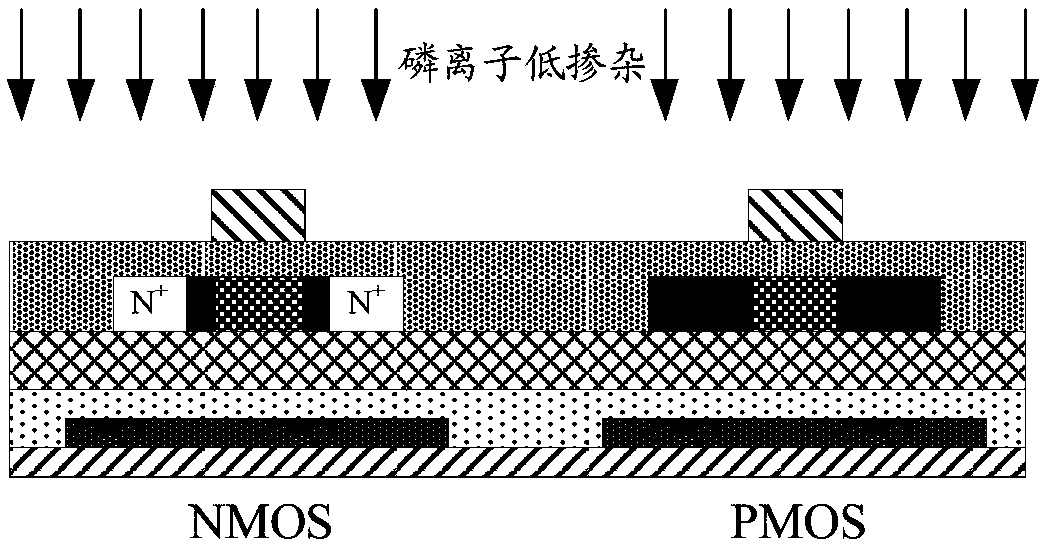

[0023] see Figure 5 , Figure 5 It is a schematic flow chart of the first embodiment of the manufacturing method of the CMOS thin film transistor of the present application. In this embodiment, the manufacturing method of the CMOS thin film transistor comprises the following steps:

[0024] S501: Provide a substrate, and seq...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com