Analog signal FFT implementation method based on FPGA and circuit thereof

A technology of analog signal and implementation method, which is applied in the field of spectrum analysis of signal processing, can solve the problems such as the effect is not intuitive enough, and achieve the effect of convenient capture and analysis, fast speed and good real-time response

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

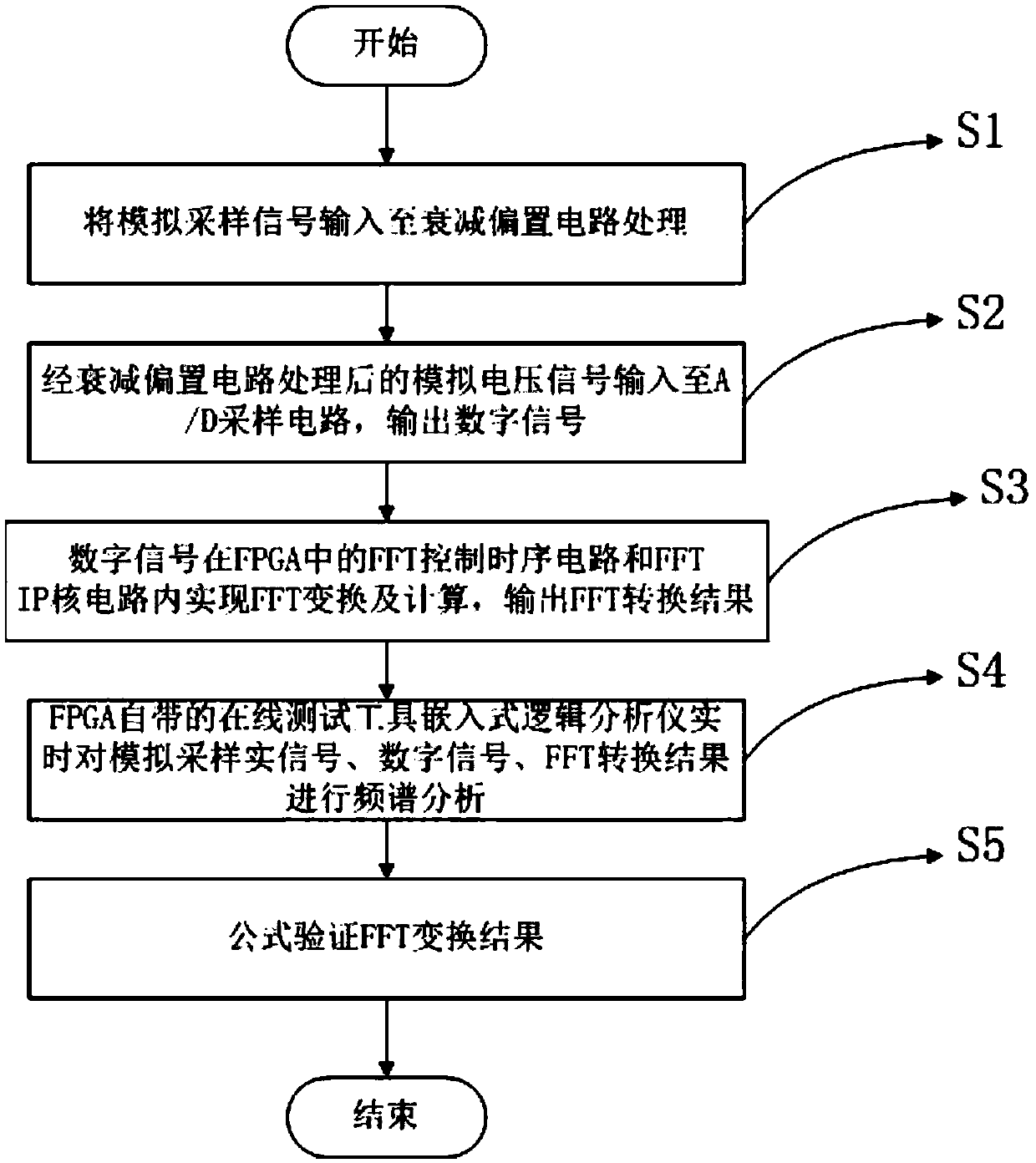

[0048] like figure 1 As shown, the present embodiment relates to a FFT implementation method of an FPGA-based analog signal, and the FFT implementation method includes the following steps:

[0049] S1. Signal processing: input the analog sampling signal to the attenuation bias circuit for processing, so as to attenuate the voltage of the analog sampling signal to the input analog voltage range required by the A / D sampling circuit;

[0050]S2, A / D conversion: the analog voltage signal processed by the attenuation bias circuit is input to the A / D sampling circuit for A / D conversion, and a digital signal is output;

[0051] S3. FFT transformation and calculation: input the digital signal to the IP core in the FPGA, call the IP core to realize FFT transformation and calculation, and output the FFT conversion result;

[0052] S4. Spectrum analysis: Call the embedded logic analyzer, an online test tool that comes with FPGA, to perform spectrum analysis on analog sampling signals, d...

Embodiment 2

[0072] In this embodiment, subsequent IFFT and D / A processing are also carried out, so it is more intuitive to use subsequent inverse operations for verification. like Figure 5 As shown, the previous steps are basically the same as in the first embodiment, specifically: after step S3, step S31 is executed:

[0073] The FFT conversion result is input to the IP core in the FPGA, the IP core is called to perform IFFT conversion, the IFFT conversion result is input to the D / A recovery circuit, and the processed analog recovery signal is output.

[0074] Further speaking, step S31 mainly includes the following steps:

[0075] S311. The mode of the IP core is selected as IFFT transformation, and the IP core performs IFFT transformation according to the result of the FFT transformation, and outputs the first data, the last data, the exponent factor and the final result of the IFFT after the IFFT transformation;

[0076] S312. Input the final result of the IFFT to the D / A recovery ...

Embodiment 3

[0083] An FFT implementation circuit of an FPGA-based analog signal is provided, and the circuit includes:

[0084] power module;

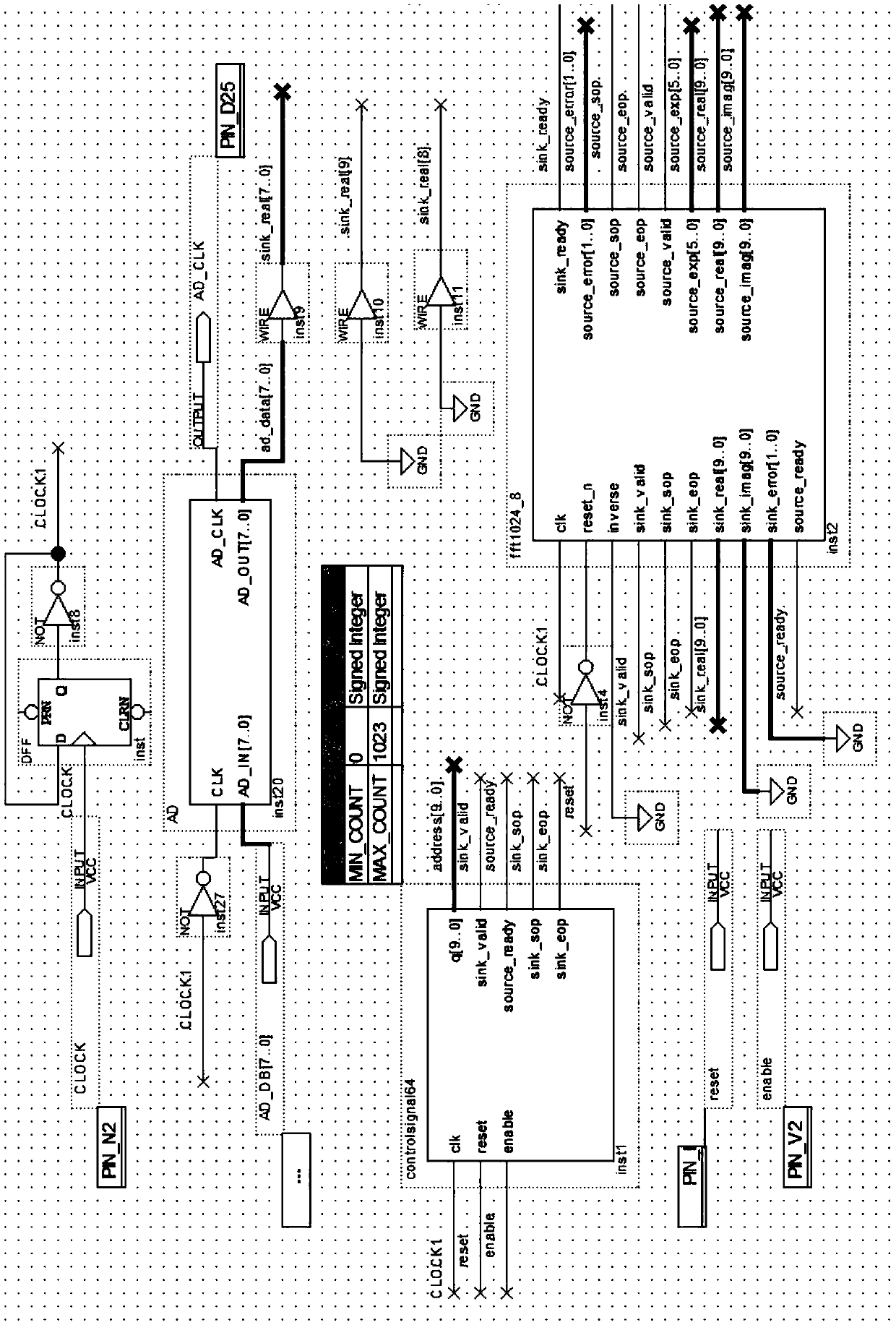

[0085] A clock frequency division circuit is electrically connected to the power module to generate the required starting frequency;

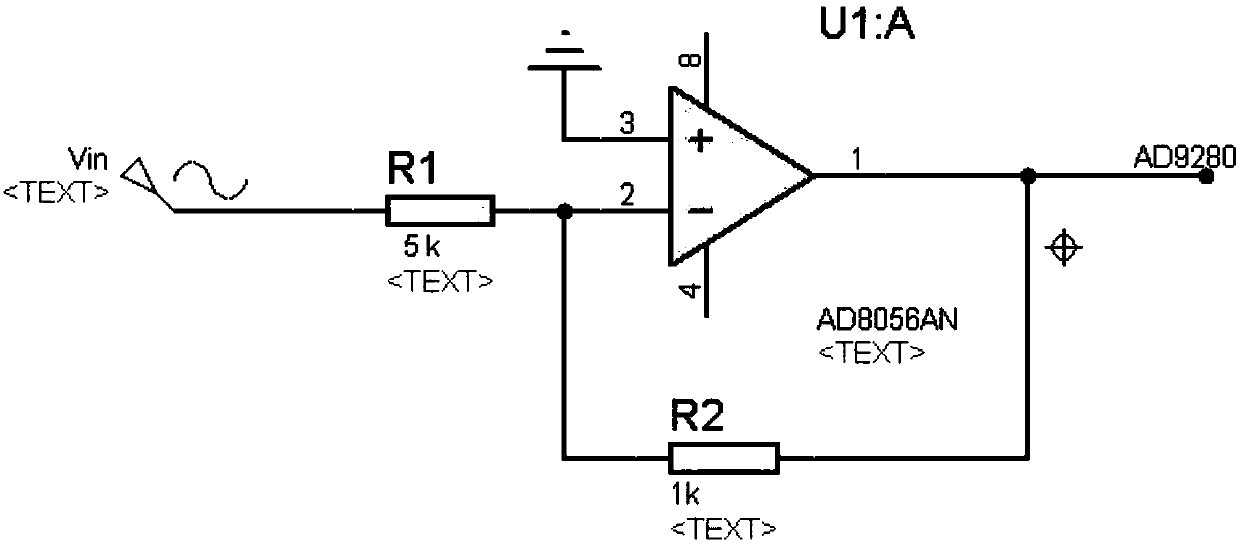

[0086] The attenuation bias circuit is electrically connected to the power supply circuit, and is used to attenuate the voltage of the analog signal to the input analog voltage range required by the A / D sampling circuit;

[0087] The A / D sampling circuit is electrically connected with the clock frequency division circuit and the attenuation bias circuit, and is used to receive the attenuated analog voltage and convert it into a digital quantity;

[0088] The FFT control timing circuit is electrically connected with the clock frequency division circuit to generate a timing signal for controlling the FFT;

[0089] The FFT_IP core circuit is electrically connected with the clock frequency division circuit and is use...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More