Two-level pipeline architecture based on RISC-V instruction set

A RISC-V, two-level pipeline technology, applied in the direction of concurrent instruction execution, program control design, instruments, etc., can solve the problems of high cost of ARM commercial architecture core authorization, inability to carry enough instruction codes, and low processor performance. Achieve the effect of reducing the cost of architecture authorization, improving accuracy and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention.

[0046] The present invention provides a two-level pipeline architecture based on RISC-V instruction set. The working principle is to reduce the cost of the processor core architecture and improve the performance of the processor by adopting the two-level pipeline architecture in the processor core.

[0047] The present invention will be described in further detail below in conjunction with examples and specific implementation methods.

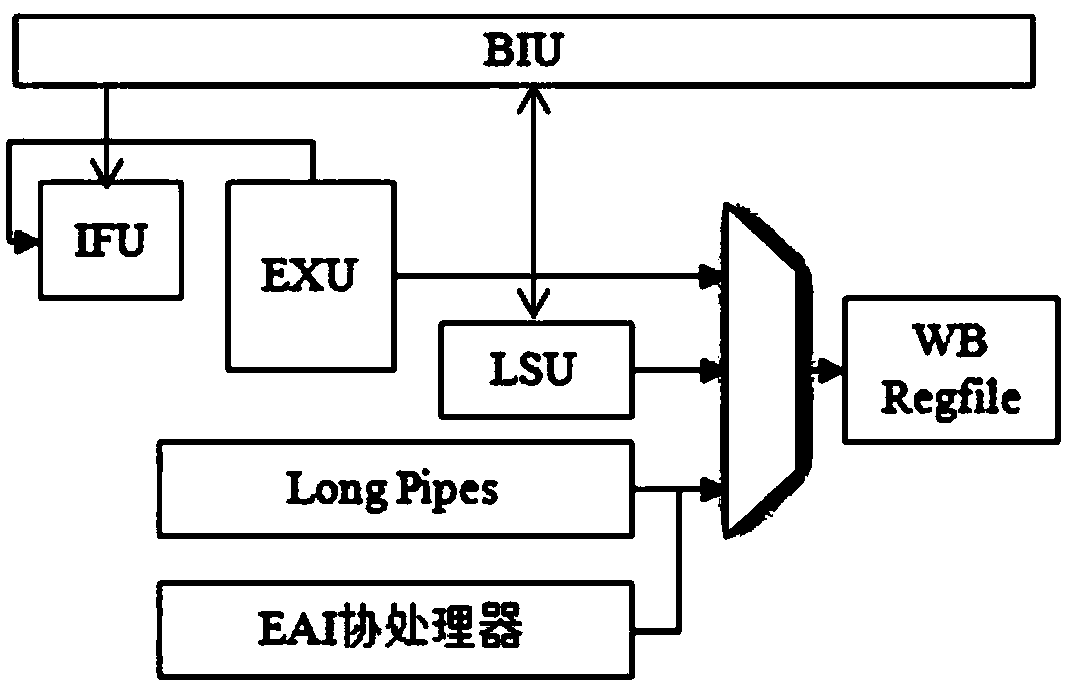

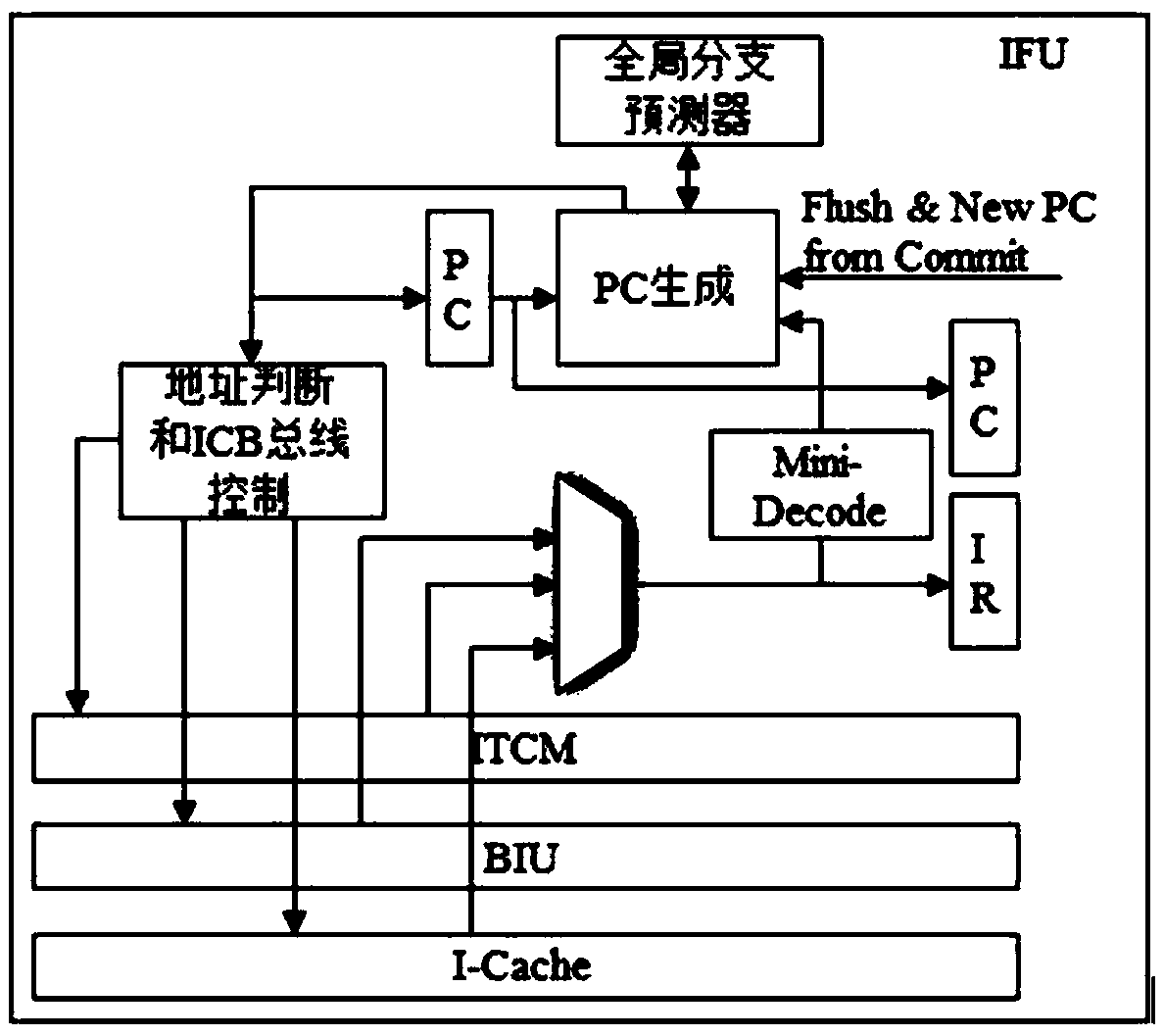

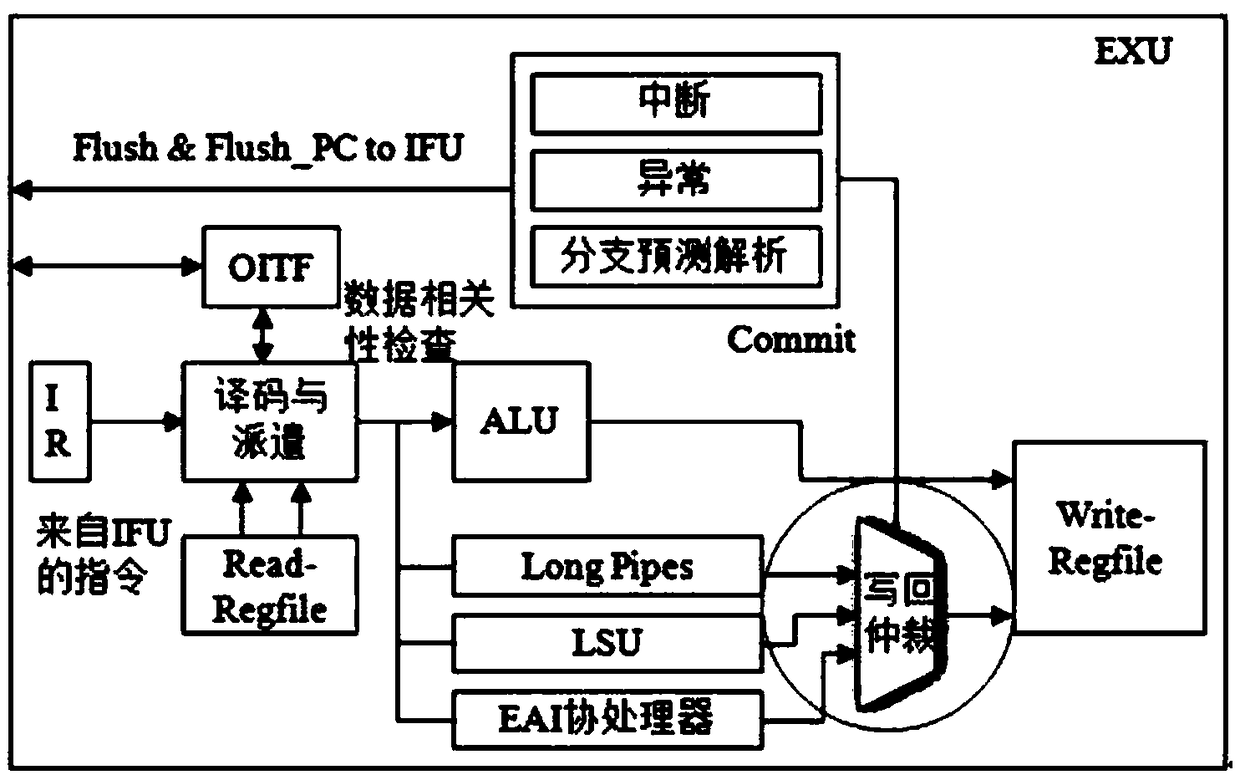

[0048] Such as Figure 1-Figure 7 As shown, a two-level pipeline architecture based on the RISC-V instruction set, the architecture includes: an instruction fetch unit (IFU: Instruction Fetch Unit), an execution unit (EXU: Execution Unit), a data read and write unit (LSU: load store unit), long pipeline data processing unit (Long Pipes), exten...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More