A Design Method of FPGA-Based Yolo Network Forward Reasoning Accelerator

A design method and forward reasoning technology, applied to biological neural network models, neural architectures, etc., can solve problems such as limitations, FPGA incapacity, and accelerated network scale, achieving the effects of increasing speed, less on-chip resources, and ensuring stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

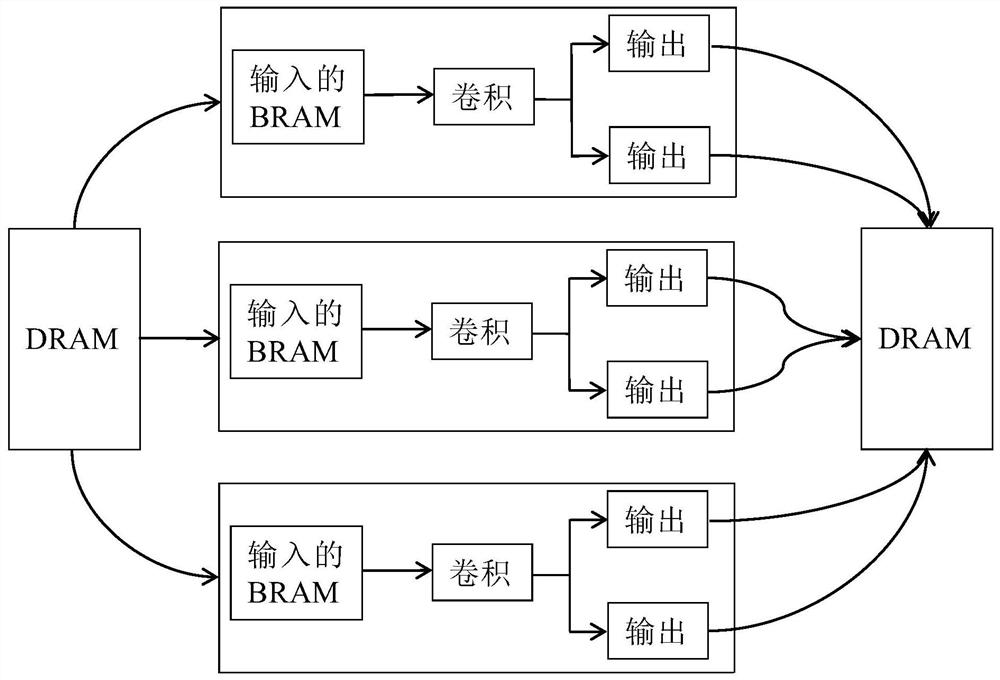

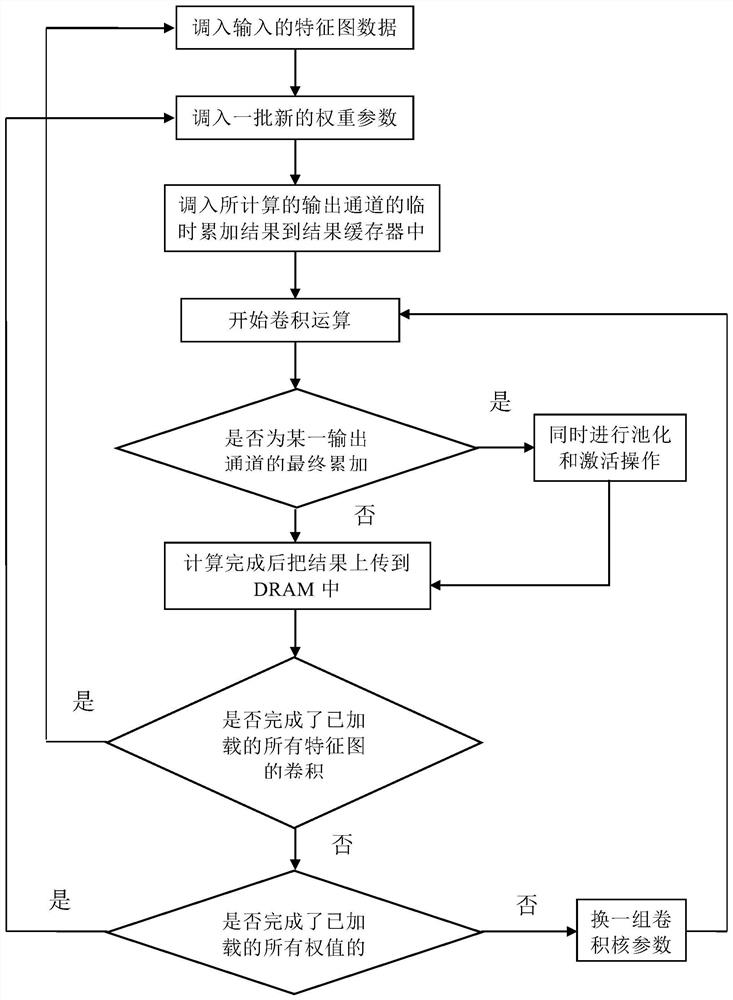

[0040] A kind of FPGA-based YOLO network forward reasoning accelerator design method, described accelerator comprises FPGA chip and DRAM, memory BRAM in the described FPGA chip is as data buffer, and described DRAM is as main storage device, uses ping-pong structure in DRAM ; It is characterized in that, described accelerator design method comprises the following steps:

[0041] (1) Perform 8-bit fixed-point quantization on the original network data to obtain the position of the decimal point that has the least impact on the detection accuracy, and form a quantization scheme. The quantization process is carried out layer by layer;

[0042] (2) The FPGA chip performs parallel computing on YOLO's nine-layer convolutional network;

[0043] (3) Location mapping.

[0044] Specifically, the quantization process of a certain layer in the step (1) is:

[0045] a) Quantify the weight data of the original network: when quantizing according to a certain decimal position of an 8bit fixe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More