Semiconductor structure and forming method

A semiconductor and substrate technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., can solve problems such as semiconductor structure performance needs to be improved, achieve the effect of improving performance, reducing the probability of residual problems, and reducing process difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] It can be seen from the background art that the performance of semiconductor devices still needs to be improved. Combining with a method of forming a semiconductor structure, the reason why its performance needs to be improved is analyzed.

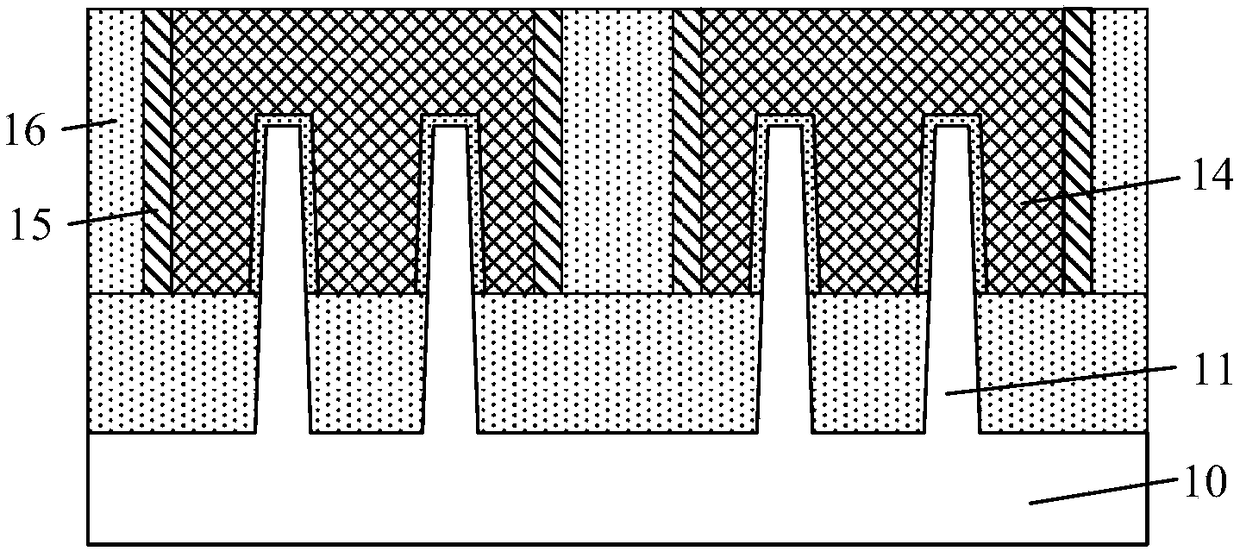

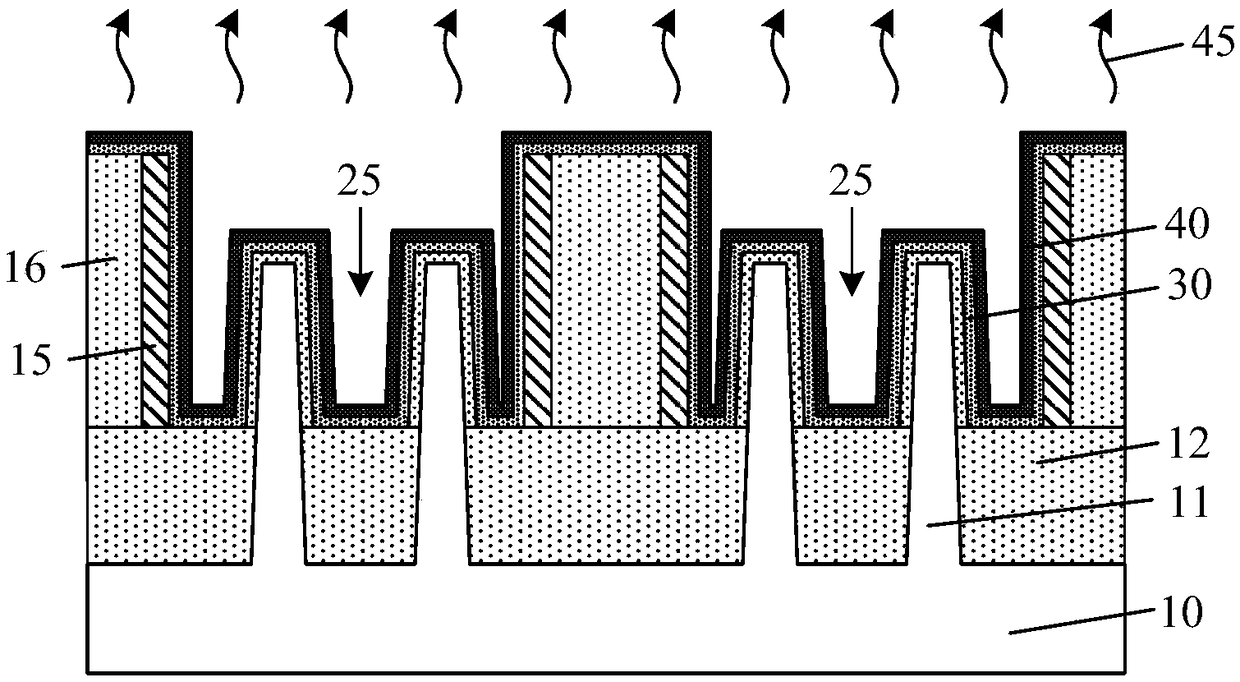

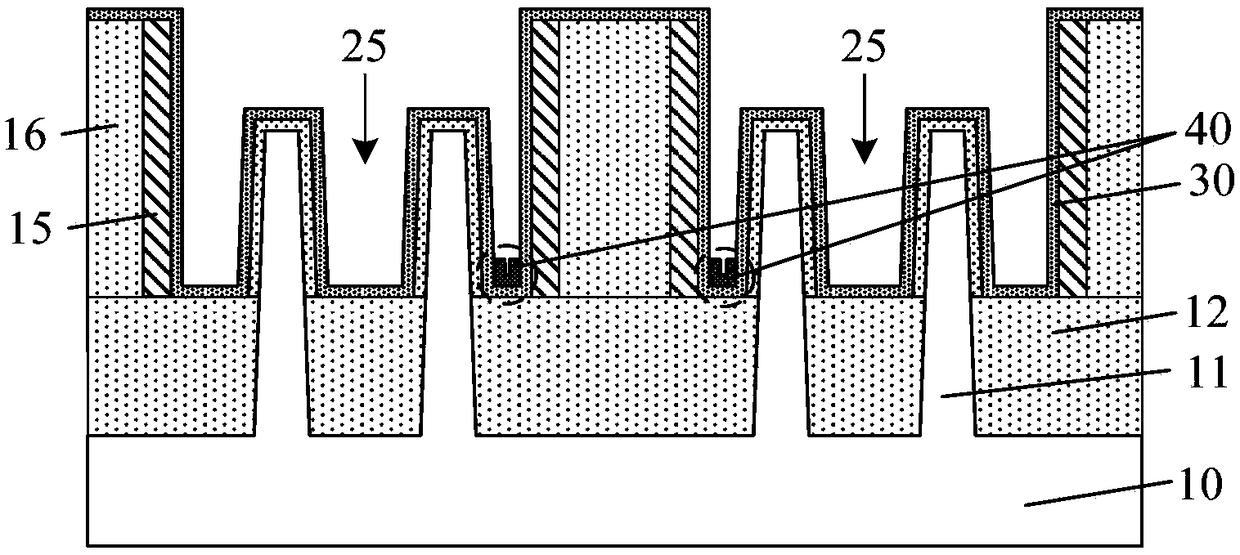

[0019] refer to Figure 1 to Figure 3 , shows a structural schematic diagram corresponding to each step in a method for forming a semiconductor structure.

[0020] refer to figure 1 , providing a base, the base includes a substrate 10 and discrete fins 11 located on the substrate 10; a dummy gate layer 14 across the fins 11 is formed on the base, and the dummy gate layer 14 Covering part of the top and part of the sidewall of the fin 11; a sidewall 15 is formed on the sidewall of the dummy gate layer 14; an interlayer dielectric layer 16 is formed on the exposed base of the dummy gate layer 14, the The interlayer dielectric layer 16 exposes the top of the dummy gate layer 14 .

[0021] refer to figure 2 , remove the dummy gate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More