Multi-epitaxial super-junction terminal structure and manufacturing method thereof

A technology of terminal structure and manufacturing method, applied in electrical components, circuits, semiconductor devices, etc., can solve the problems of high production cost and large area of the terminal area, so as to increase the occupied area, reduce the chip area, and reduce the conduction. The effect of resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

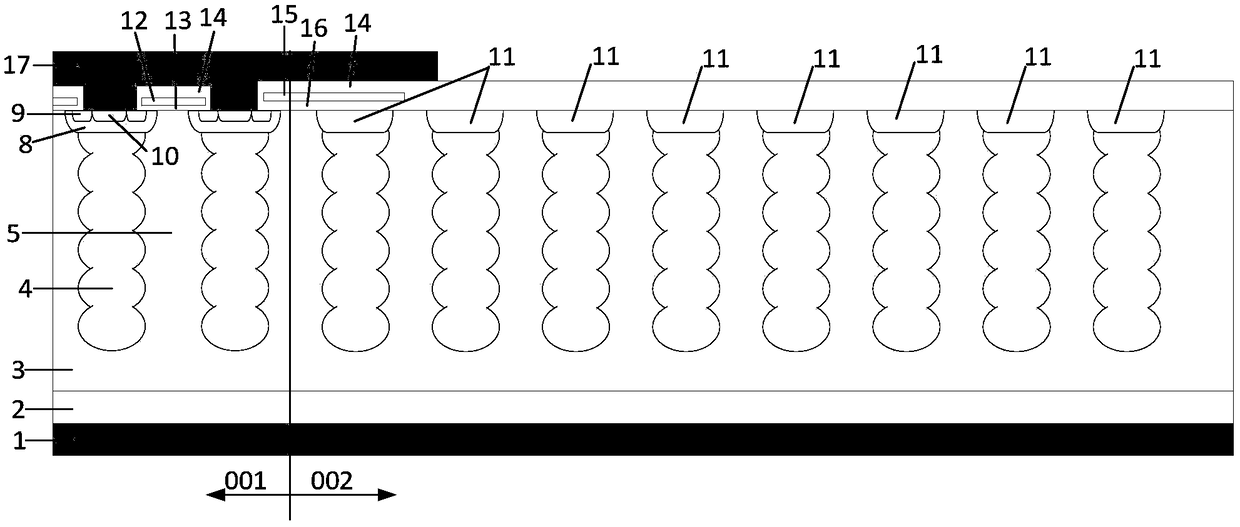

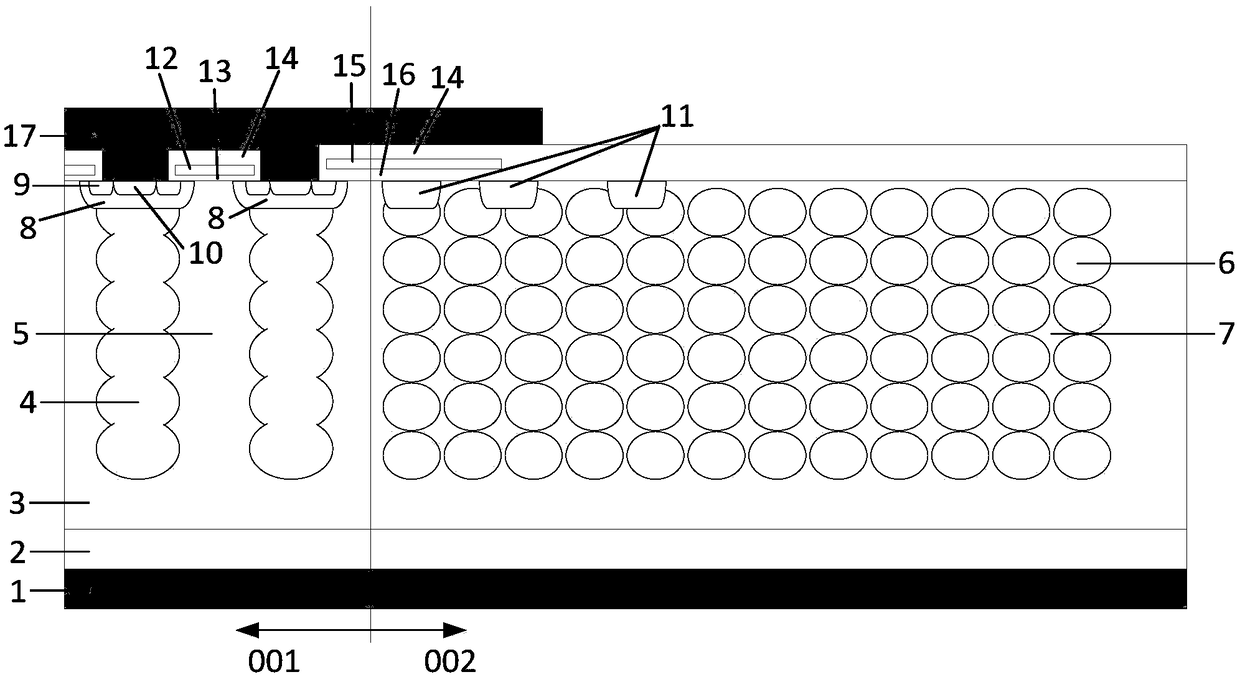

[0049] Embodiment 1: as figure 2 As shown, taking an N-type planar gate DMOS device as an example, the first conductivity type is N-type, and the second conductivity type is P-type. It is a multi-epitaxial super junction terminal structure. On the top view plane, the semiconductor The device includes an active area 001 and a terminal area 002 surrounding the active area 001;

[0050] In cross-sectional view, the terminal region 002 includes a drain metal 1, an N-type substrate 2 on the drain metal 1, and an N-type epitaxial layer 3 on the N-type substrate 2, and the N-type epitaxial layer 3 is provided with a number of P-type circular areas 6 regularly arranged in a ring shape, and adjacent P-type circular areas 6 are adjacent, and N-type areas 7 are provided between adjacent P-type circular areas 6; Three P-type well regions 11 are arranged on the surface of the terminal region 002 close to the active region 001;

[0051] A field oxide layer 16 is provided on the surface o...

Embodiment 2

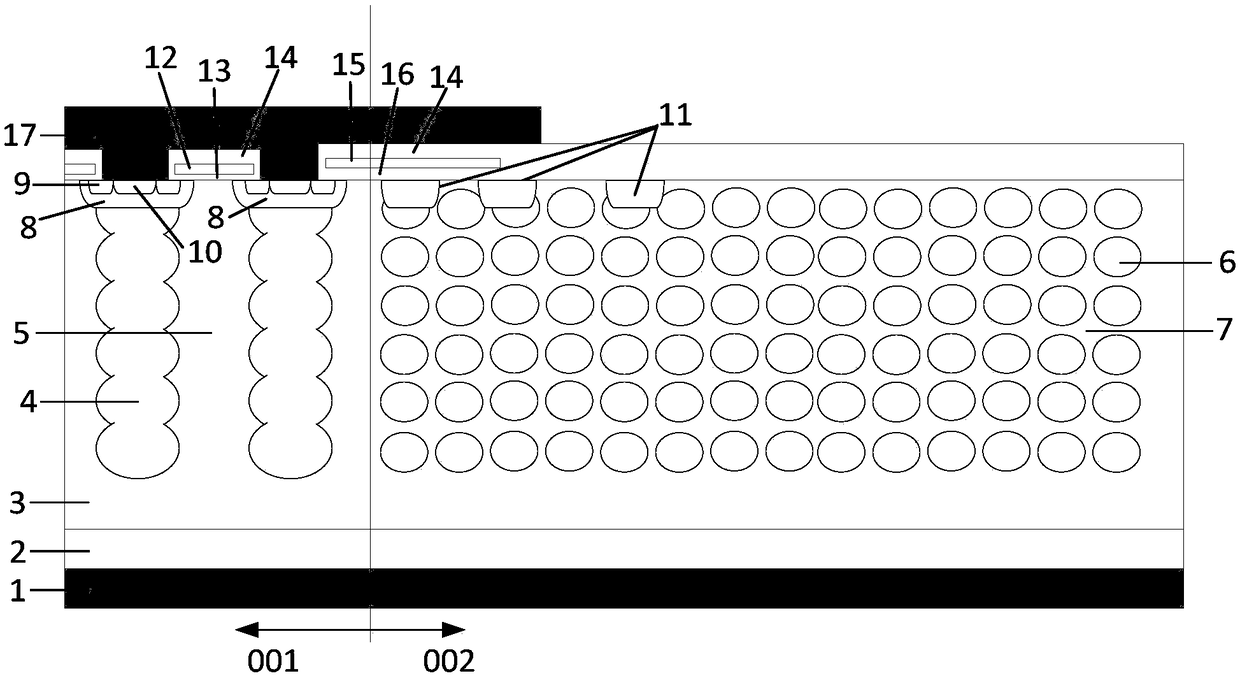

[0068] Embodiment 2: as image 3 As shown, taking an N-type planar gate DMOS device as an example, the first conductivity type is N-type, the second conductivity type is P-type, a super junction terminal structure with multiple epitaxy, and on the cross-sectional section, the The terminal region 002 includes a drain metal 1, an N-type substrate 2 on the drain metal 1, and an N-type epitaxial layer 3 on the N-type substrate 2. The N-type epitaxial layer 3 is provided with several regular rows An annular P-type circular area 6 is arranged, and the adjacent P-type circular areas 6 are spaced apart, and an N-type area 7 is provided between adjacent P-type circular areas 6; near the terminal area 002 there is Three P-type well regions 11 are provided on the surface of the source region 001;

[0069] In this embodiment, the boundaries of the upper and lower adjacent and left and right adjacent P-type circular regions 6 are phase-separated, and the P-type region of the active region...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More