On-chip Network Optimization Method Based on Approximate Computing

A network-on-chip and optimization method technology, which is applied in the direction of data exchange network, digital transmission system, electrical components, etc., can solve the problem of not using the tolerance of the application program

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be further described in detail below in conjunction with the embodiments and the accompanying drawings, but the embodiments of the present invention are not limited thereto.

[0042] see Figure 4 , C represents the processor core in the network on chip node, M represents the processor Cache (cache memory), R represents the router, and NI represents the network interface. The on-chip network optimization method based on approximate calculation of the present invention includes several parts: a flow predictor, a data clipper, a data restorer, a global controller and a local controller. in:

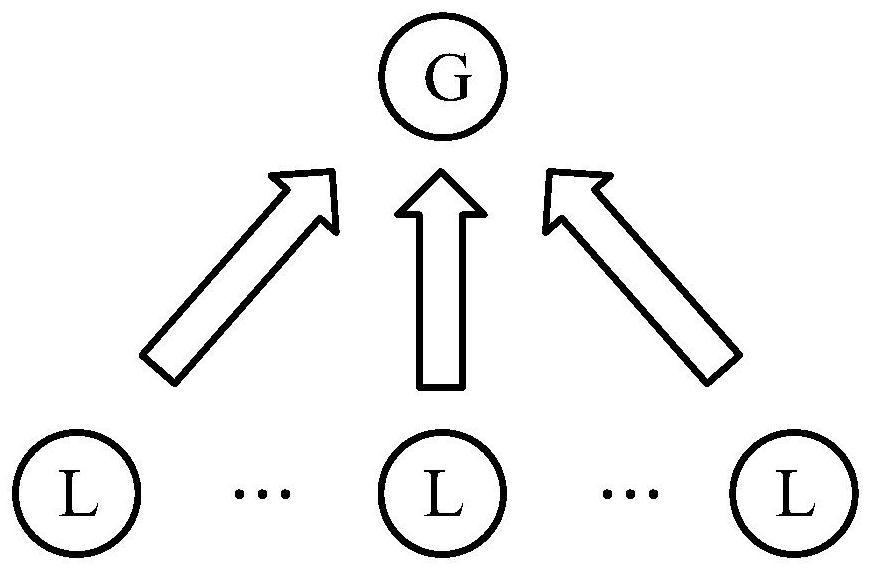

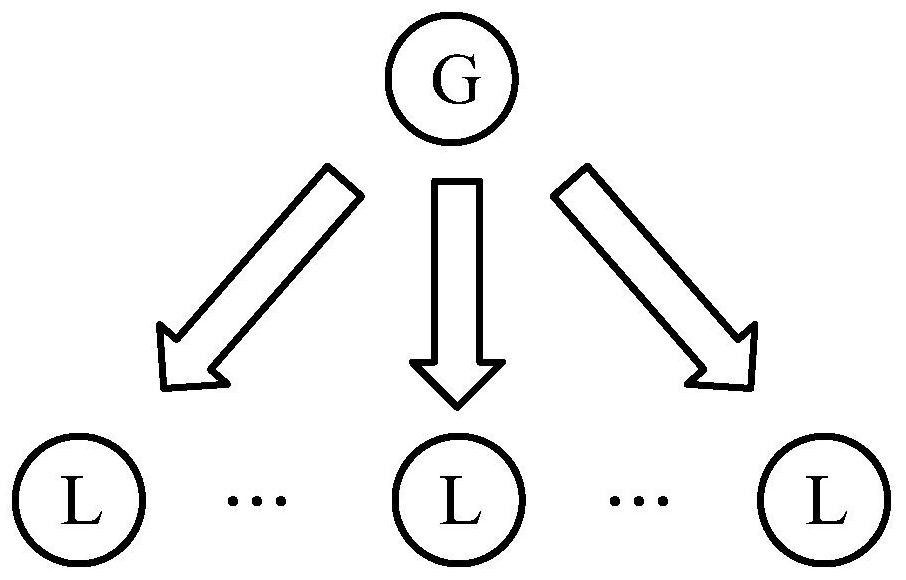

[0043] Such as figure 1 As shown, the traffic predictor runs on each node L, and at the beginning of each regulation interval, according to the past operating conditions of the node, predicts the communication situation of the data flow sent by the node in the interval, and sends it to the master Control node G.

[0044] Each node of the network on chip i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More