A register single event effect analog simulation method for an aerospace chip

A single event effect and simulation technology, applied in design optimization/simulation, instruments, special data processing applications, etc., can solve problems such as single event effect fault injection in space application chips, achieve high authenticity and reliability, and improve efficiency , the effect of improving flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

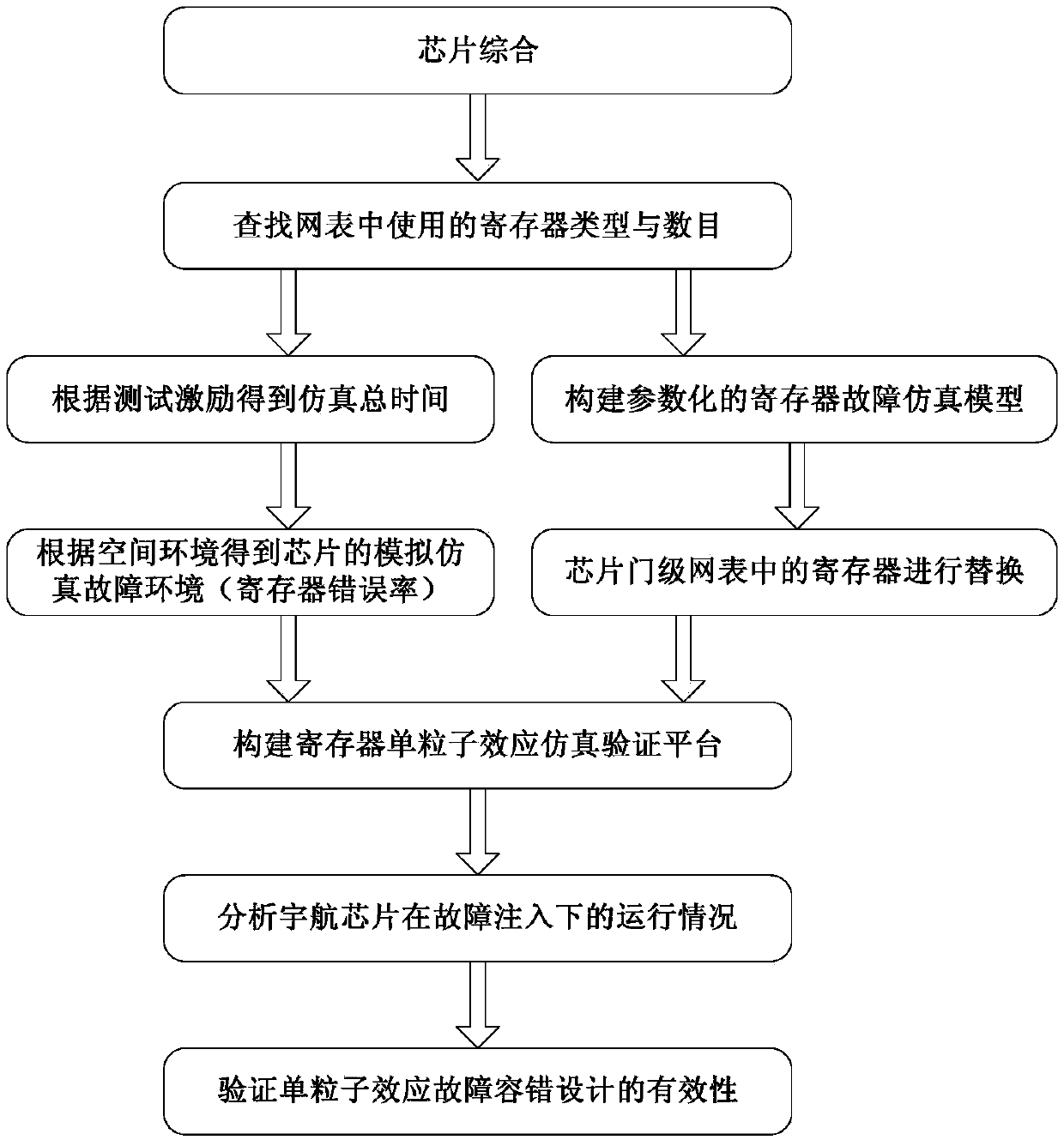

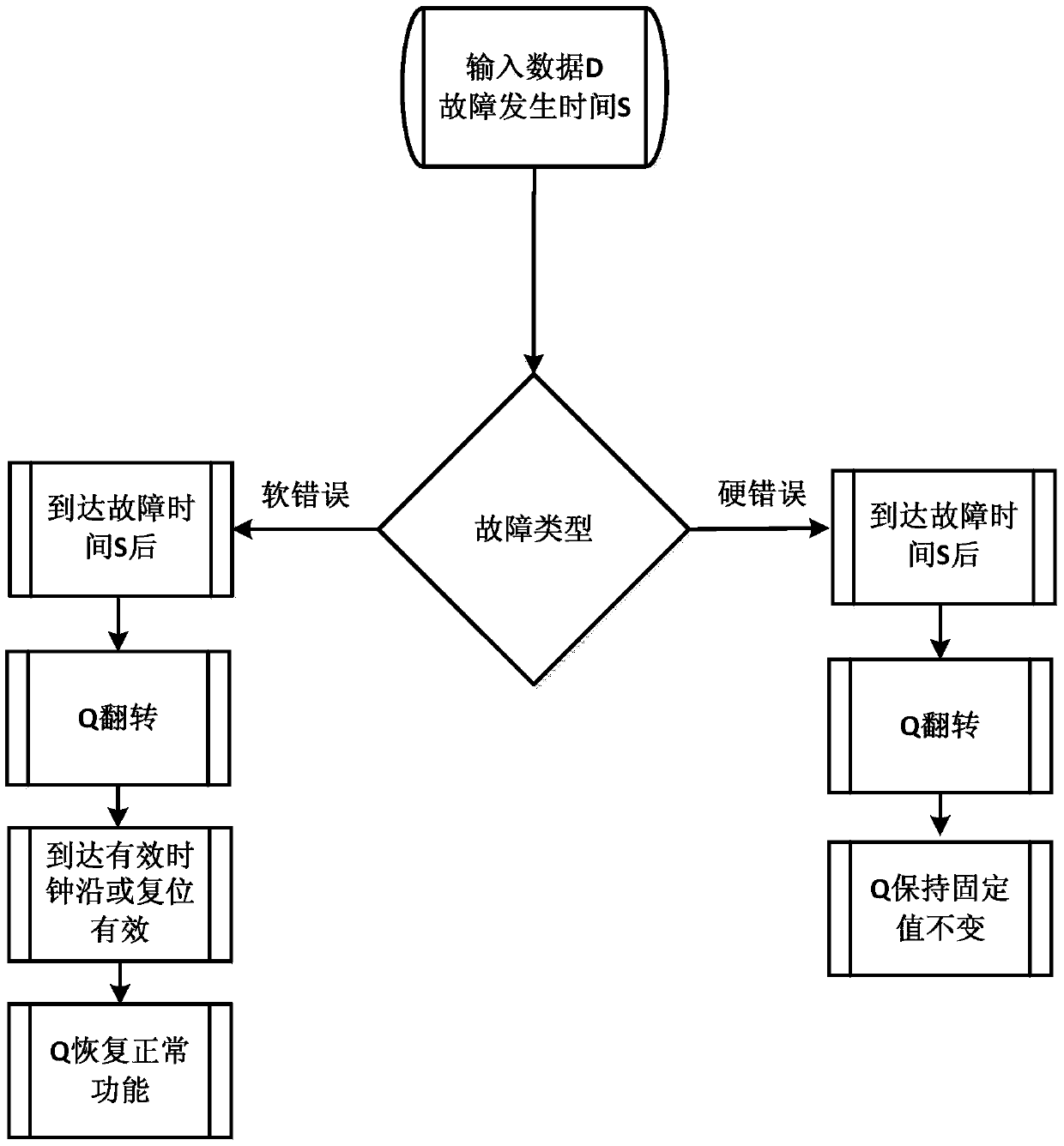

Method used

Image

Examples

Embodiment

[0041] A detailed explanation of a register single event effect simulation method for aerospace chips combined with a specific implementation case (SapceWire protocol chip):

[0042] 1) Based on the SIMC 0.13um process library file, use the Design Compiler tool to design the RTL of the SapceWire protocol chip (hereinafter referred to as the SPW chip) to obtain the gate-level netlist of the SPW chip;

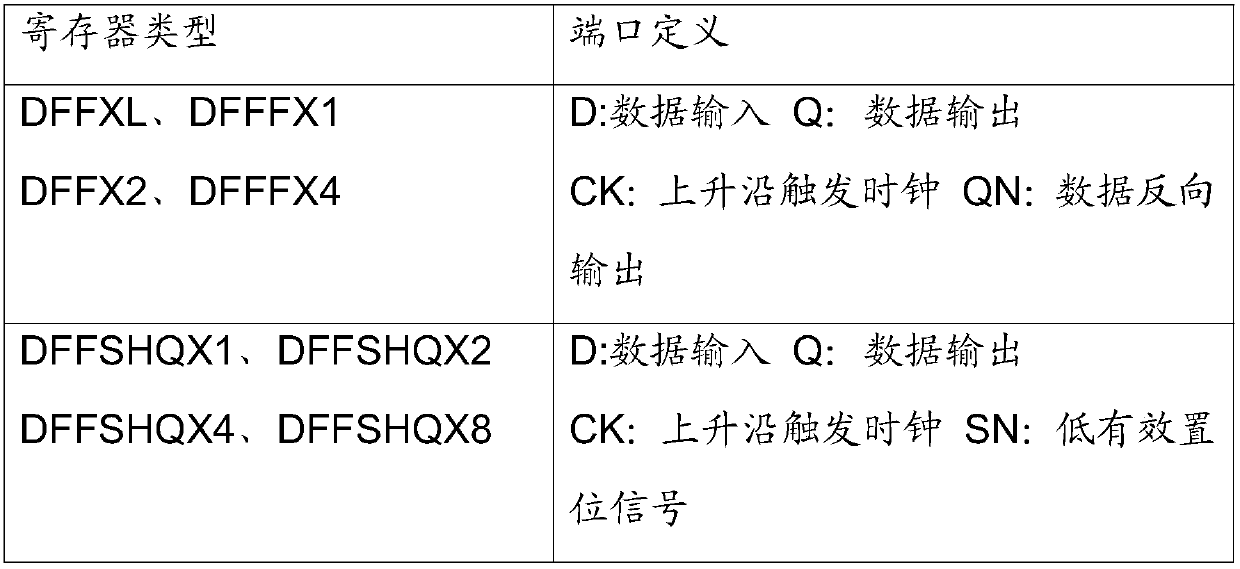

[0043] 2) Based on the data sheet of the SIMC 0.13um process library, the types of all registers of SIMC 0.13um and the definitions of input and output ports are obtained (there are many types of registers, and 2 types of them are listed):

[0044]

[0045] 3) Based on the data manual of the SIMC 0.13um process unit library file, all register types under the process are obtained, and the number of registers used in the SPW chip netlist obtained in step 1) is 138907; and the types used are only Contains DFFSHQX1, DFFSHQX2, DFFSHQX4, DFFSHQX8. There are many register lists, onl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More