Method and system for detection and fault positioning of SoC chip through laser simulation single particle irradiation

A single-particle irradiation, fault location technology, applied in electronic circuit testing, electrical measurement, measuring devices, etc., can solve problems such as unfavorable chip flip characteristics, large chip flip cross-section, large laser spot, etc., to prevent the impact of test results. , high coverage, rich experimental conditions and effects of methods

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

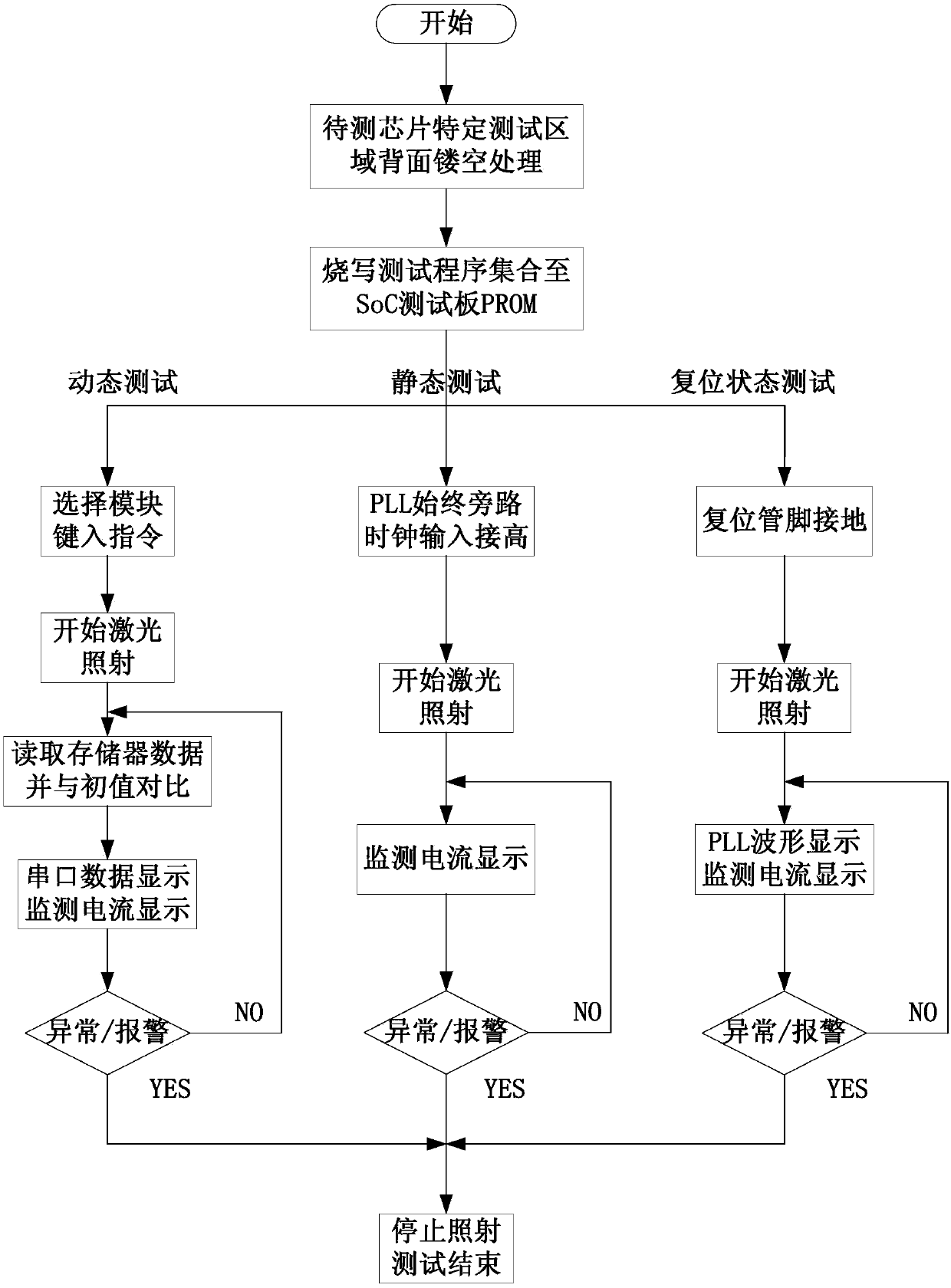

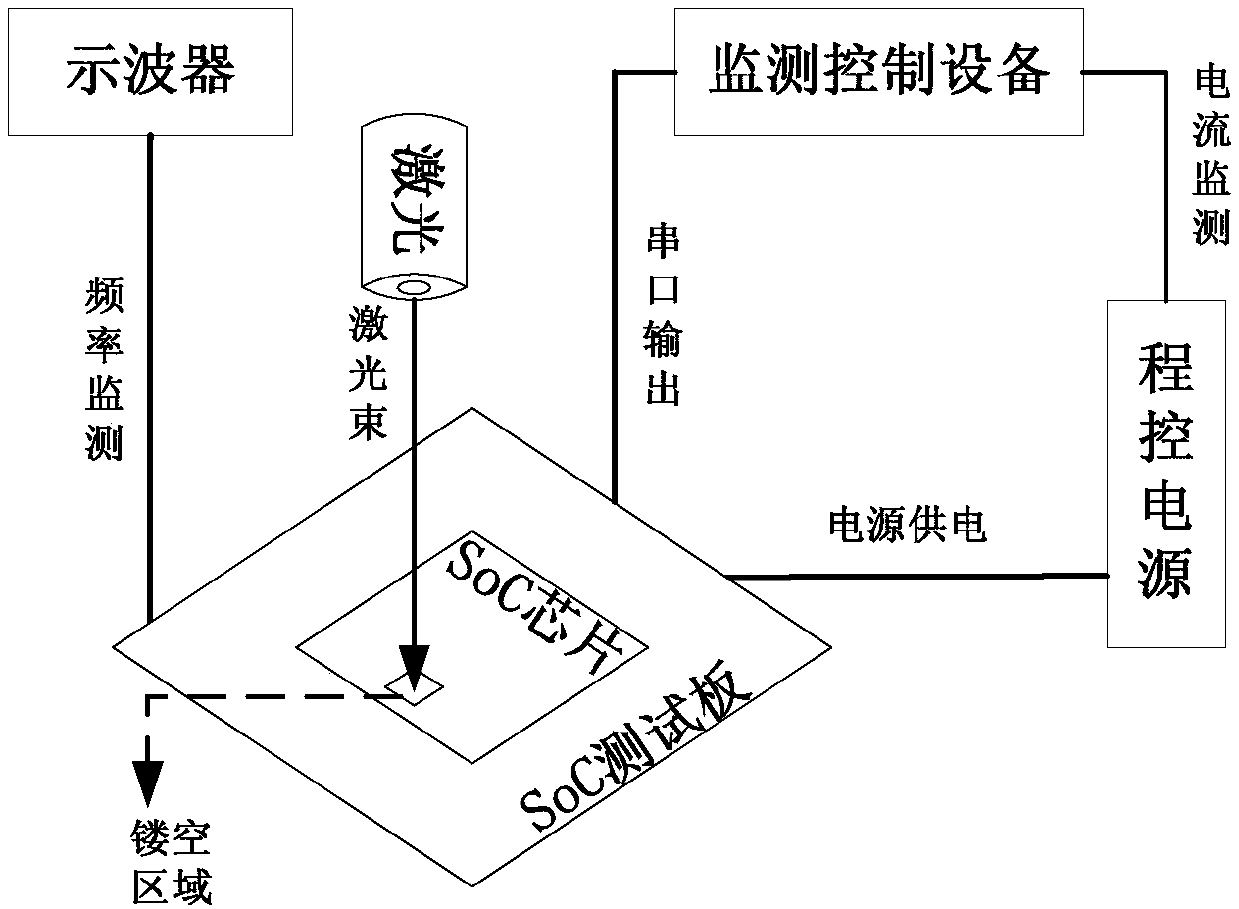

[0059] Such as figure 1 As shown, in view of the technical difficulties of laser simulation single event effect testing in the prior art, the present invention proposes a SoC chip laser simulation single event radiation detection and fault location method, including reset mode, static mode and dynamic mode three test modes, The specific steps for each mode are as follows:

[0060] 1. Steps in reset mode:

[0061] (1-1), the back side of the SoC chip area to be tested is opened to expose the chip substrate;

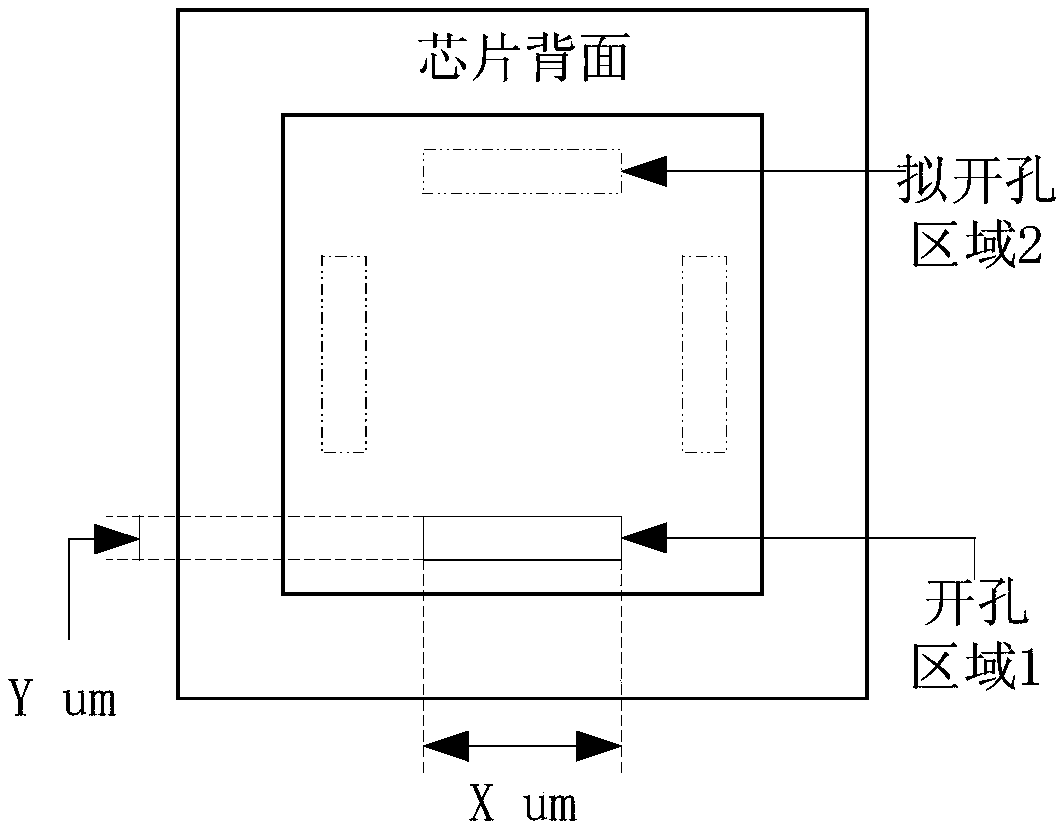

[0062] The maximum scanning speed of the selected laser is 100um / s. In order to reduce the impact of the laser on the non-test area due to the hole opening process error, the hole opening accuracy is preferably controlled within 100um. When the area to be tested affects die bonding, the area to be tested can be divided into multiple sub-areas, and multiple SOC chip tests are performed on each sub-area to obtain test results. Such as figure 1 As shown, when the area to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More