IES combined FPGA hardware simulation acceleration system

A technology to accelerate system and hardware simulation, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as limiting simulation, accelerating application scenarios, complex hardware structure, etc., to achieve accurate simulation time, reduce operating burden, Fast read effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

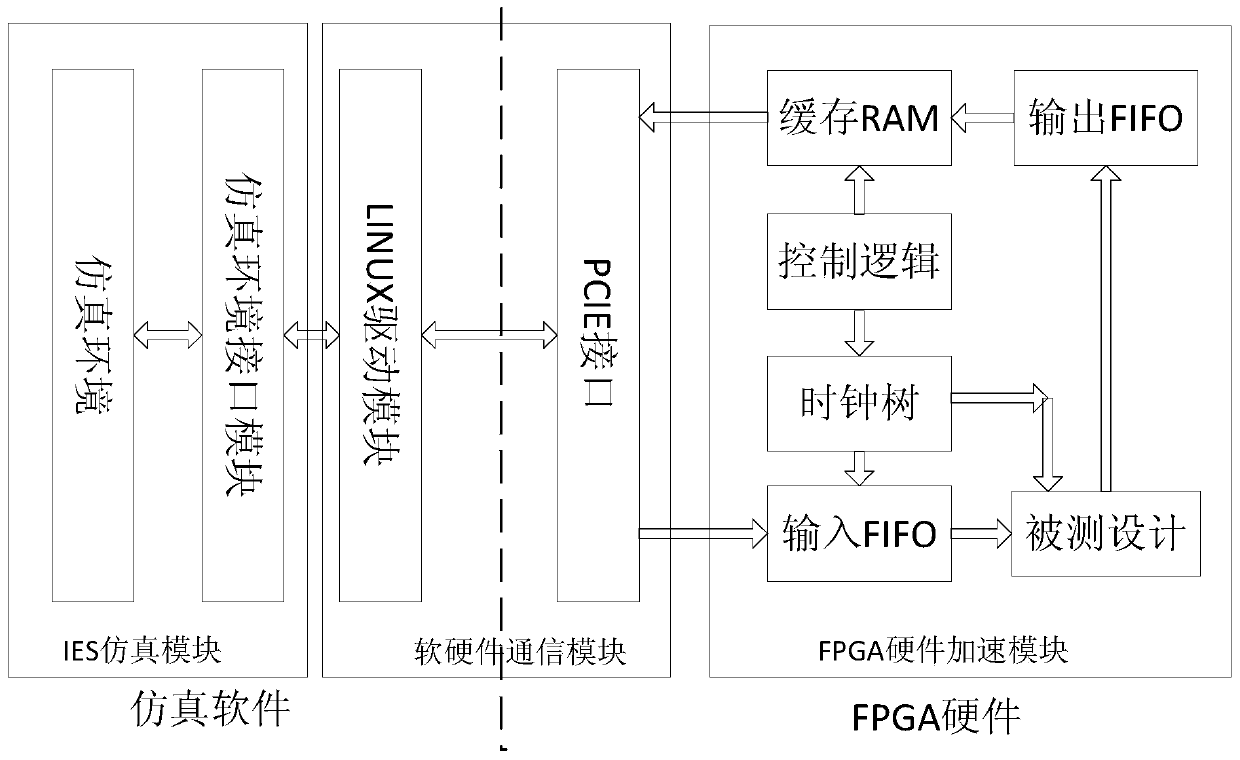

[0064] Such as figure 1 As shown, a certain embodiment of the present invention is divided into three parts, which are respectively IES simulation module, software and hardware communication module and FPGA hardware acceleration module. The IES simulation module writes stimulus data to the FPGA hardware acceleration module through the software and hardware communication module based on the SystemVerilog simulation environment; the FPGA hardware acceleration module processes the FPGA design, and the simulation environment obtains test results and completes a frame of data simulation. Repeatedly, the stimulus data rate input to the design under test corresponds to the least common multiple rate of the combed clock tree, and the data rate output to the simulation environment also corresponds to the least common multiple rate. Through this scheme, the simulation time can be precisely controlled and the waveform display can be realized directly by the simulation software.

[0065]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More