Memory array structure, preparation method thereof, memory, write-in method and read-out method

A storage array and storage technology, applied in the field of storage, can solve the problems of high energy consumption, high operating voltage, and difficult storage, and achieve the effects of simplifying the preparation process, reducing the number of etching times, and reducing the manufacturing cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

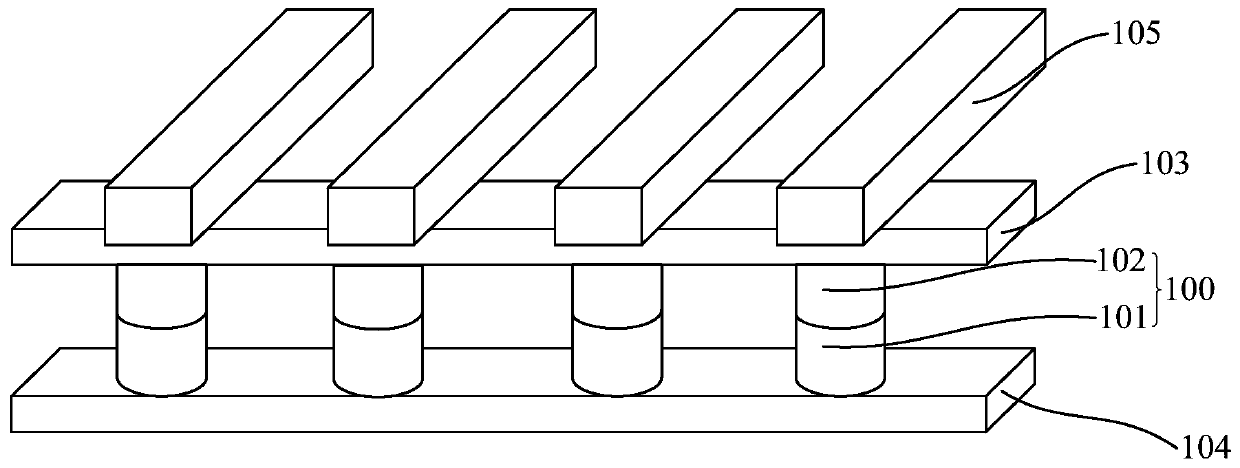

[0085] Such as figure 1 As shown, the present invention provides a storage array structure, and the storage array structure includes:

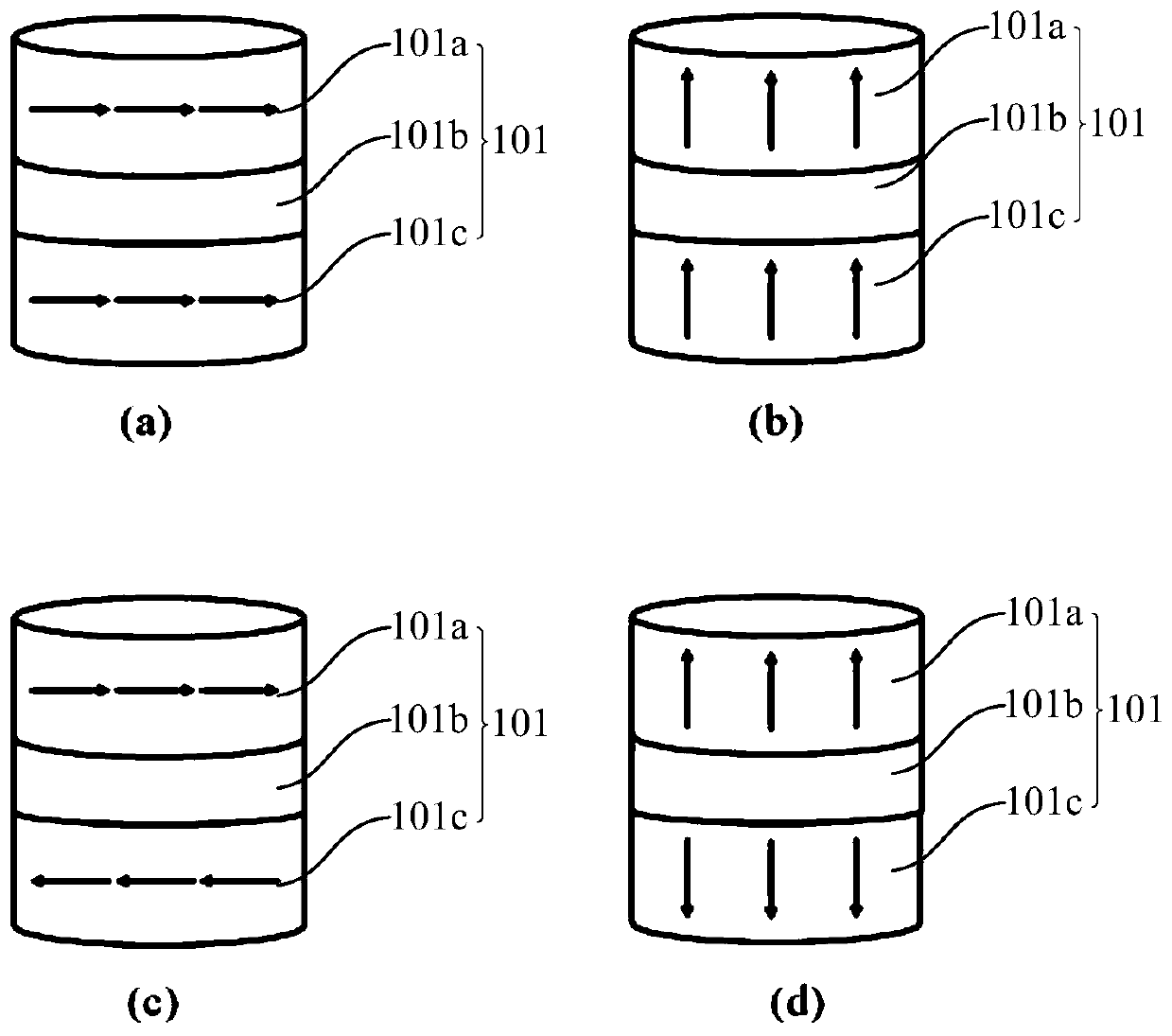

[0086] At least one storage unit 100, the storage unit 100 includes a stacked magnetic storage device 101 and a superconducting device 102, and the magnetic storage device 101 and the superconducting device 102 are arranged in series;

[0087] At least one superconducting upper electrode 103, the superconducting upper electrode 103 is arranged above the storage unit 100, and is electrically connected to the corresponding storage unit 100, when there are at least two superconducting upper electrodes 103, There is no contact between the superconducting upper electrodes 103;

[0088] At least one superconducting lower electrode 104, the superconducting lower electrode 104 is arranged under the storage unit 100, and is electrically connected to the corresponding storage unit 100, when there are at least two superconducting lower electrodes 104, ...

Embodiment 2

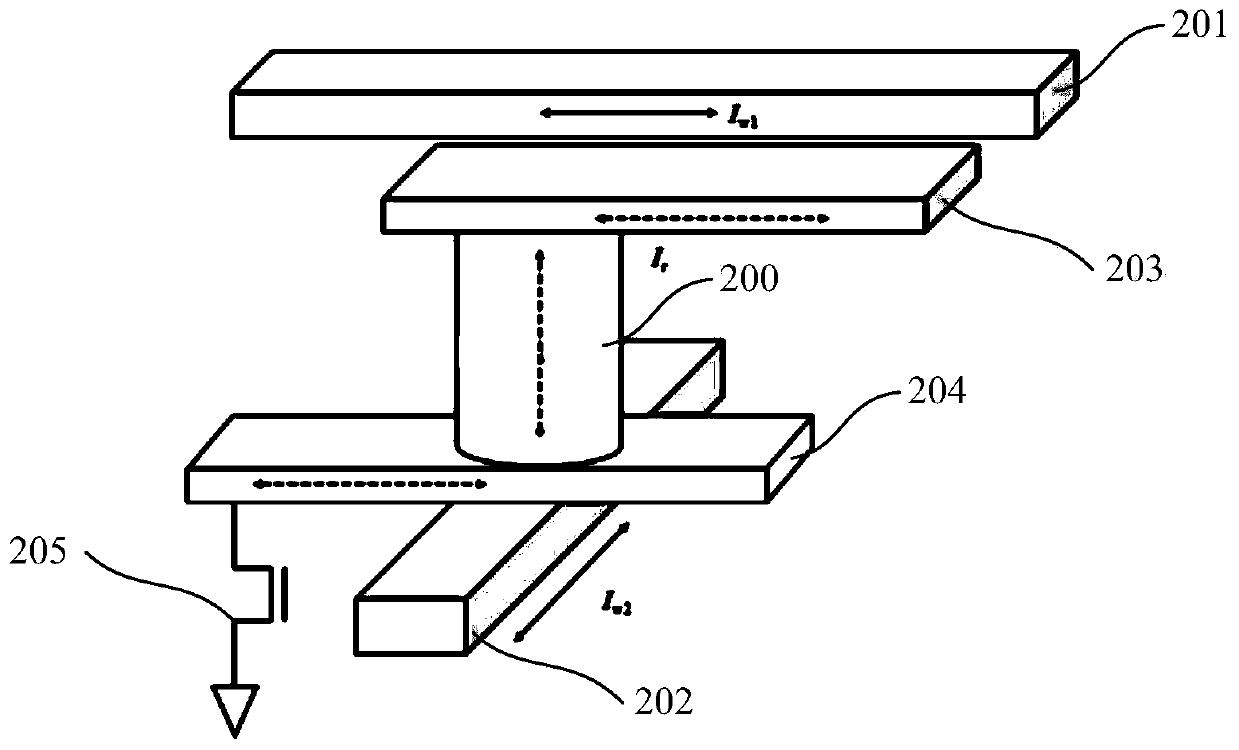

[0128] Such as Figure 8 As shown, the present invention also provides a memory array structure. The difference between the array structure of this embodiment and Embodiment 1 is that the memory array structure further includes at least one superconducting write bit line 106, and the superconducting The guide write bit line 106 is arranged above or below the memory cell 100, and is arranged to cross correspondingly with the corresponding superconducting word line 105, and the superconducting write bit line 106 and the superconducting word line 105. The superconducting write bit line 106 and the superconducting upper electrode 103, the superconducting writing bit line 106 and the superconducting lower electrode 104, and the superconducting writing bit line 106 and the storage unit 100 There is a gap between them, wherein, when there are at least two superconducting write bit lines 106, there is no contact between each of the superconducting write bit lines 106, and other struct...

Embodiment 3

[0136] The present invention also provides a memory, wherein the memory includes the memory array structure described in any one of the above embodiments, wherein the superconducting upper electrode 103 and the superconducting lower electrode 104 serve as the the bit line. In this embodiment, in addition to the device structures and connections described in the above embodiments in the memory, the superconducting device in each of the storage units is arranged in series with the magnetic storage device. The superconducting upper electrode and the superconducting lower electrode are arranged in parallel between the memory cells to form a memory array. The structures and connections of other necessary device structures constituting the memory and the structure of the memory array are well known in the art and will not be repeated here.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com