Patents

Literature

31results about How to "Reduce the number of etch" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

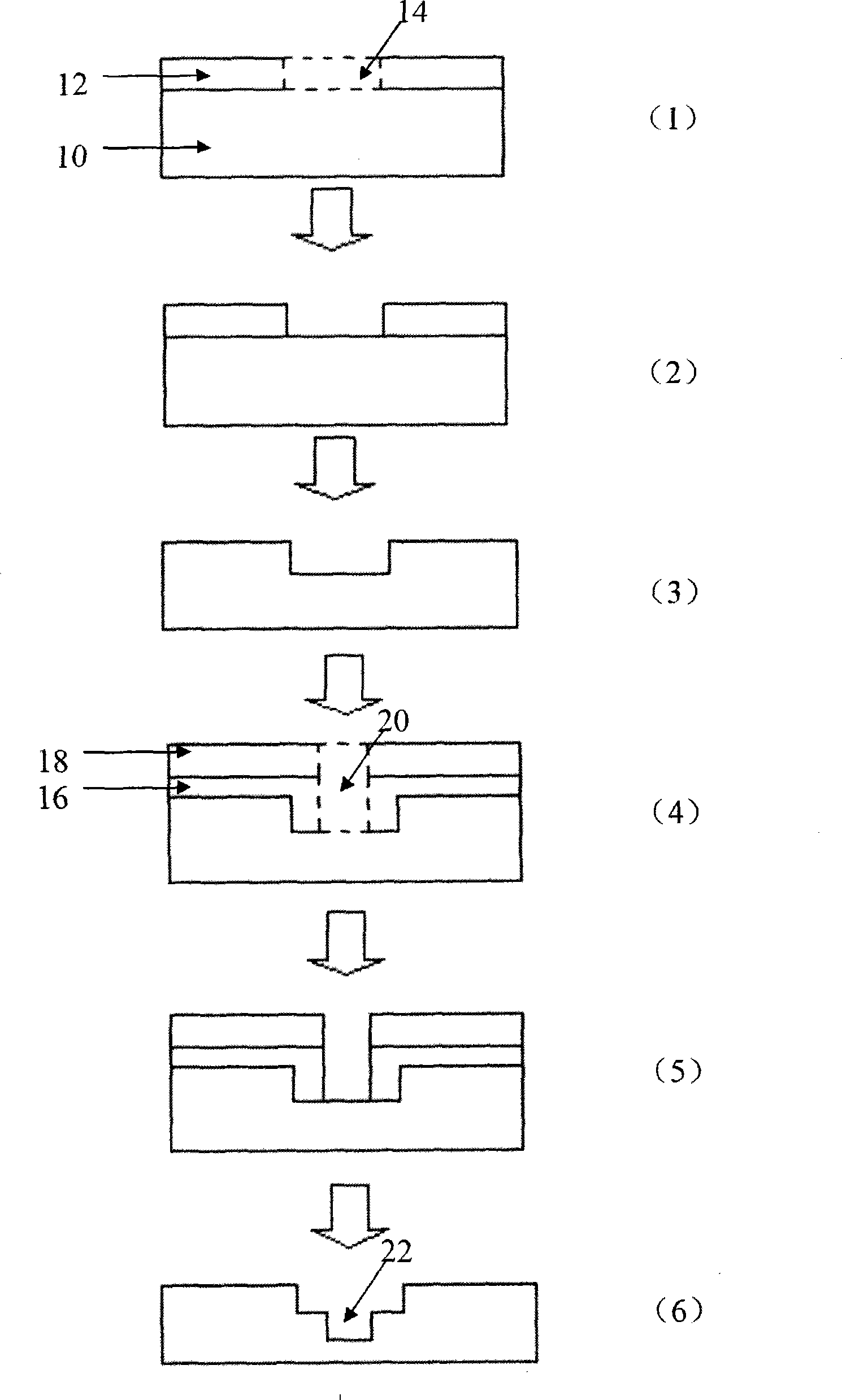

Process for Damascus

ActiveCN101546727AReduce developmentReduce the number of etchSemiconductor/solid-state device manufacturingInter layerMedia layer

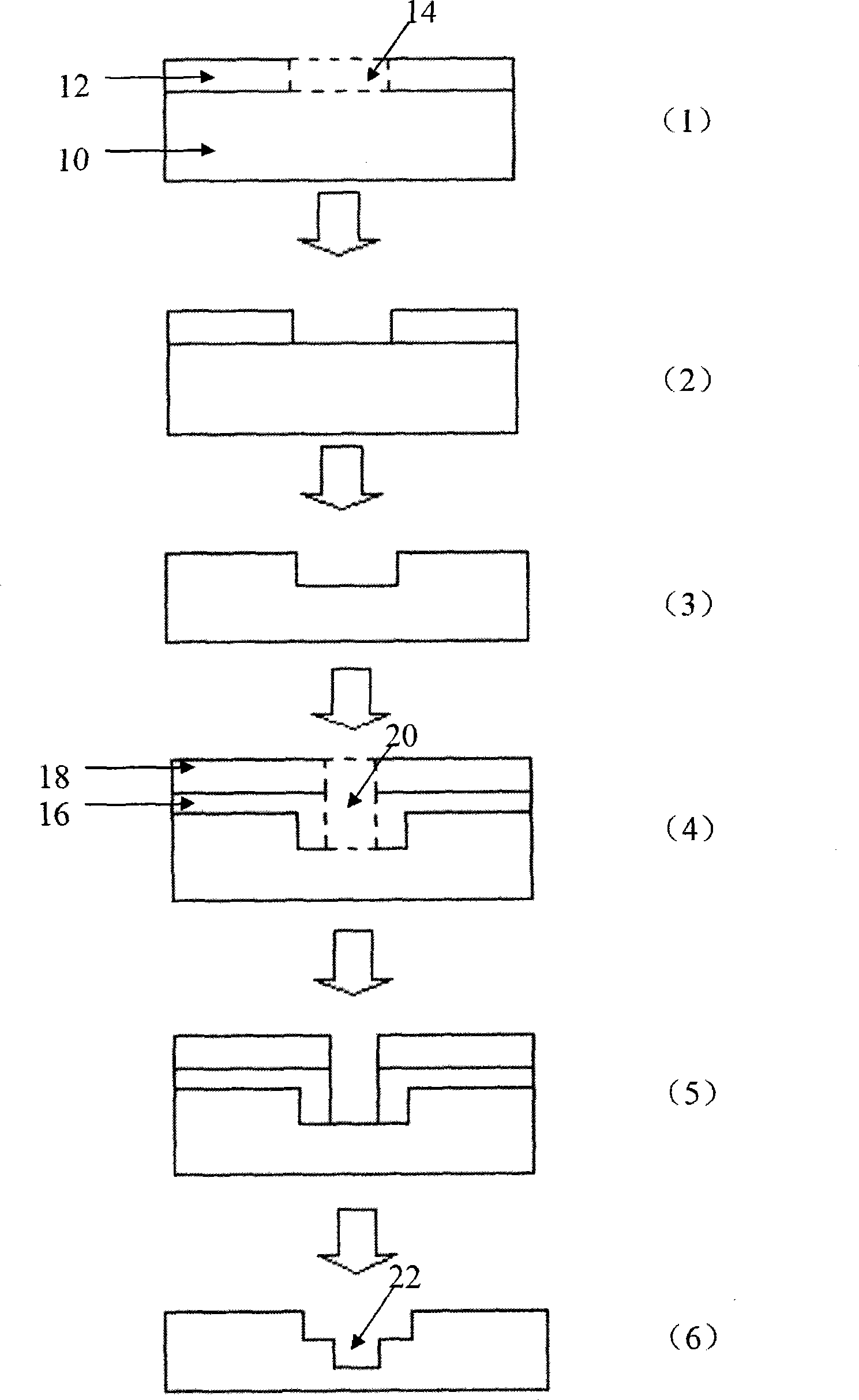

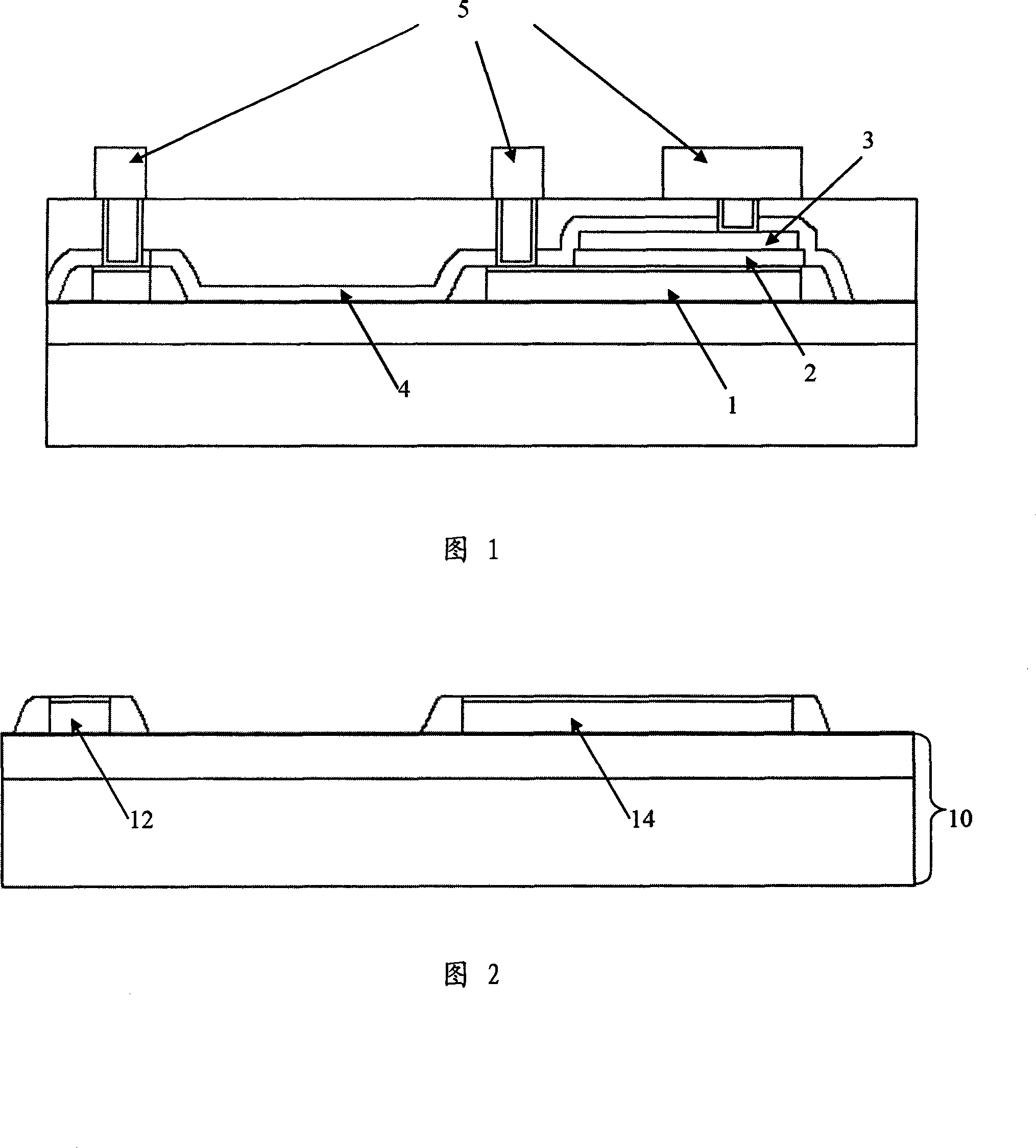

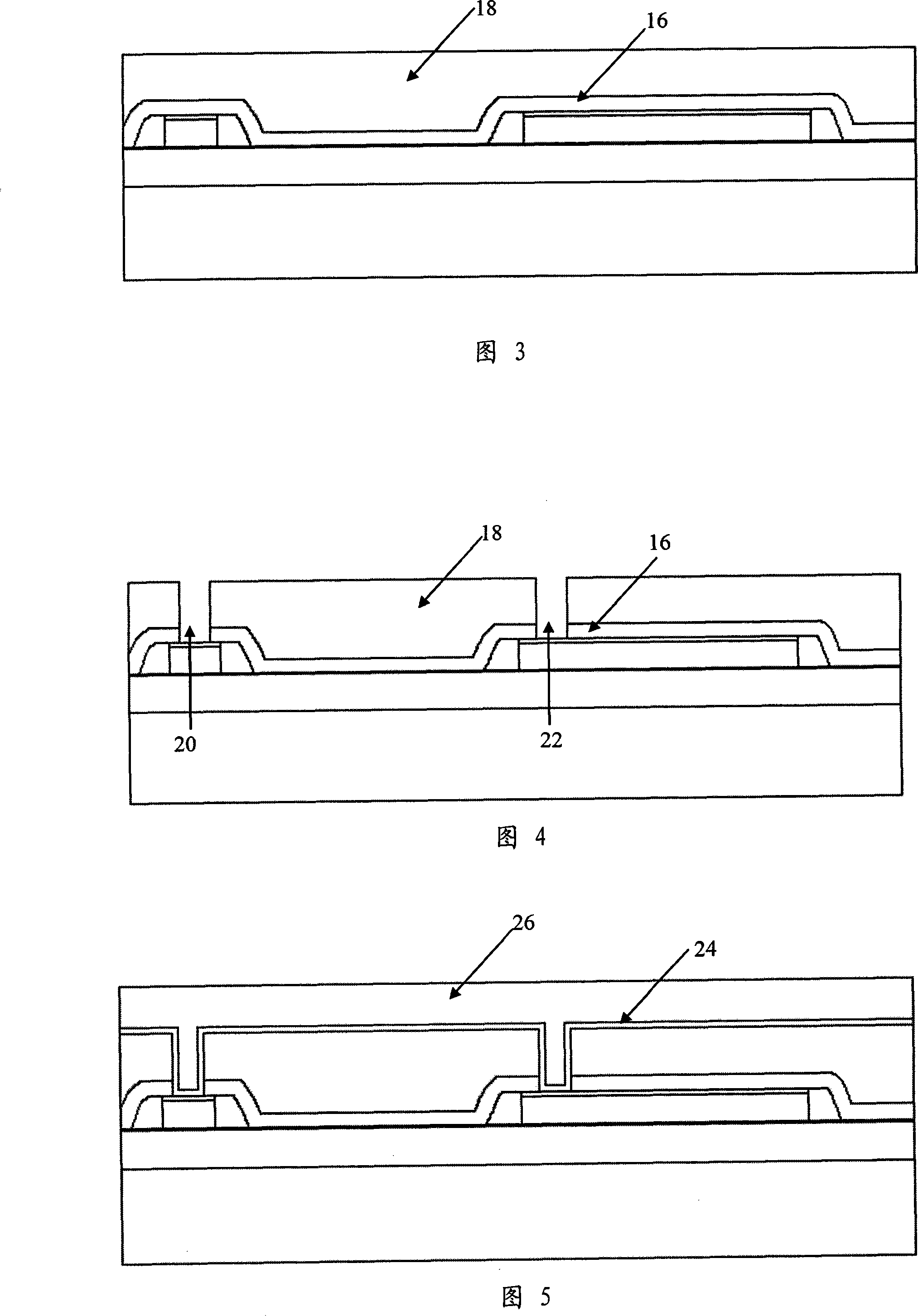

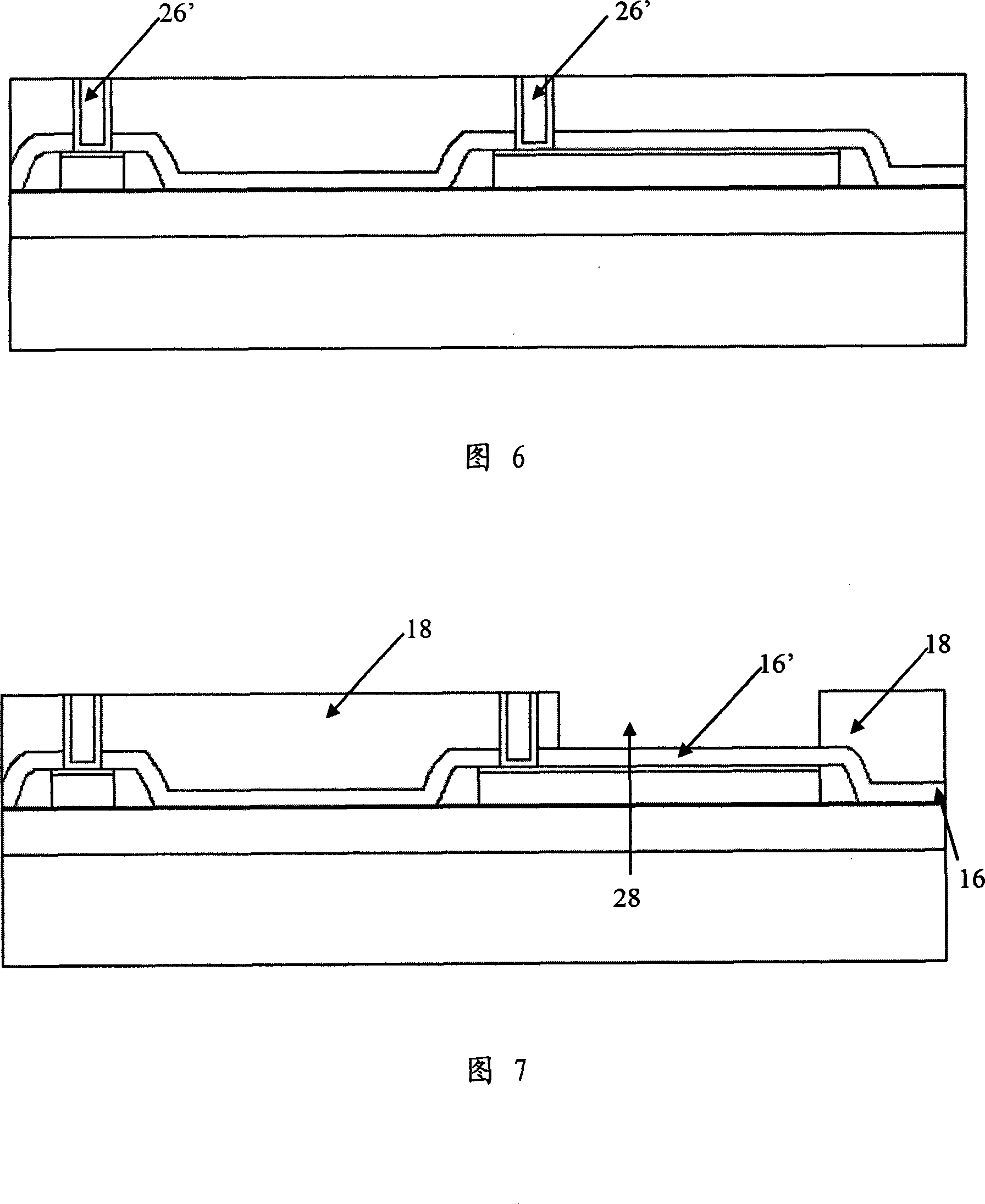

The invention discloses a process for Damascus, which can reduce the times of the development and etching in the process of forming grooves or inter-layered through holes on a substrate. The process comprises the following steps: (1) continuously carrying out exposure processing on a plurality of photoresist layers without development processing so as to form an exposure area; (2) carrying out the development processing on the exposure area so as to obtain a development area corresponding to the exposure area; and (3) etching a medium layer through the development area to form the required grooves or through holes. The process carries out the development and etching for one time on the exposure area obtained after multiple times of the exposure processing so as to obtain the required grooves or the through holes. Compared the prior art, the process centralizes to complete the development processing after each time of exposure processing at a time, thereby reducing the times of the development and etching and improving the efficiency.

Owner:SEMICON MFG INT (SHANGHAI) CORP

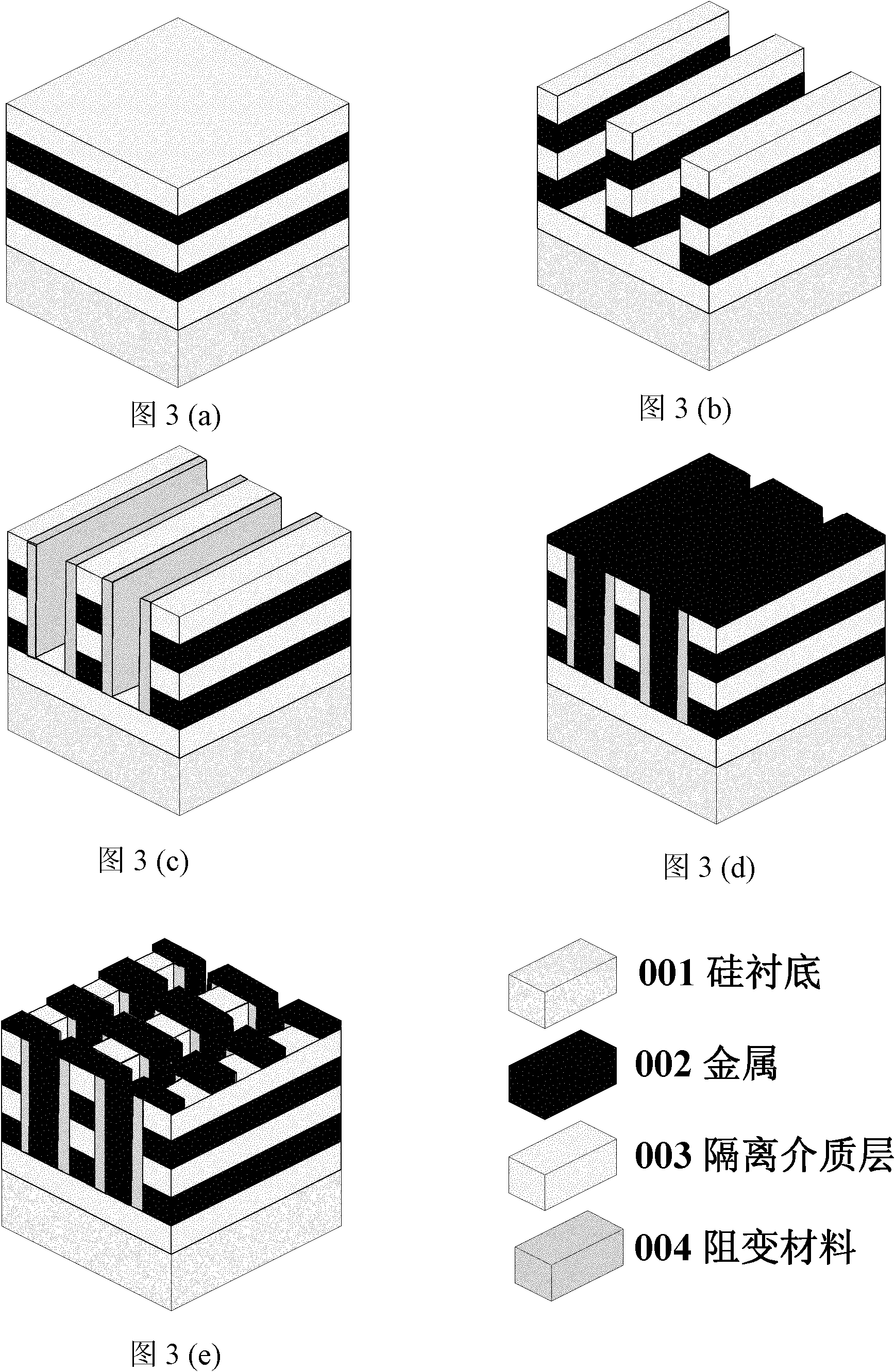

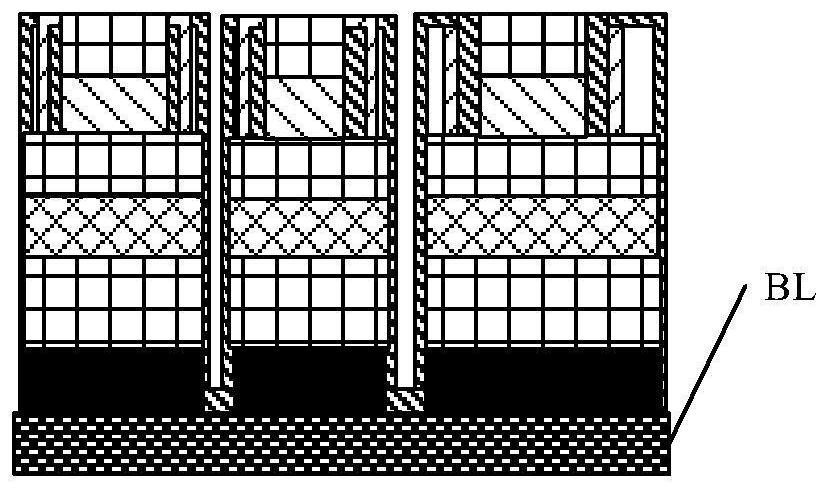

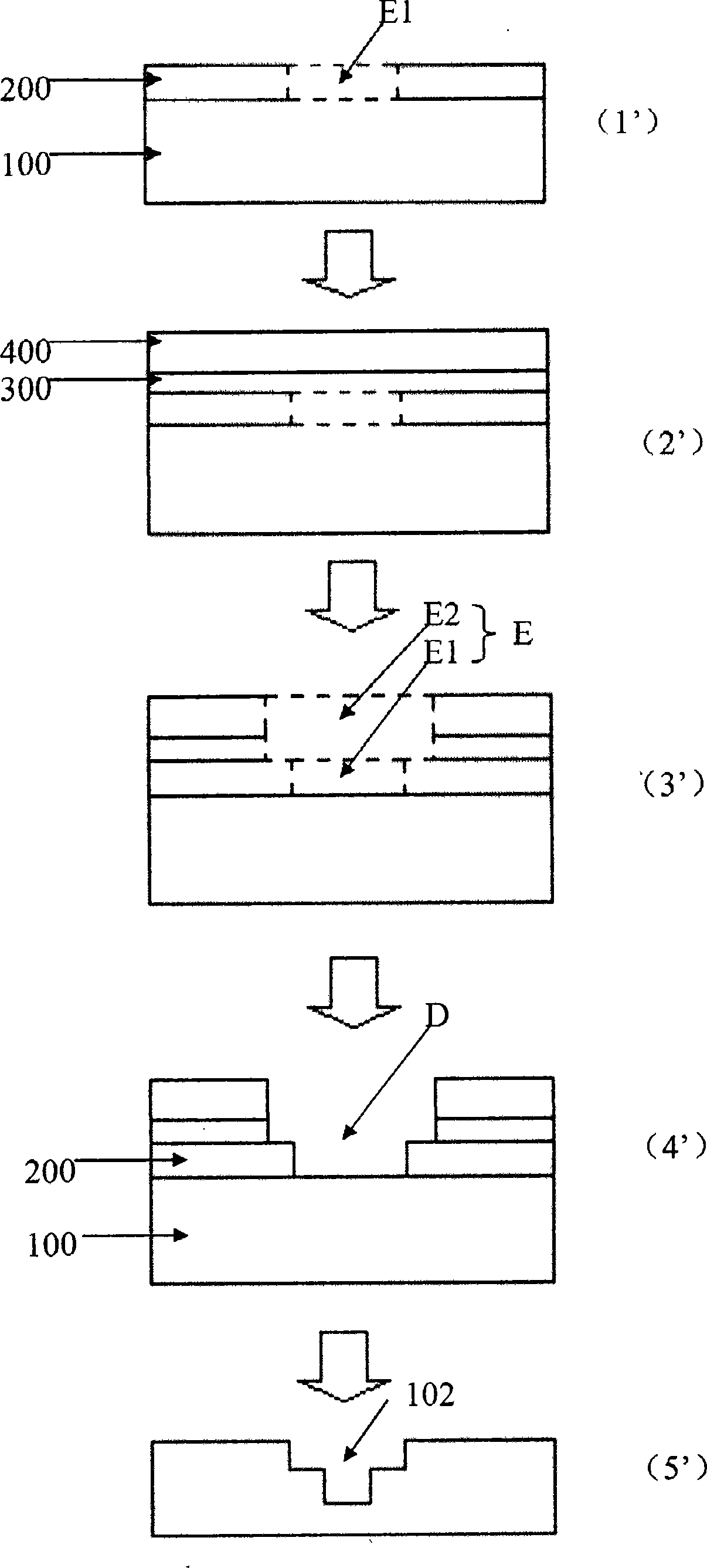

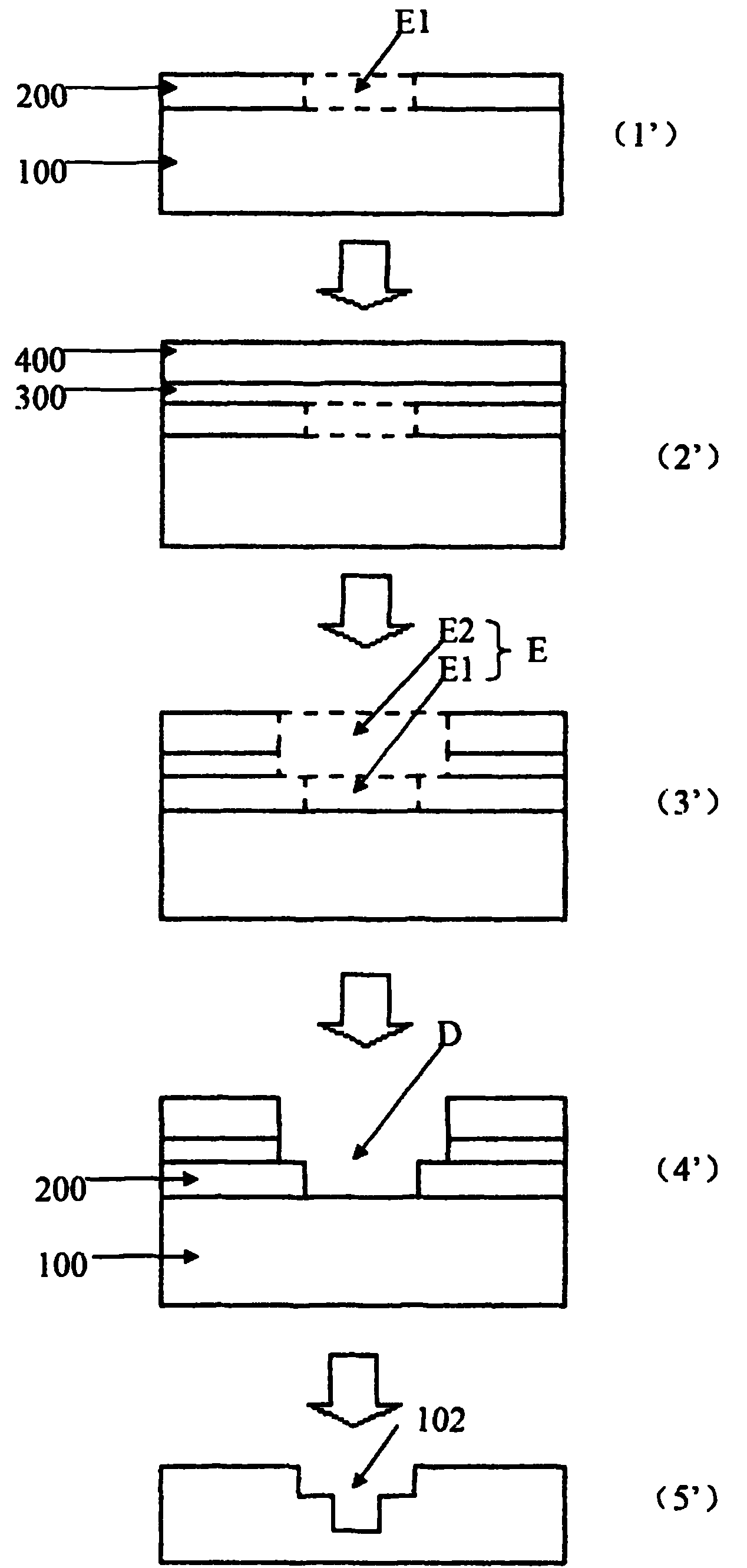

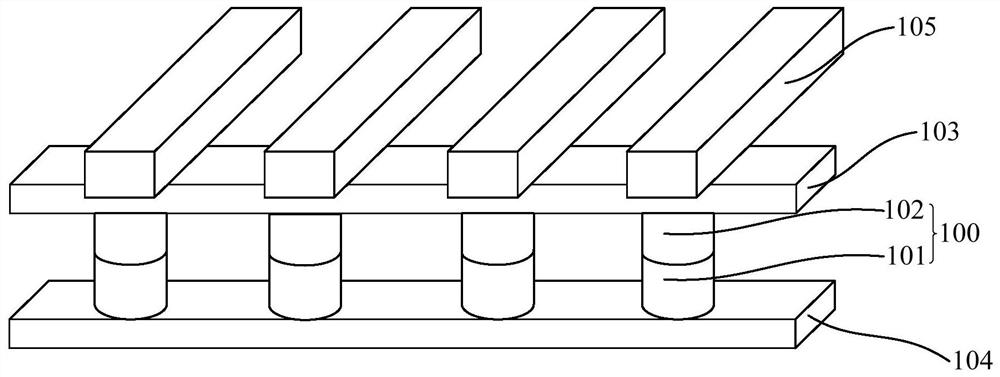

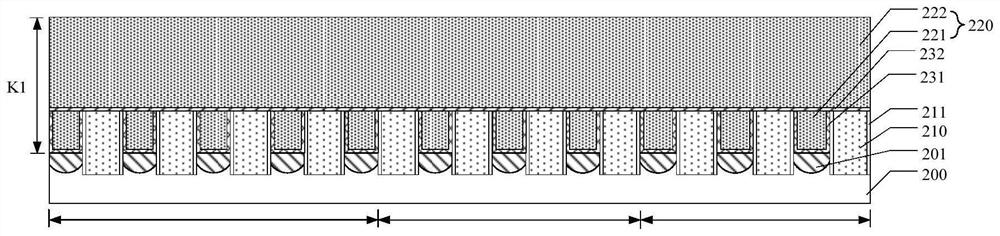

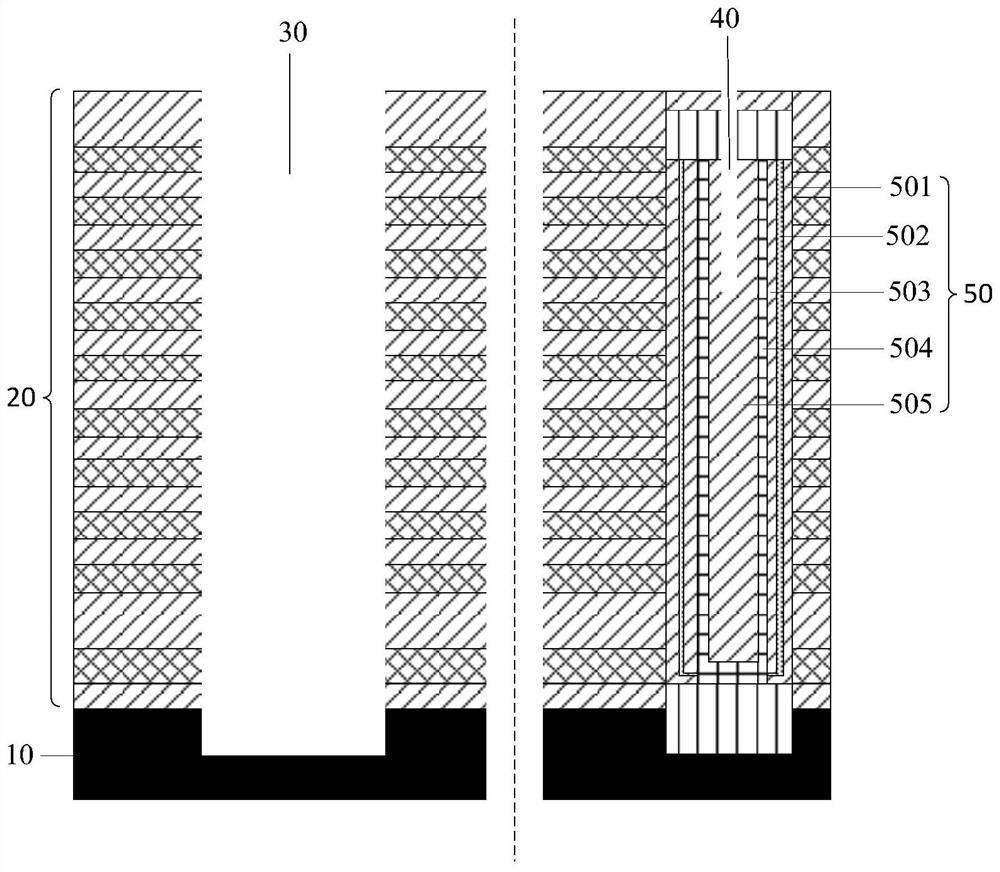

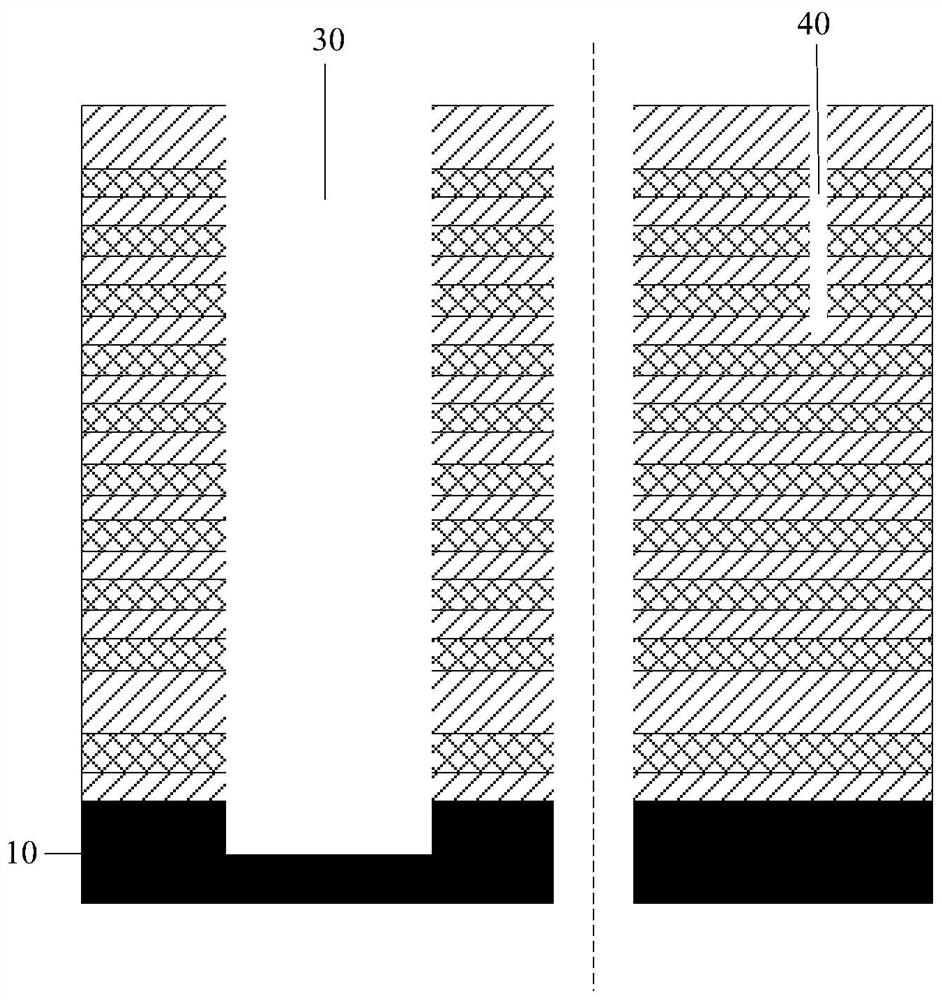

Three-dimensional nonvolatile memory array and preparation method thereof

InactiveCN101976676ASmall sizeReduce photolithography processSolid-state devicesSemiconductor devicesVery large scale integrated circuitsManufacturing technology

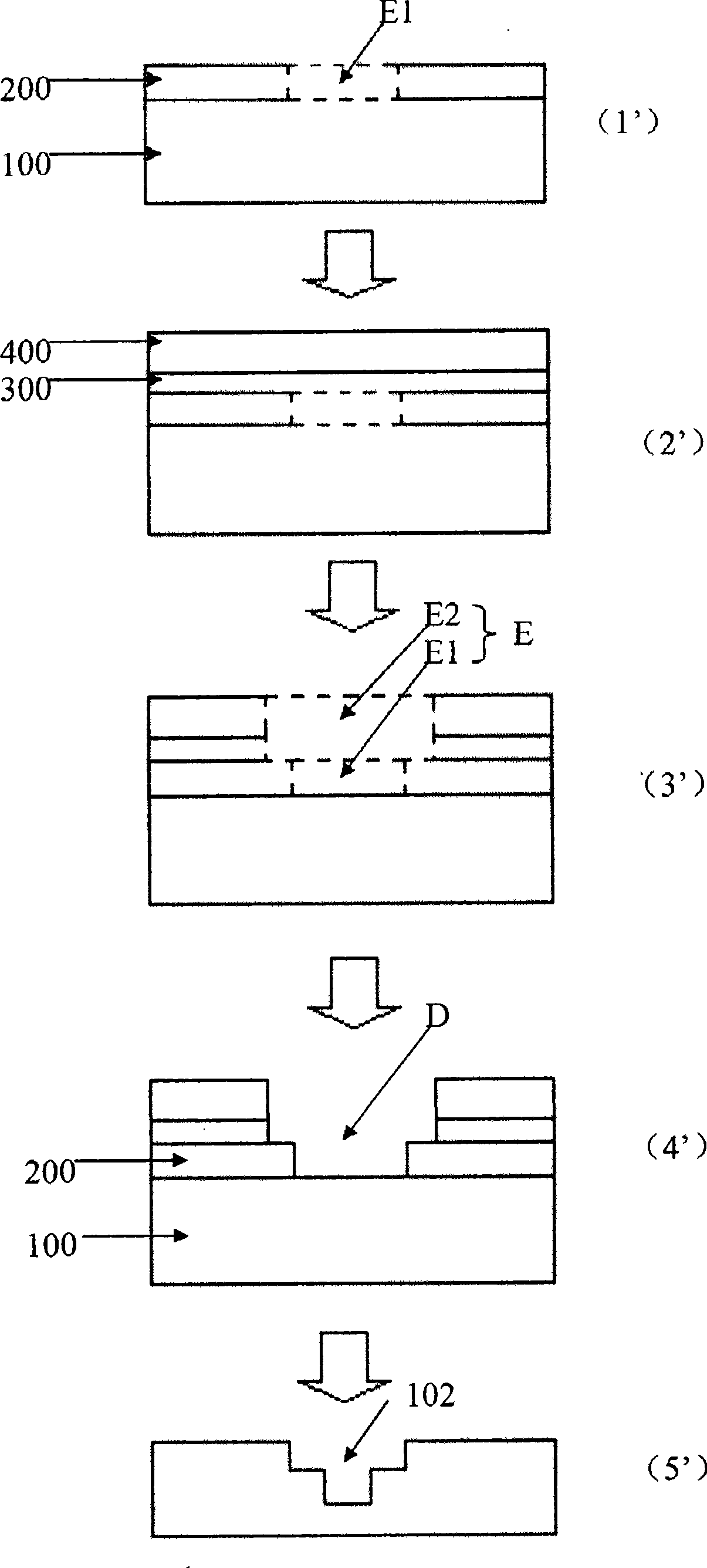

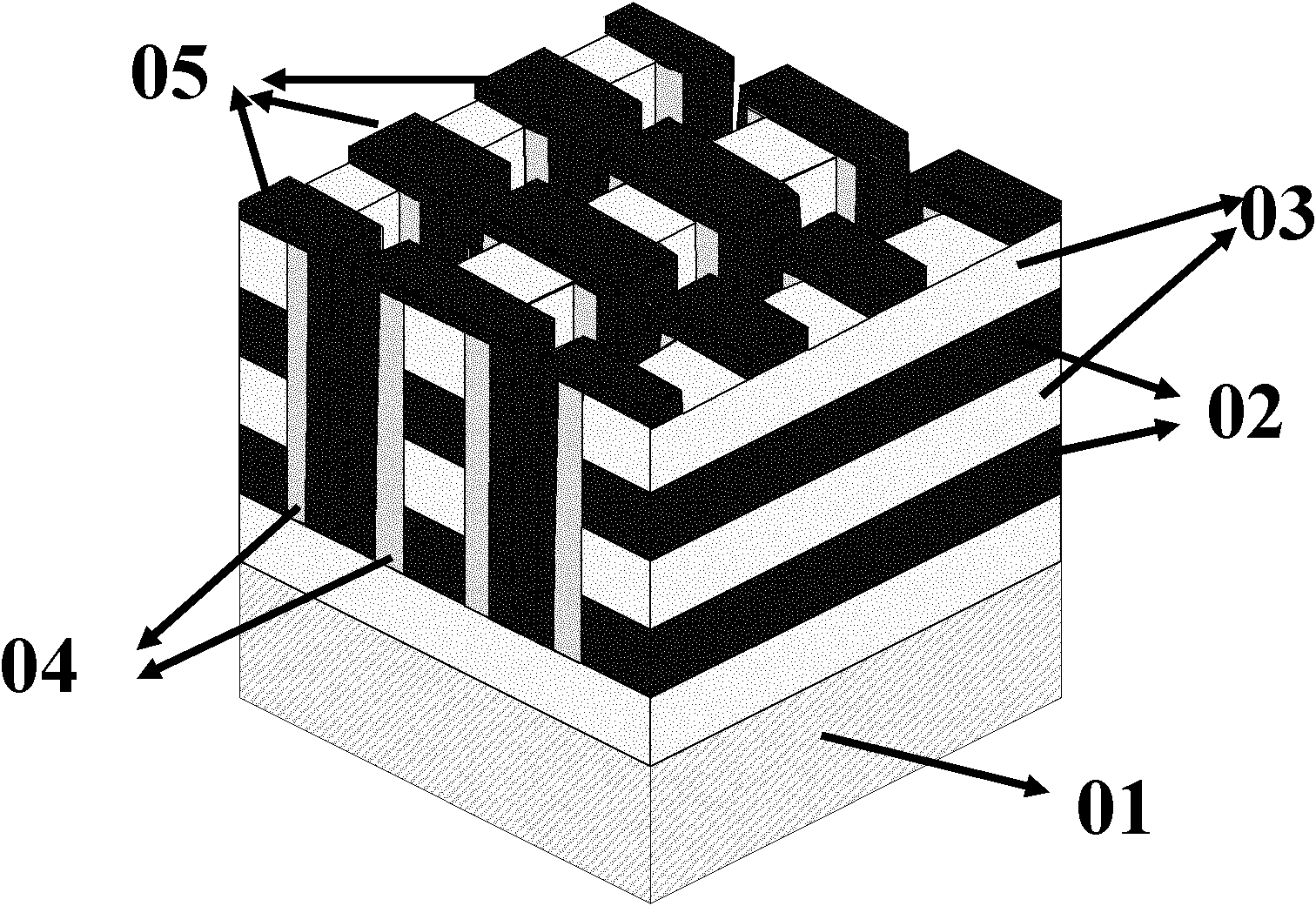

The invention provides a three-dimensional nonvolatile memory array and a preparation method thereof, and belongs to the technical field of a nonvolatile memory in the manufacturing technology of super-large-scale integration. The three-dimensional nonvolatile memory array comprises a substrate and a bottom electrode / isolation medium stack structure; a deep groove is etched on the bottom electrode / isolation medium stack structure; a variable-resistance material and a top electrode layer are deposited on the side wall of the deep groove; the bottom electrode and the top electrode are crossed on the side wall of the deep groove; and a variable-resistance material is arranged between the cross points; each cross point forms a variable-resistance memory unit; all the variable-resistance memory units form a three-dimensional variable-resistance memory array; and the three-dimensional variable-resistance memories in the array are isolated by the isolation medium layer. The invention can improve the storage density of the variable-resistance memory, while simplifying the process and reducing the process cost.

Owner:PEKING UNIV

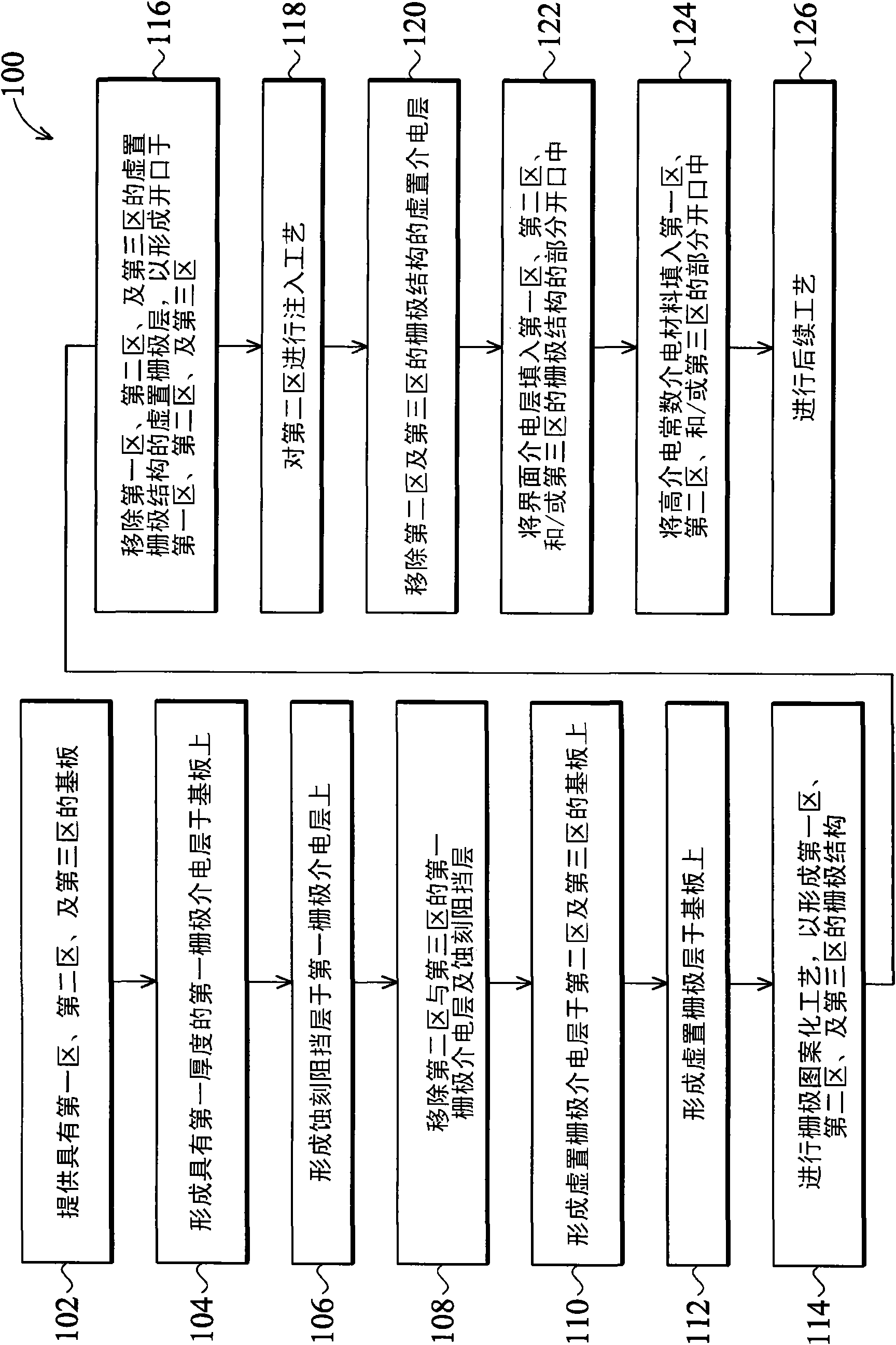

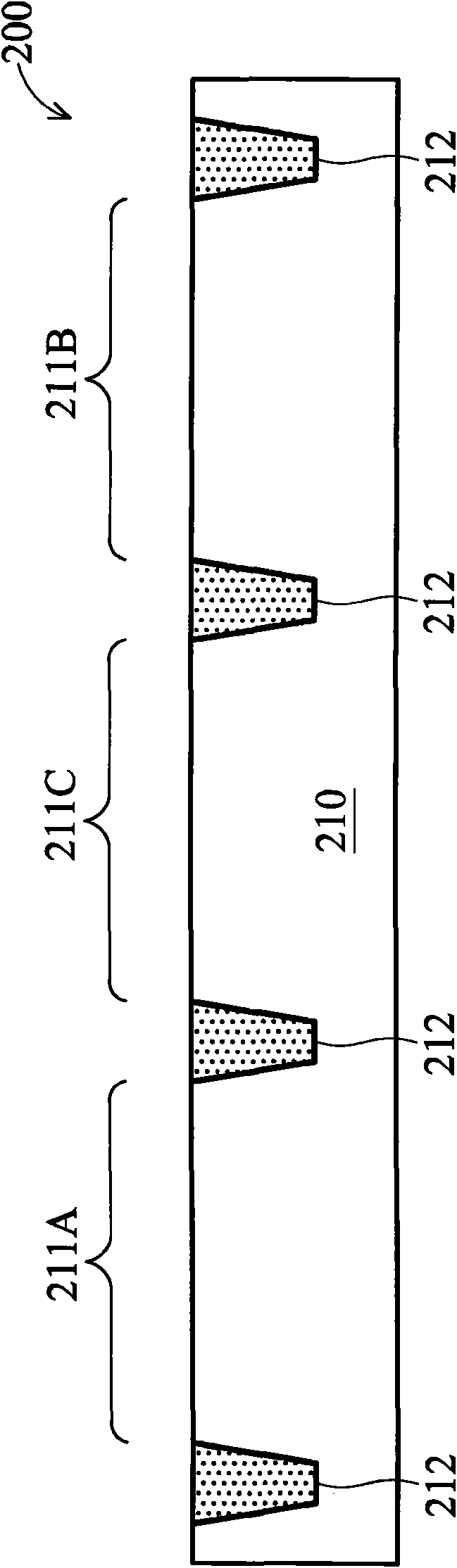

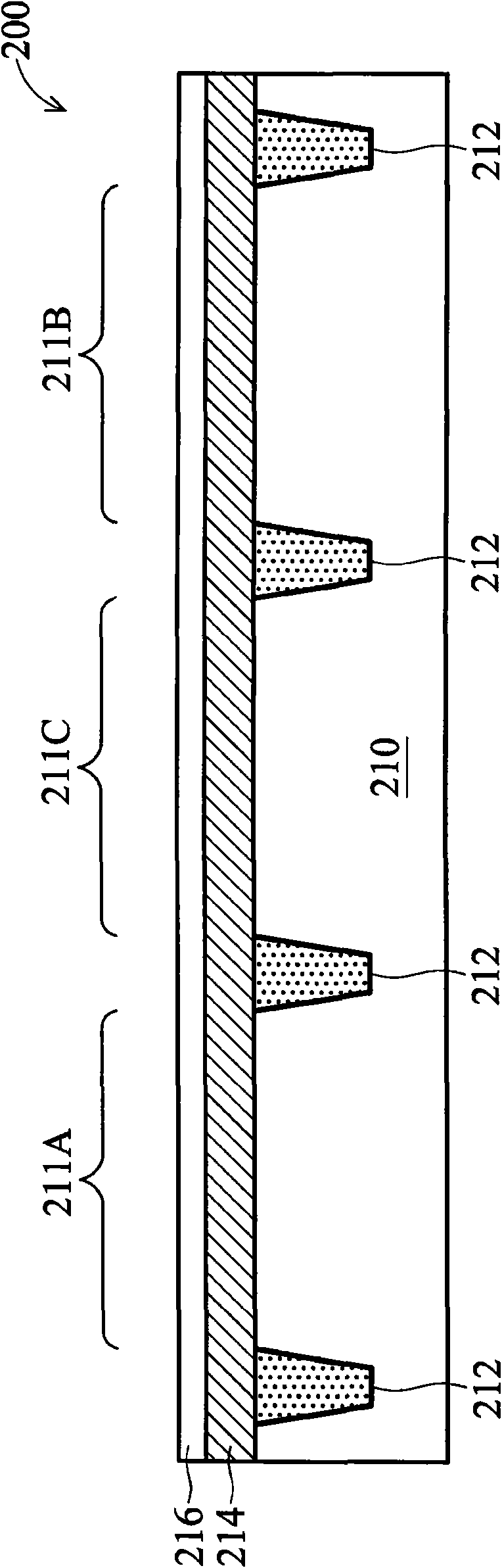

Method for fabricating an integrated circuit device

ActiveCN102117774AReduce the number of etchImprove reliabilityTransistorSemiconductor/solid-state device manufacturingGate dielectricEngineering

The present invention provides a method for fabricating an integrated circuit device. The method includes providing a substrate having a first region, a second region, and a third region; and forming a first gate structure in the first region, a second gate structure in the second region, and a third gate structure in the third region, wherein the first, second, and third gate structures include a gate dielectric layer, the gate dielectric layer being a first thickness in the first gate structure, a second thickness in the second gate structure, and a third thickness in the third gate structure. Forming the gate dielectric layer of the first, second, and third thicknesses can include forming an etching barrier layer over the gate dielectric layer in at least one of the first, second, or third regions while forming the first, second, and third gate structures, and / or prior to forming the gate dielectric layer in at least one of the first, second, or third regions, performing an implantation process on the at least one region. The method can reduce a number of etching oxidation layers of an active region.

Owner:TAIWAN SEMICON MFG CO LTD

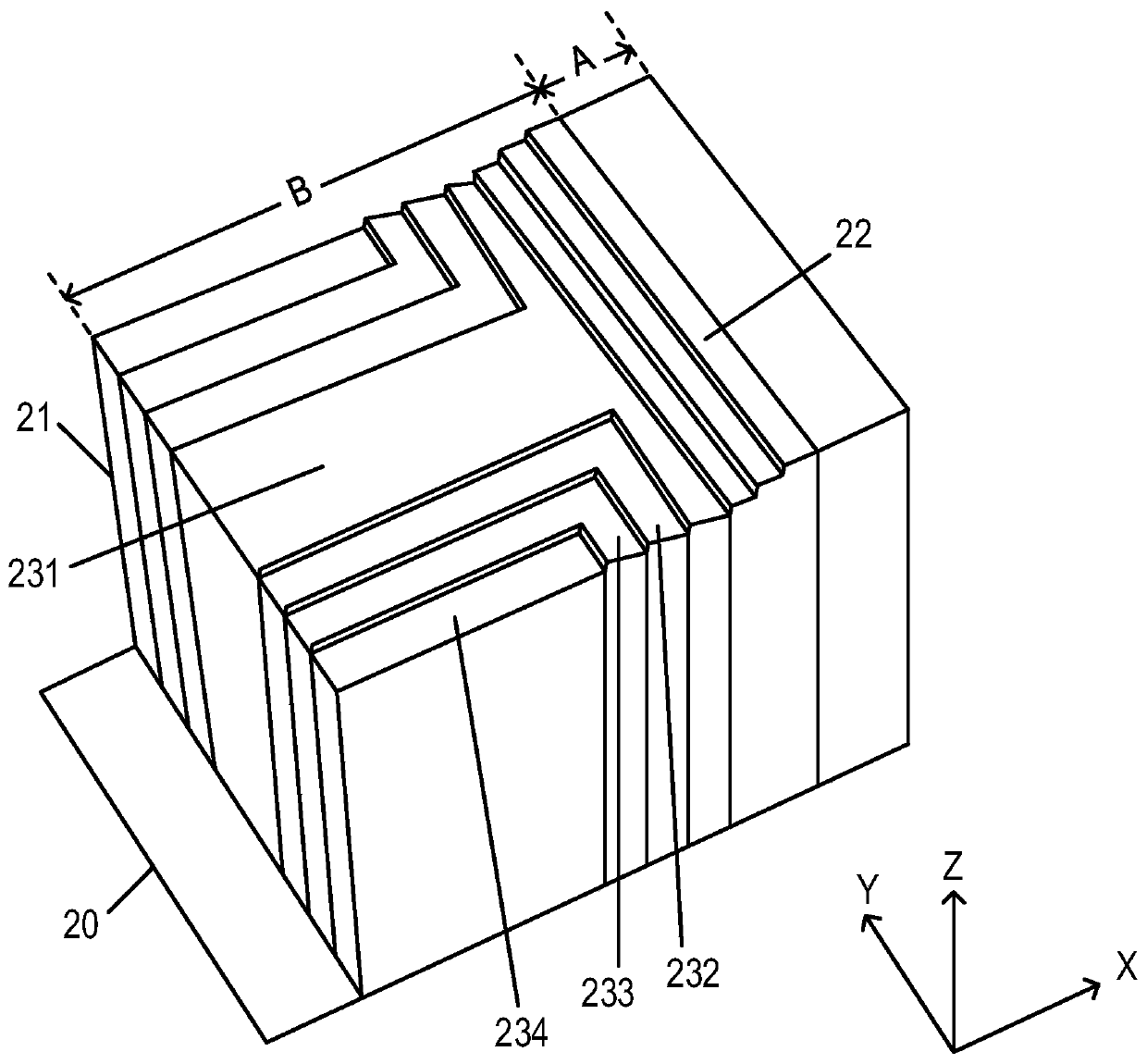

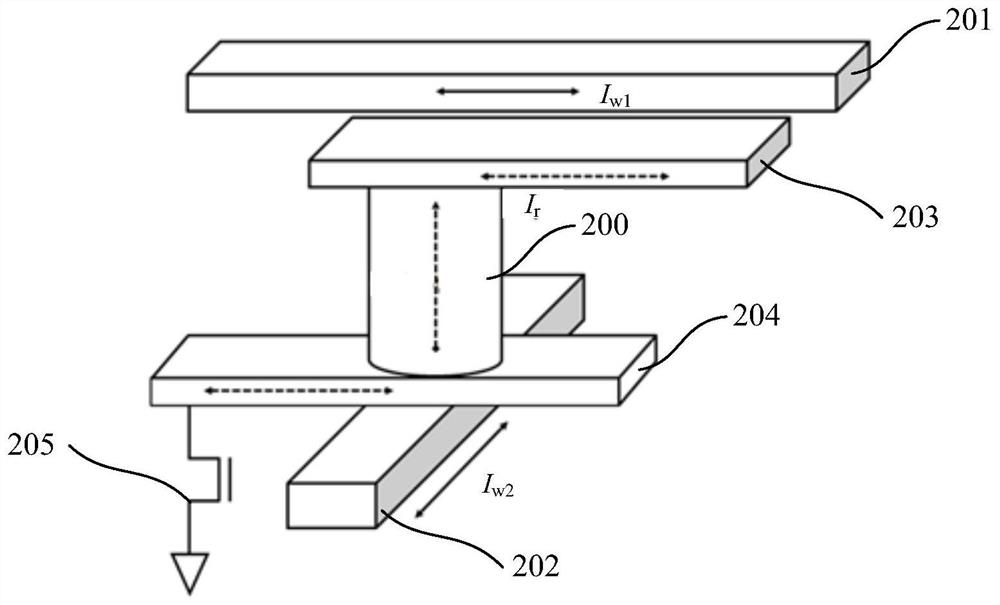

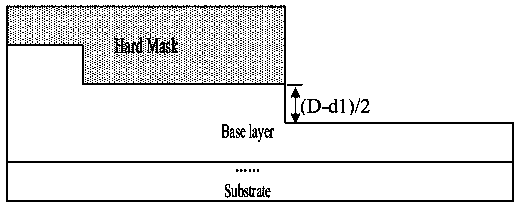

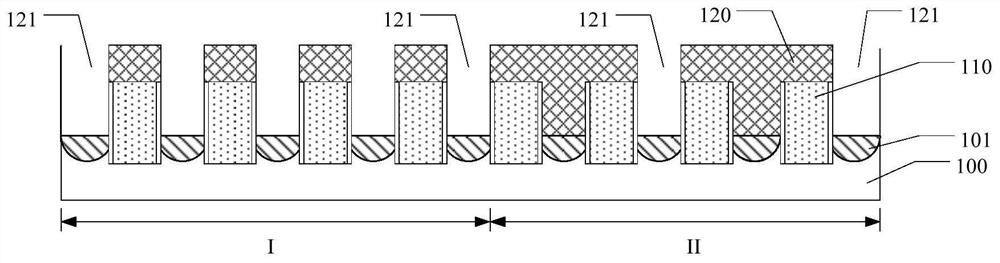

Three-dimensional memory and formation method thereof

ActiveCN110534527ASimple manufacturing processReduce manufacturing costSolid-state devicesSemiconductor devicesSemiconductorElectrical and Electronics engineering

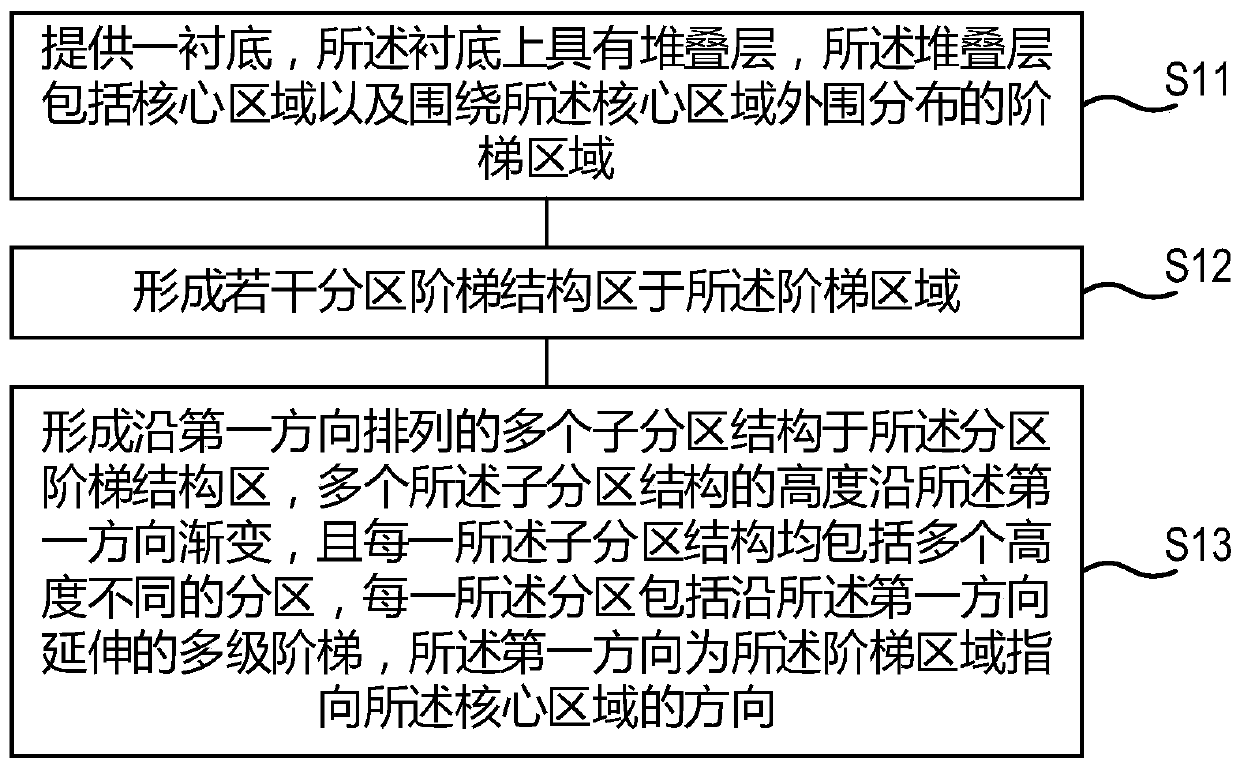

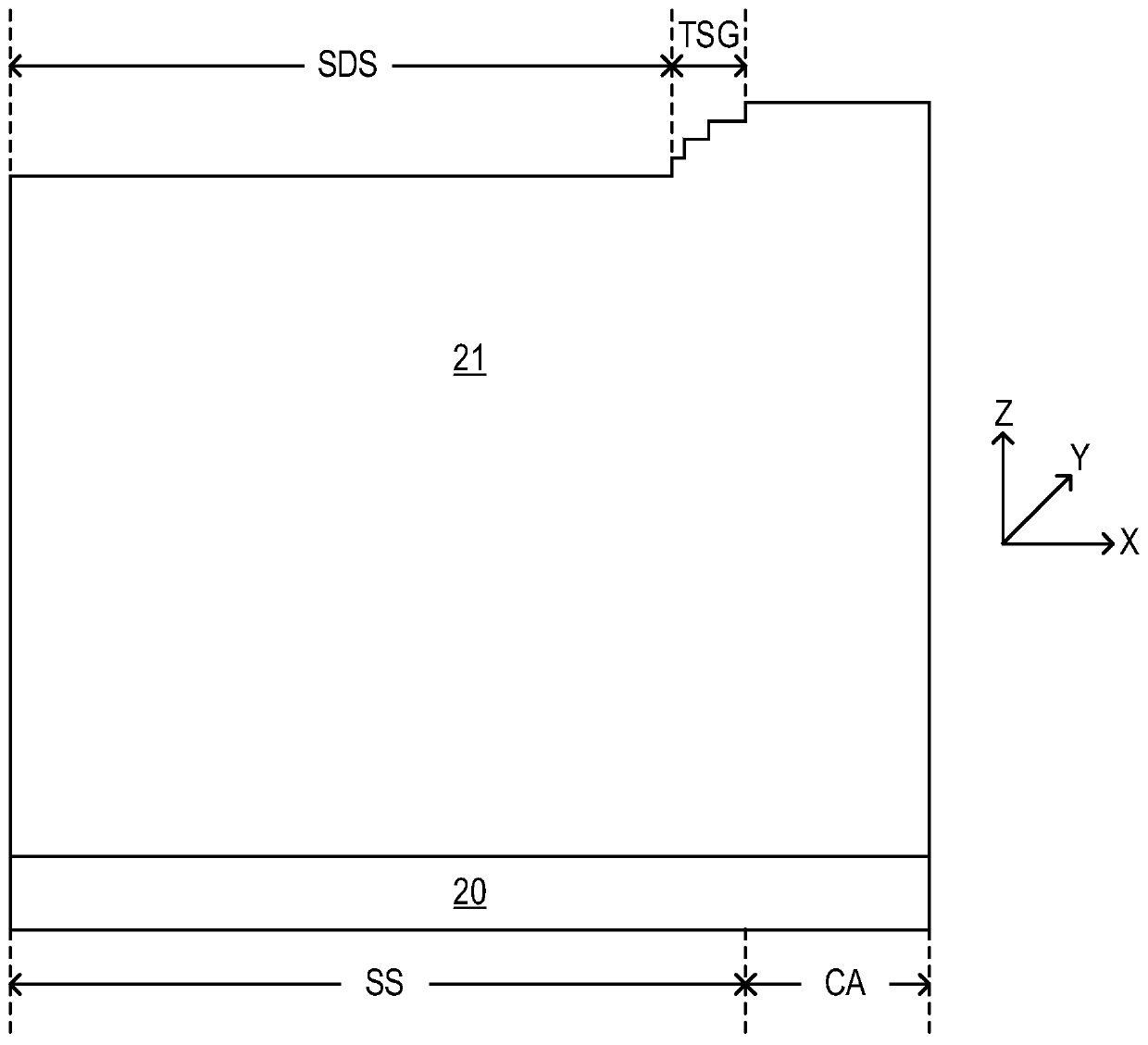

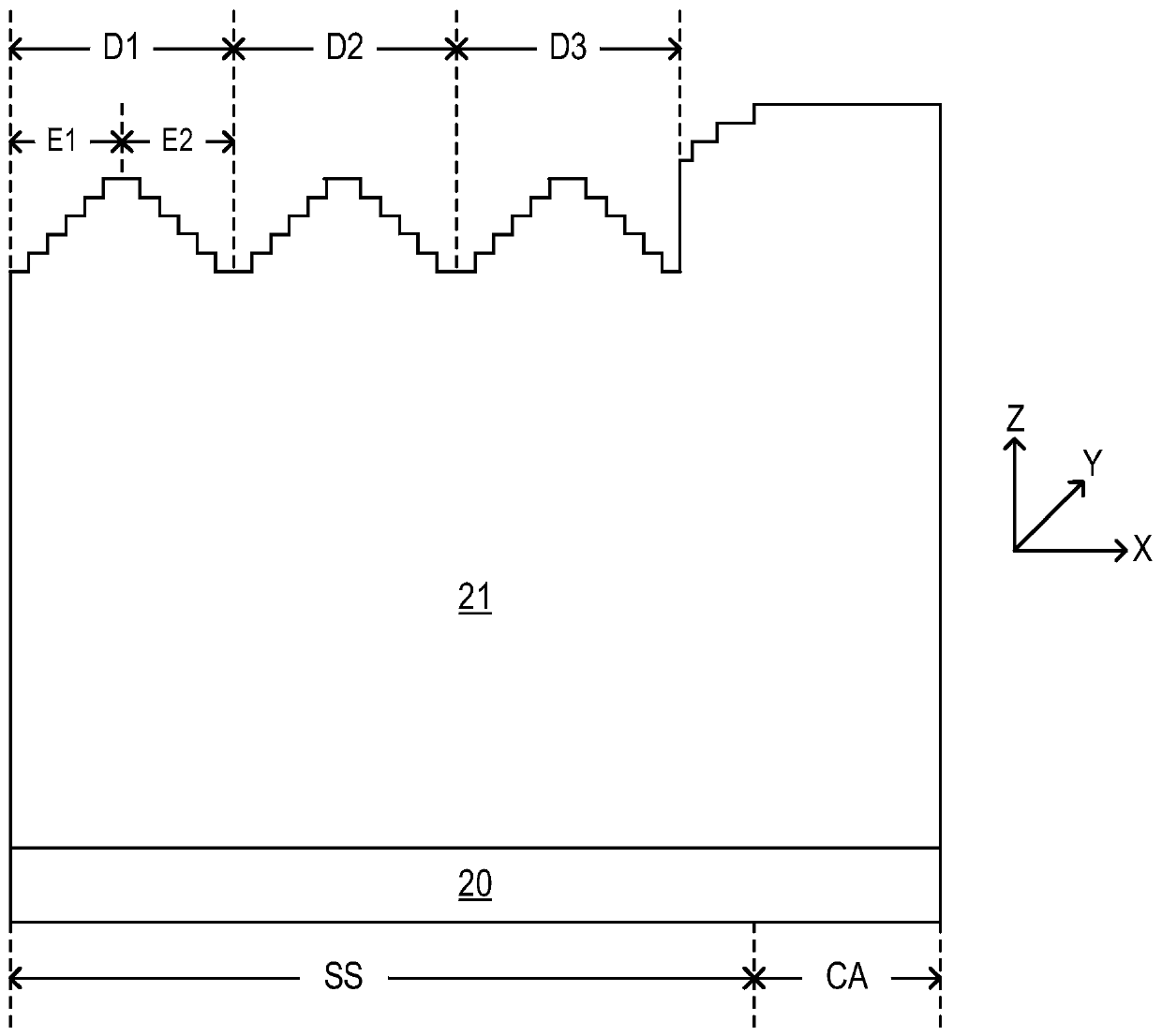

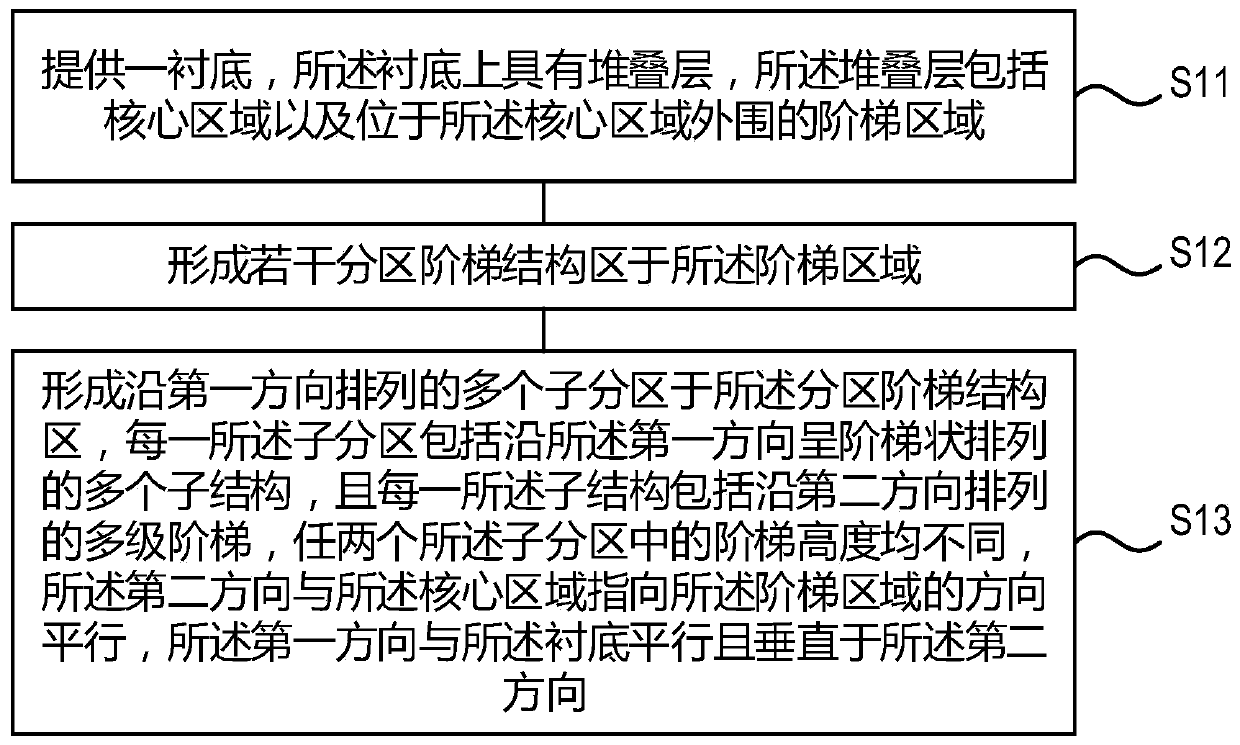

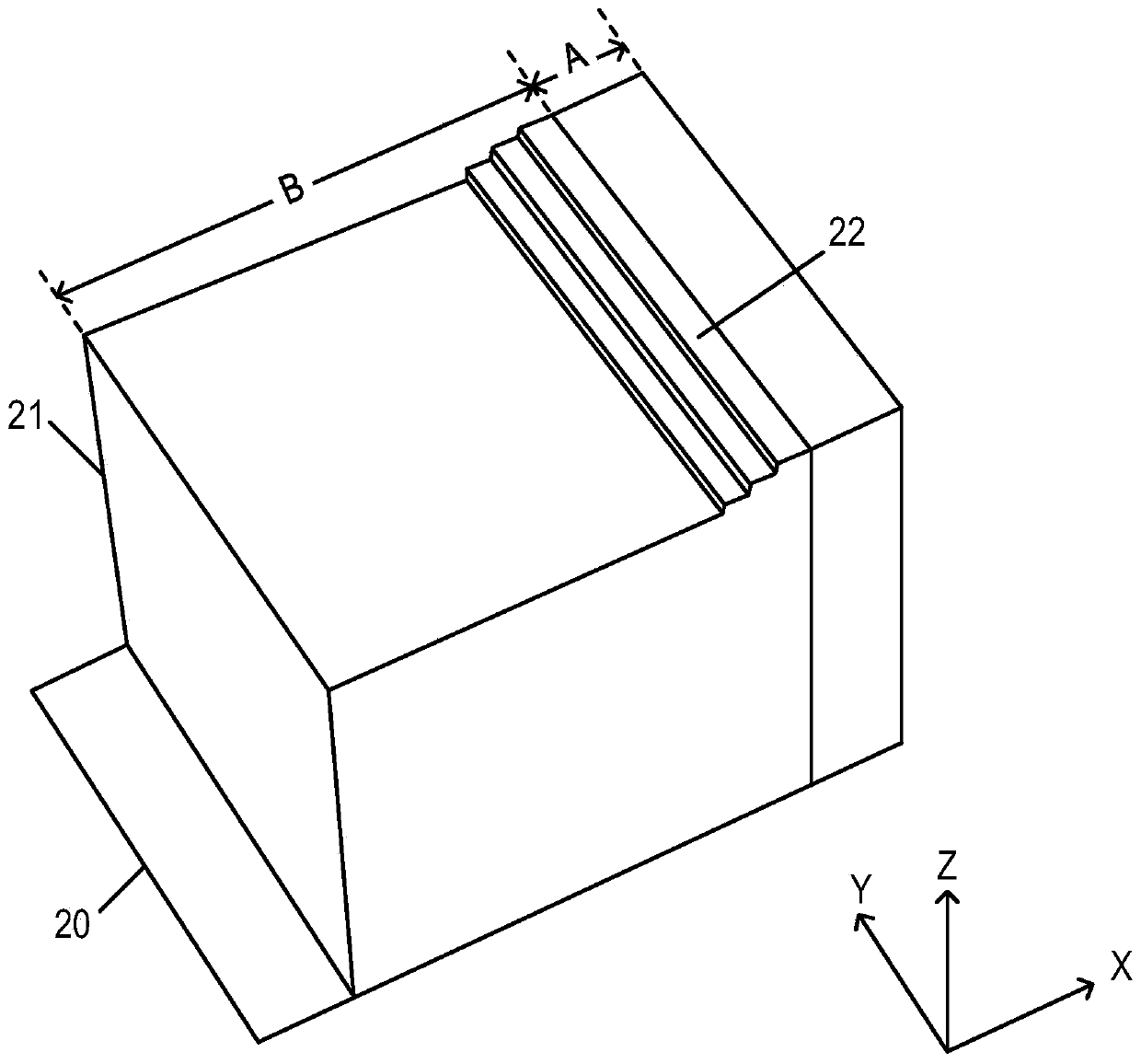

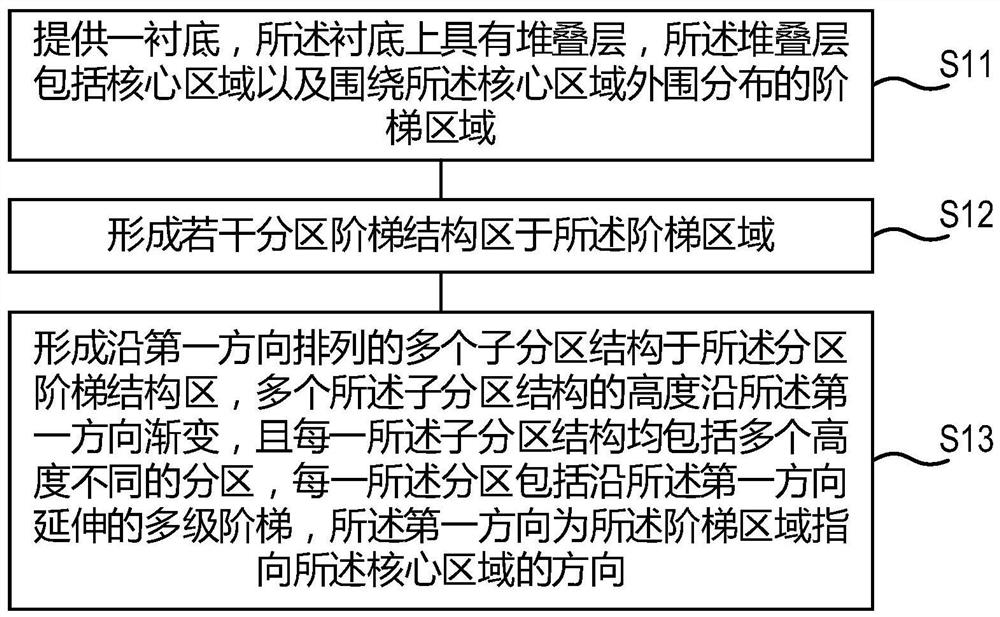

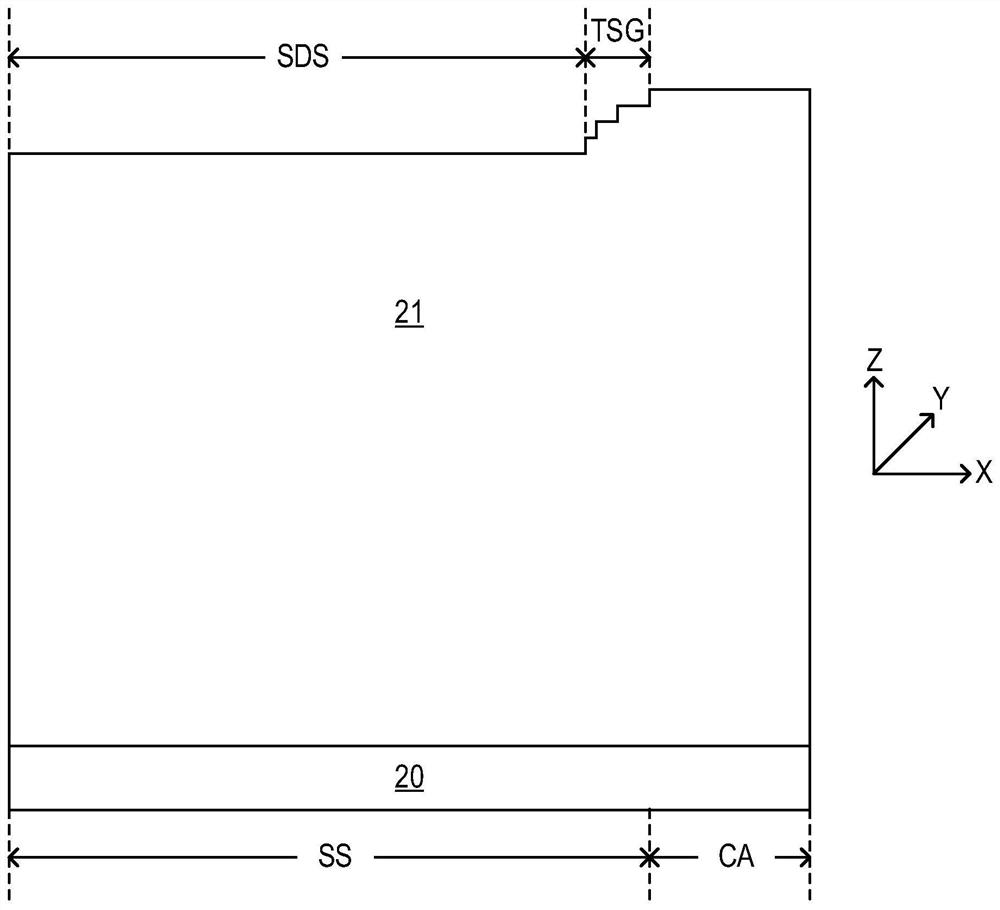

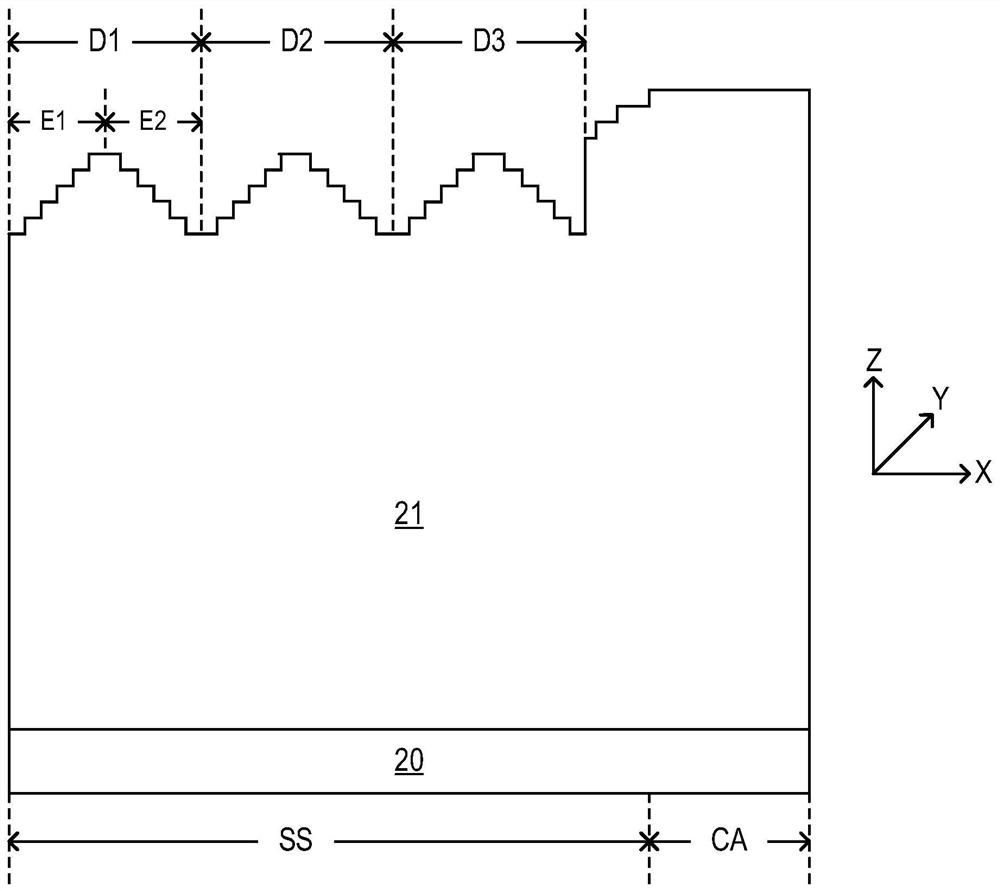

The invention relates to the technical field of semiconductor manufacturing, in particular to a three-dimensional memory and a formation method thereof. The formation method of the three-dimensional memory comprises the following steps: providing a substrate, wherein the substrate is provided with a stacked layer, and the stacked layer comprises a core region and a step region distributed around the periphery of the core region; forming a plurality of partition step structure regions in the step region; and forming a plurality of sub-partition structures arranged along a first direction in thepartition step structure regions, wherein the height of a plurality of sub-partition structures gradually changes along the first direction, and the first direction is the direction in which the stepregions point to the core region. The number of mask plates and the times of etching can be reduced so as to simplify the manufacturing process of the three-dimensional memory and reduce the manufacturing cost of the three-dimensional memory.

Owner:YANGTZE MEMORY TECH CO LTD

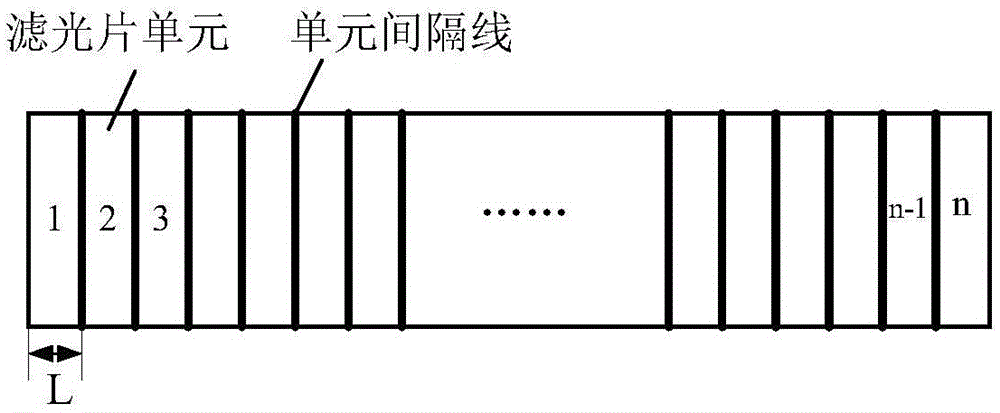

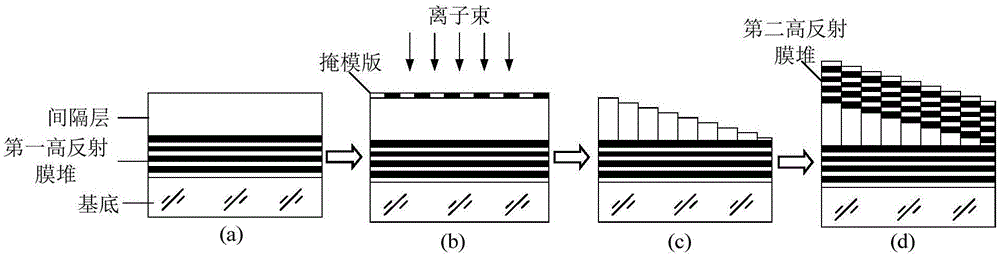

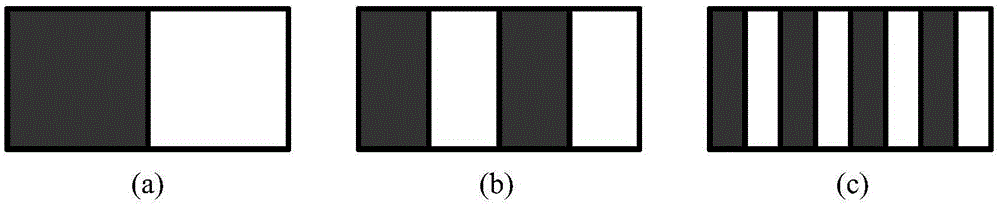

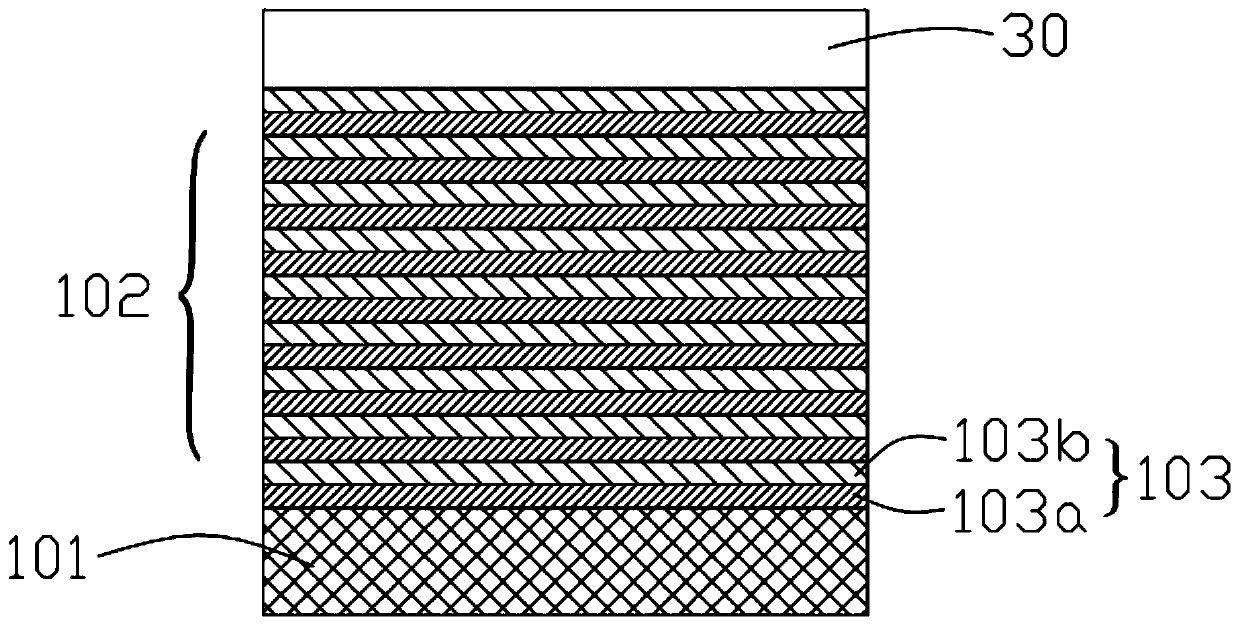

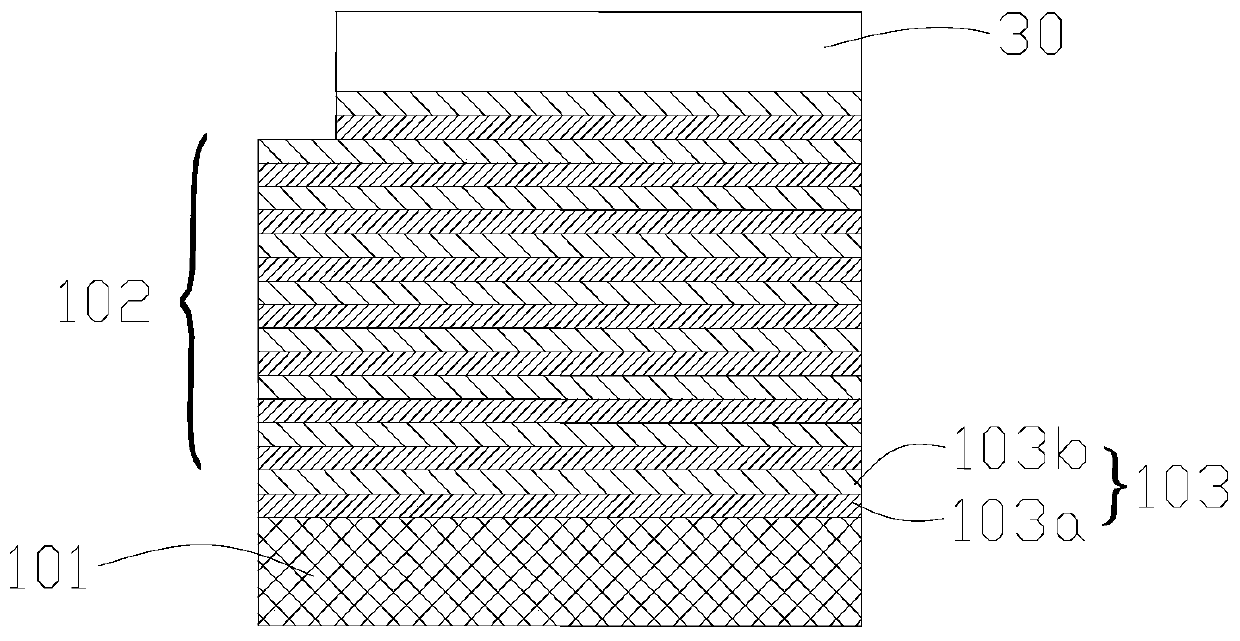

Preparation method for bandpass optical filters with central wavelengths thereof gradually varied

The invention discloses a preparation method for bandpass optical filters with the central wavelengths thereof gradually varied. According to the method, firstly, a first high-reflection film stack and spacing layers are prepared in a vacuum chamber through the plasma-enhanced chemical vapor deposition process according to the proportional relationship between the locations of the central wavelengths of bandpass optical filters and the optical thicknesses of the spacing layers. Secondly, different thickness etching means are conducted on the spacing layers at different locations in the vacuum chamber based on the combination of the ion-beam etching technique and the mask plate etching technique. In this way, the spacing layers corresponding to the locations of different central wavelengths are arranged in the form of ladder-like steps. Finally, a second high-reflection film stack is prepared through the plasma-enhanced chemical vapor deposition process, so that the bandpass optical filters with the central wavelengths thereof gradually varied are obtained. According to the technical scheme of the invention, based on the above preparation method for the bandpass optical filter with the central wavelength thereof gradually varied, n bandpass optical filters with the central wavelengths thereof gradually varied can be prepared each time through the preparation process of the first high-reflection film stack and the spacing layers, the ion beam and mask plate-combined etching process and the preparation process of the second high-reflection film stack. Therefore, the method is simple and high in efficiency.

Owner:XIAN TECH UNIV

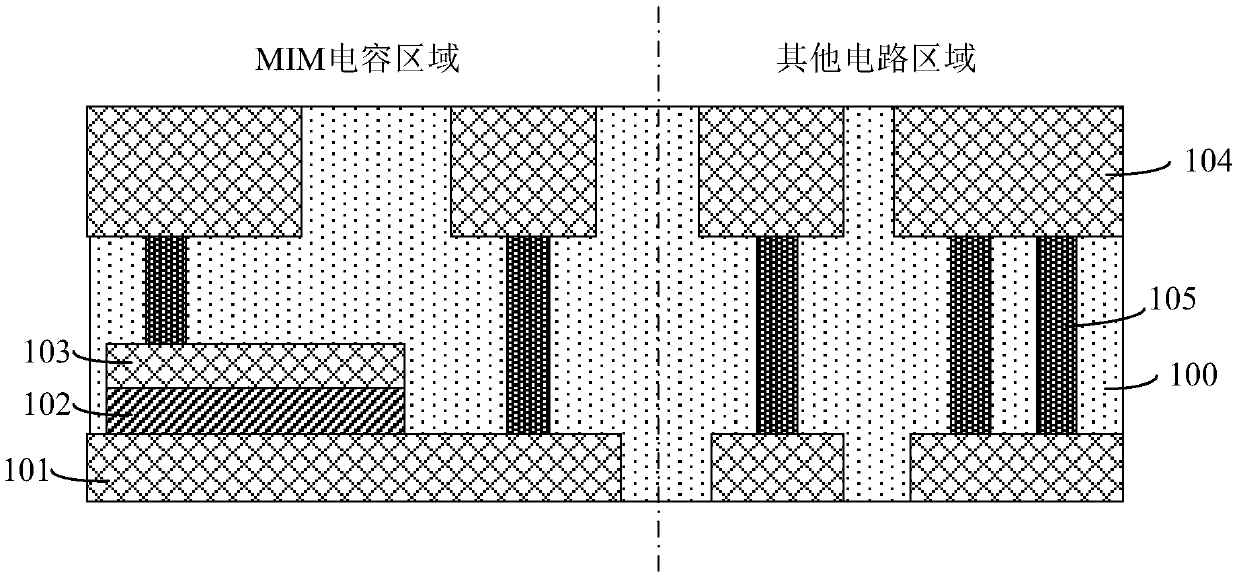

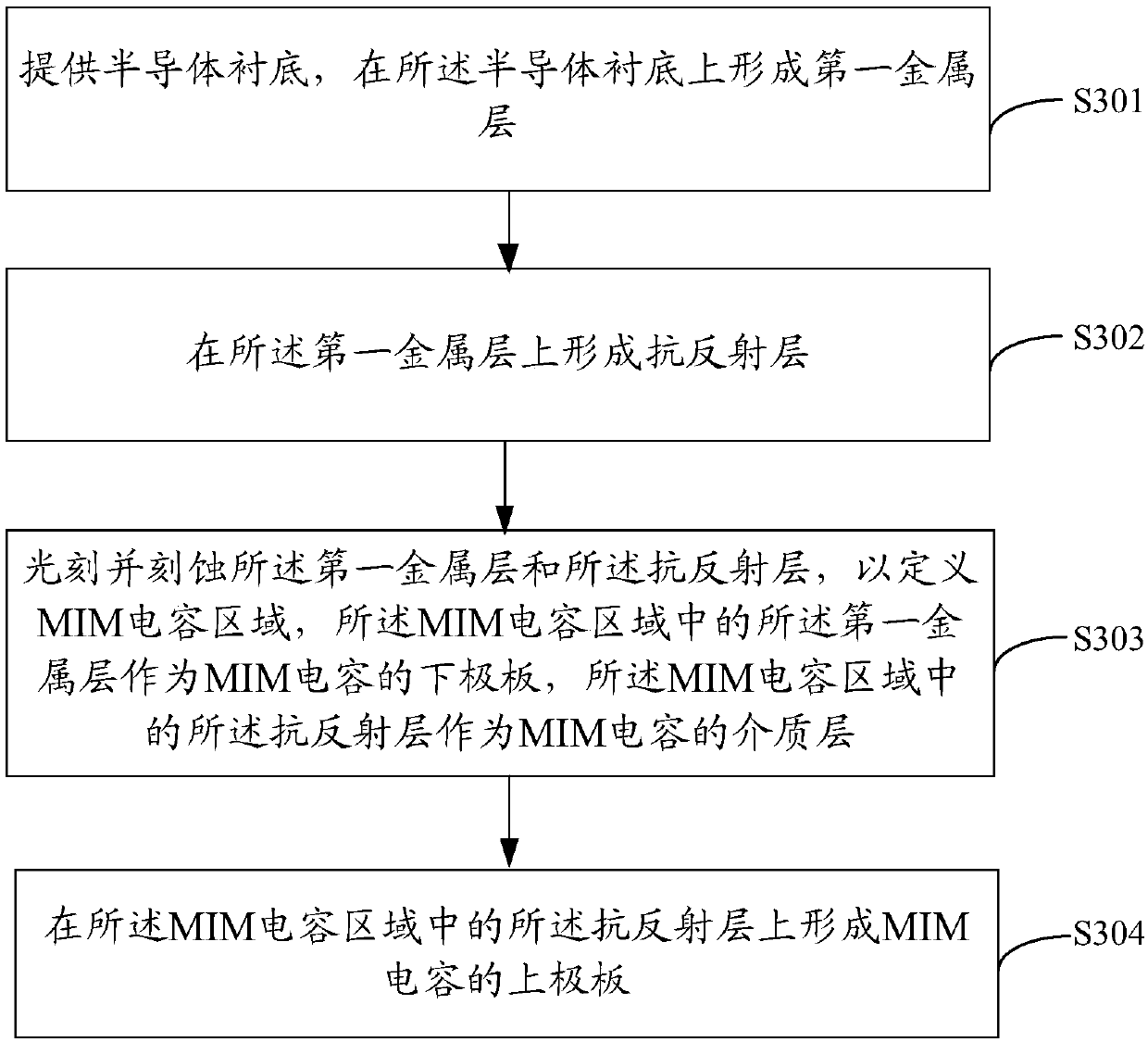

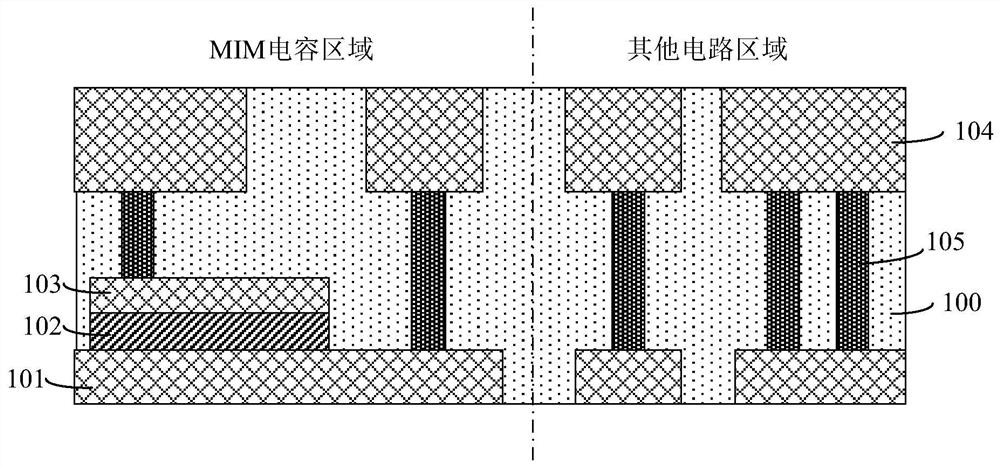

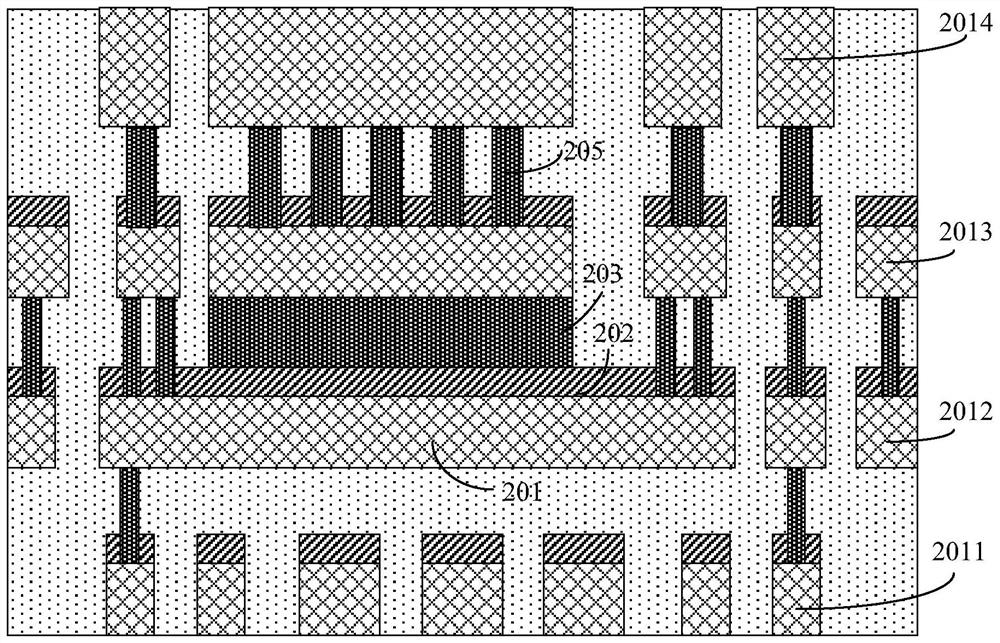

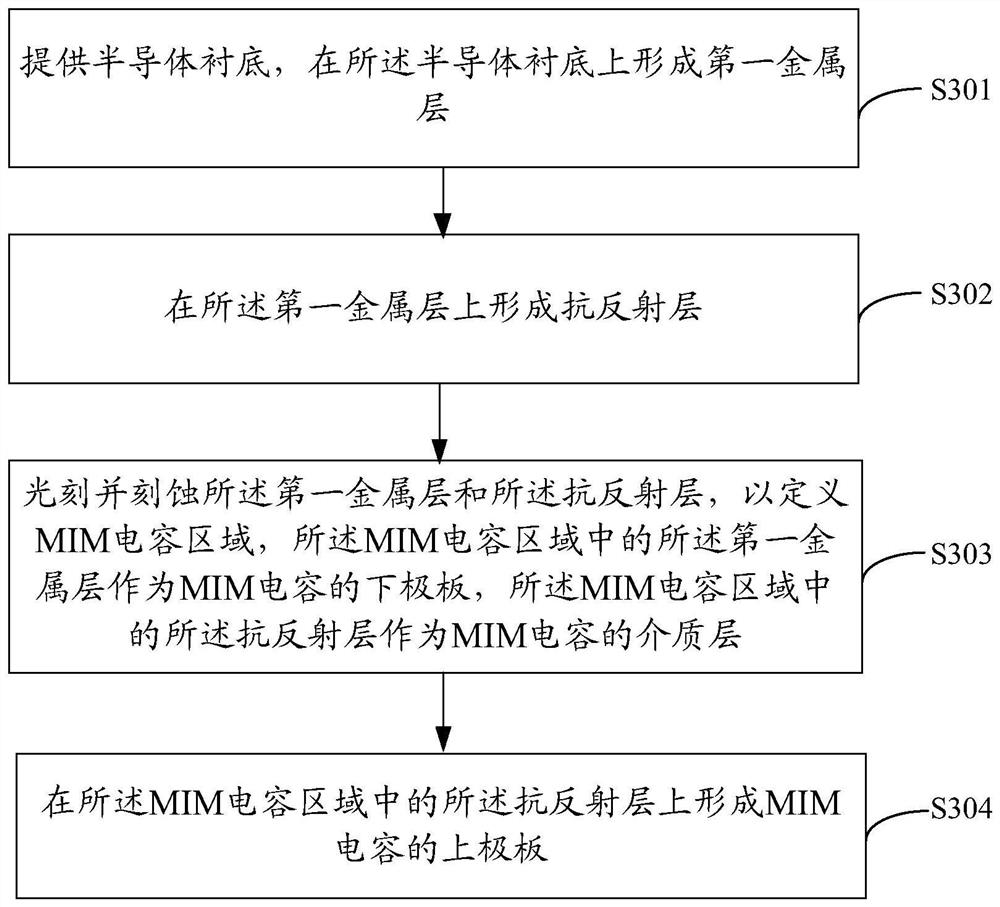

MIM capacitor and manufacturing method thereof

ActiveCN111199953AReduce photolithography processReduce the number of etchSemiconductor/solid-state device detailsSolid-state devicesCapacitanceLithography process

The invention provides an MIM capacitor and a manufacturing method thereof. The manufacturing method comprises the steps of providing a semiconductor substrate, and forming a first metal layer on thesemiconductor substrate; forming an anti-reflection layer on the first metal layer; photoetching and etching the first metal layer and the anti-reflection layer to define an MIM capacitor region, wherein the first metal layer in the MIM capacitor region serves as a lower pole plate of the MIM capacitor, and the anti-reflection layer in the MIM capacitor region serves as a dielectric layer of the MIM capacitor; and forming an upper pole plate of the MIM capacitor on the anti-reflection layer in the MIM capacitor region. According to the manufacturing method provided by the invention, the anti-reflection layer reserved in the etched area is used as a dielectric layer of the capacitor at the same time, the etched area is continuously filled with metal to serve as the upper pole plate, an additional capacitor dielectric layer does not need to be manufactured, an additional photoetching process is not needed for defining the upper pole plate area any more, and the photoetching and etching frequency is reduced, so that the process cost is reduced, and the process period is shortened.

Owner:CSMC TECH FAB2 CO LTD

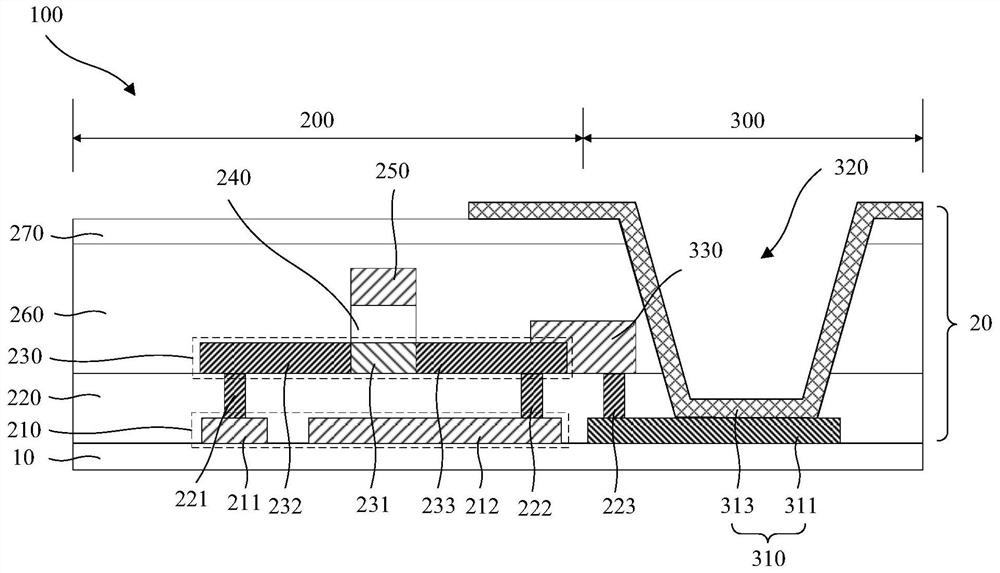

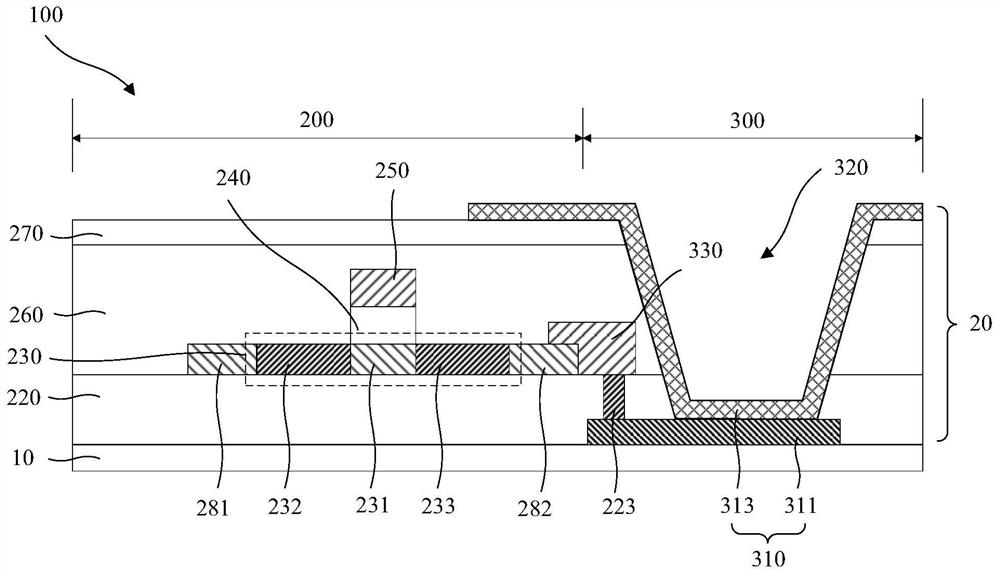

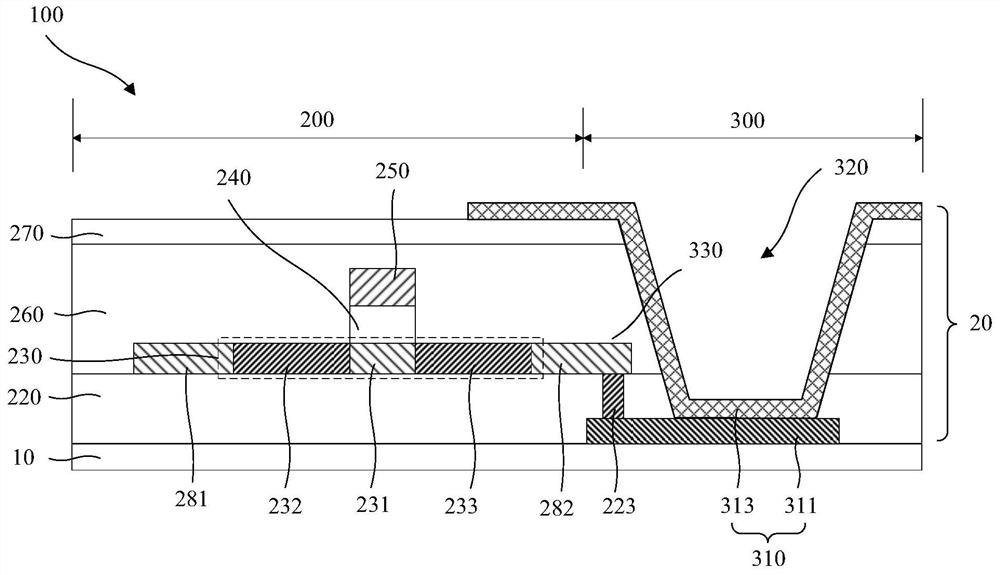

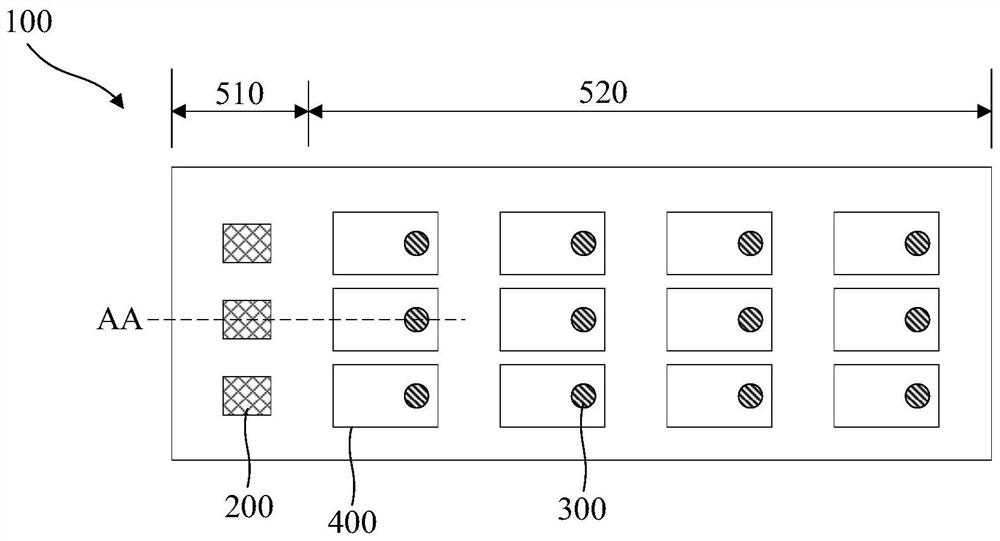

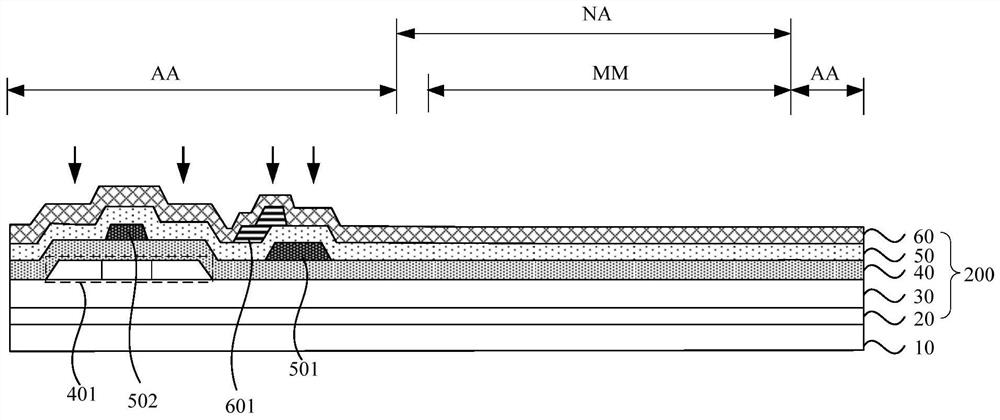

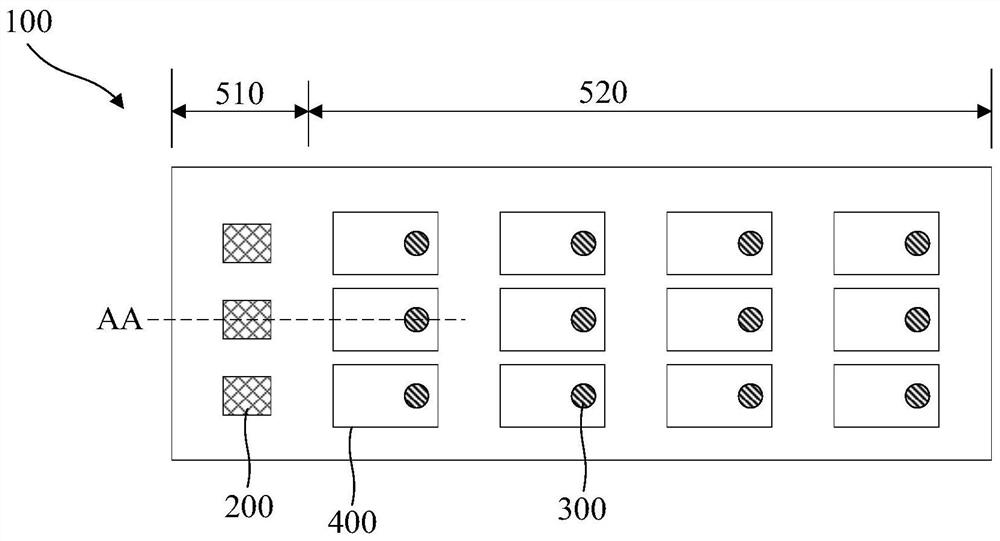

Light-emitting panel and manufacturing method thereof

ActiveCN112838100AReduce the number of etchSimplify processing difficultyTransistorSolid-state devicesThin membraneHemt circuits

The invention provides a light-emitting panel and a manufacturing method thereof. The light-emitting panel comprises a thin film transistor area and a binding area away from the thin film transistor area, a plurality of thin film transistor units are arranged in the thin film transistor area, at least one first terminal is arranged in the binding area, and the first terminal at least comprises a first electrode located on the substrate. The first electrode and at least one of the first metal layer and the second metal layer in the thin film transistor unit are arranged on the same layer, so that the first electrode is electrically connected with the driving circuit layer through the electric connecting component; and the first electrode, the source and drain electrodes in the driving circuit layer and the shading metal are formed in the same process, so that the etching times of the manufacturing process are reduced, the process difficulty of the light-emitting panel is simplified, and the manufacturing efficiency is improved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

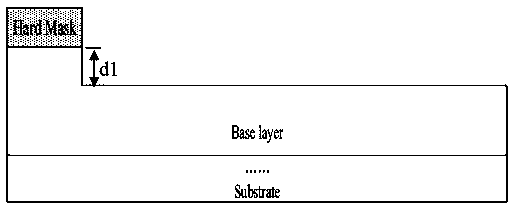

Preparation method of SiC high-voltage power device junction terminal

InactiveCN107546114AHigh blocking voltageReduce the number of etchSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingEngineering

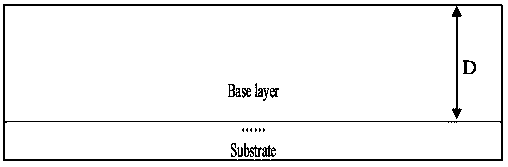

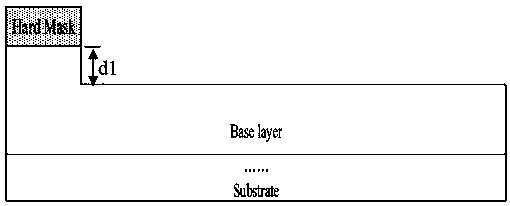

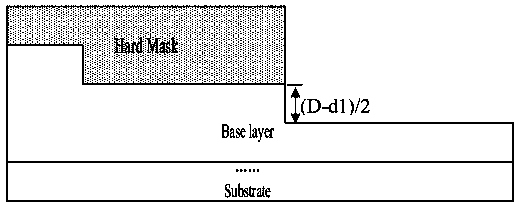

The invention discloses a preparation method of a SiC high-voltage power device junction terminal. Firstly, according to blocking voltage requirement of different levels, a number (2n) of steps is determined and the mask pattern structure design is carried out; then a multi-level step structure is formed on a SiC sample through multiple times of step preparation process (including preparing a hardmask layer, etching a step region, and removing a silicon oxide hard mask layer), and finally steps of 2n levels are formed through (n+1) times of step etching. For making the SiC high-voltage powerdevice junction terminal with the steps of multiple levels, the terminal can be prepared only with very few times of step etching, thus while the steps of multiple levels can be realized and SiC high-voltage power device blocking voltage is greatly raised, the preparation process of the multi-step junction terminal can be greatly simplified, and thus the method has a great application prospect inthe SiC high-voltage power device.

Owner:INST OF ELECTRONICS ENG CHINA ACAD OF ENG PHYSICS

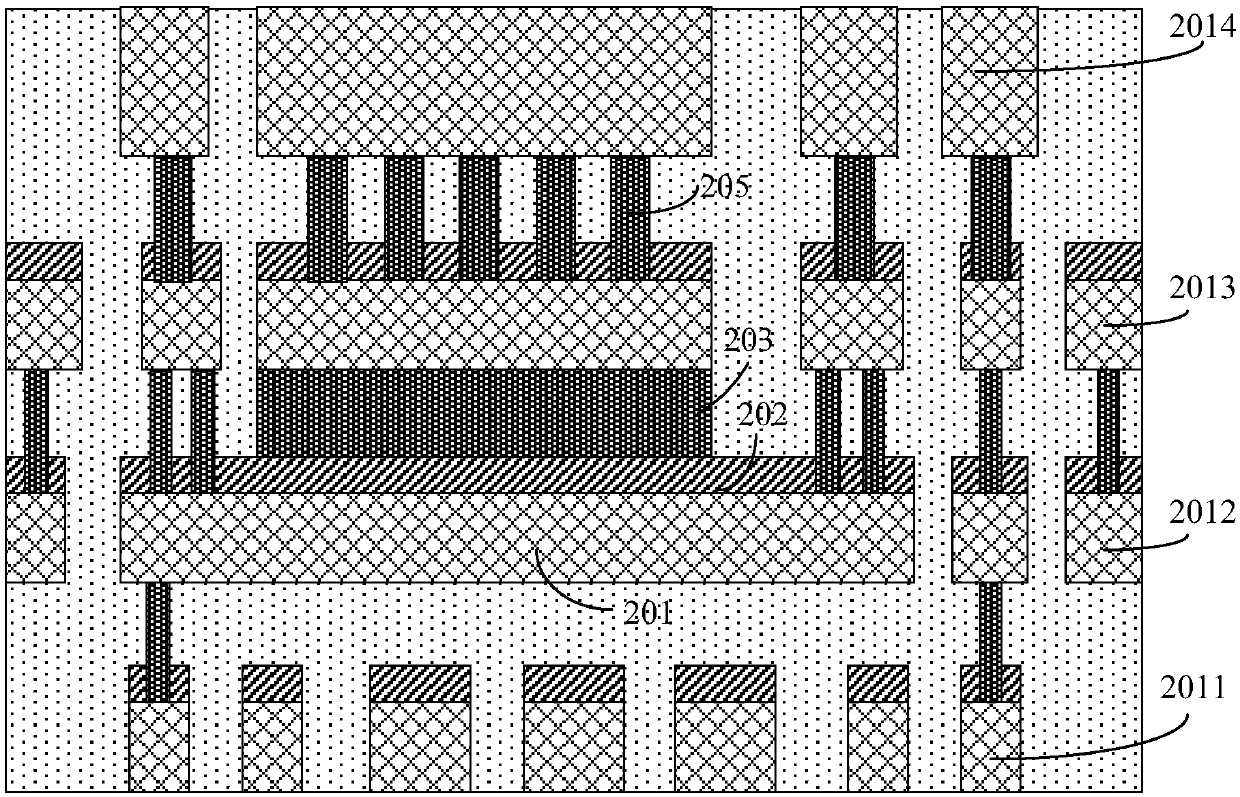

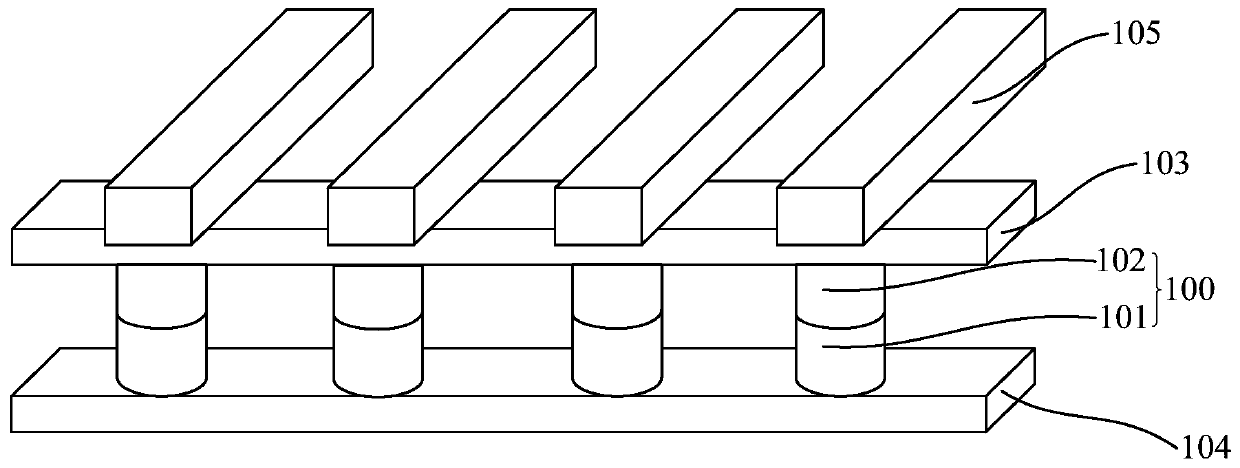

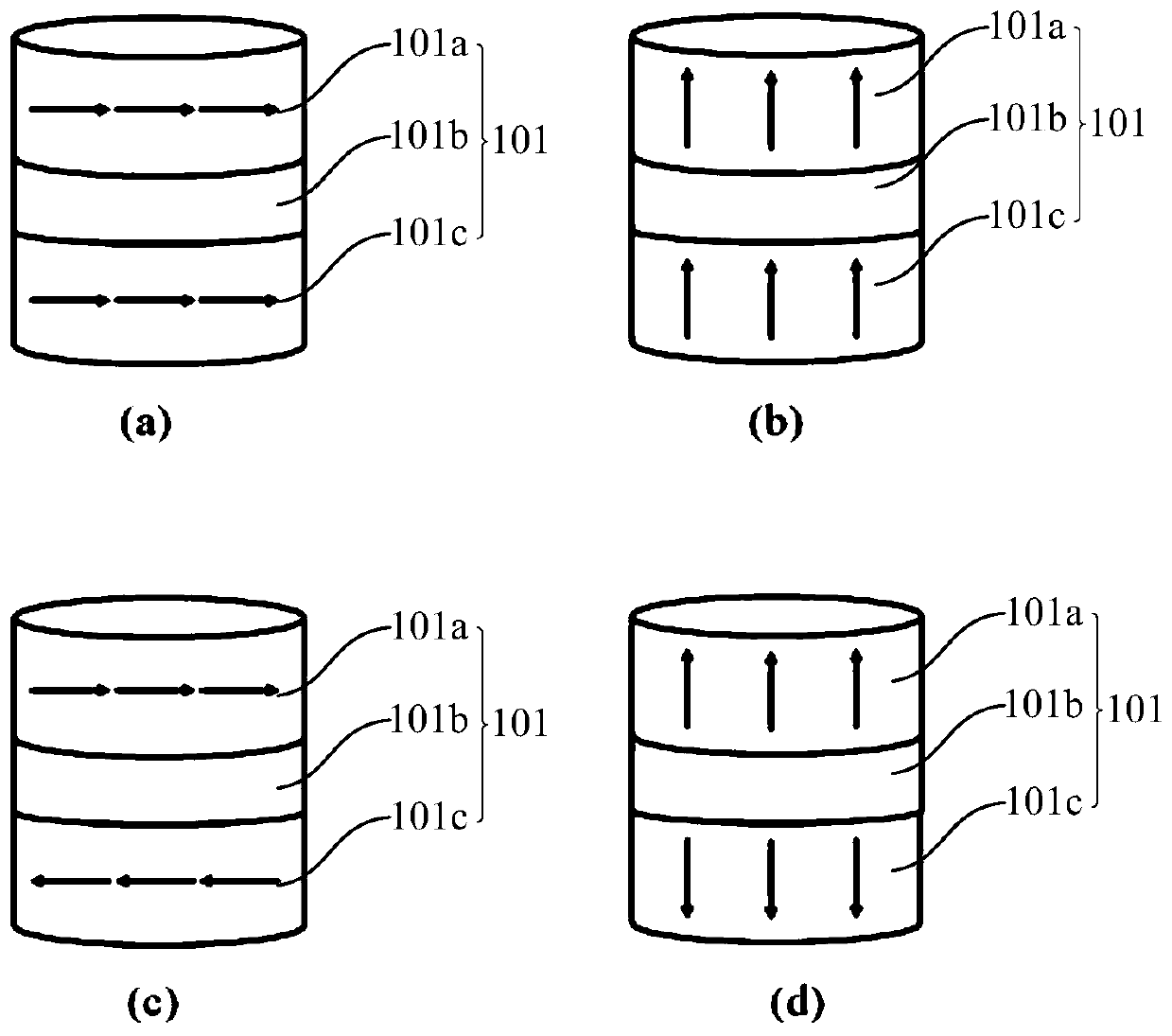

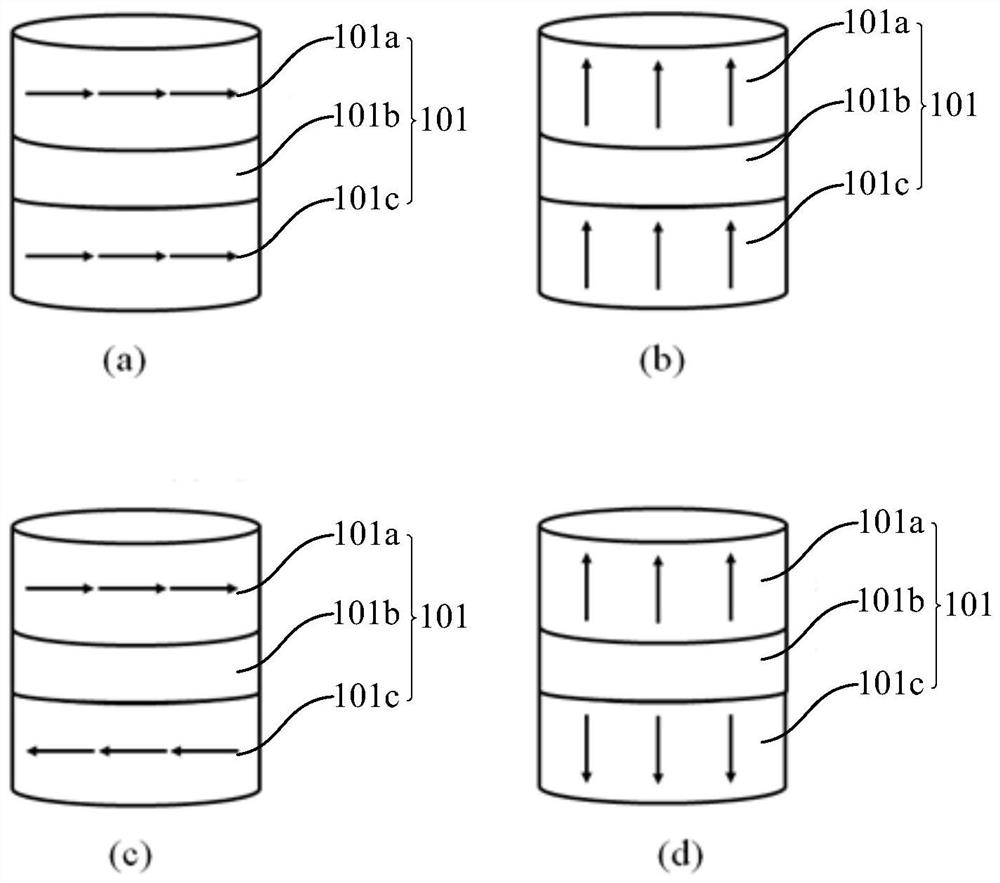

Memory array structure, preparation method thereof, memory, write-in method and read-out method

ActiveCN109860192AGuaranteed working voltageSimple manufacturing processSolid-state devicesSemiconductor devicesComputer architectureCmos logic circuits

The invention provides a memory array structure, a preparation method thereof, a memory, a write-in method and a read-out method. The array structure comprises at least one memory cell which comprisesa superconducting device and a magnetic memory device which are overlapped and connected in series; at least one superconductive upper electrode which is arranged above the memory unit; at least onesuperconductive lower electrode arranged below the memory unit; at least one superconductive word line arranged above the memory unit or below the memory unit, wherein the superconductive word line isarranged close to the superconductive device in the memory unit. According to the invention, the magnetic memory device is organically combined with the superconducting integrated circuit, and the switching effect of the circuit is realized by using a superconducting device, thereby replacing a CMOS logic circuit. The memory array structure can achieve the operation of the memory at low temperature, guarantees that an MRAM achieves high-speed and high-density storage at a low working voltage, achieves the work based on different writing modes, forms an information reading mode suitable for the superconducting logic process, and is simple in structural design and beneficial to reduction of the etching frequency.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

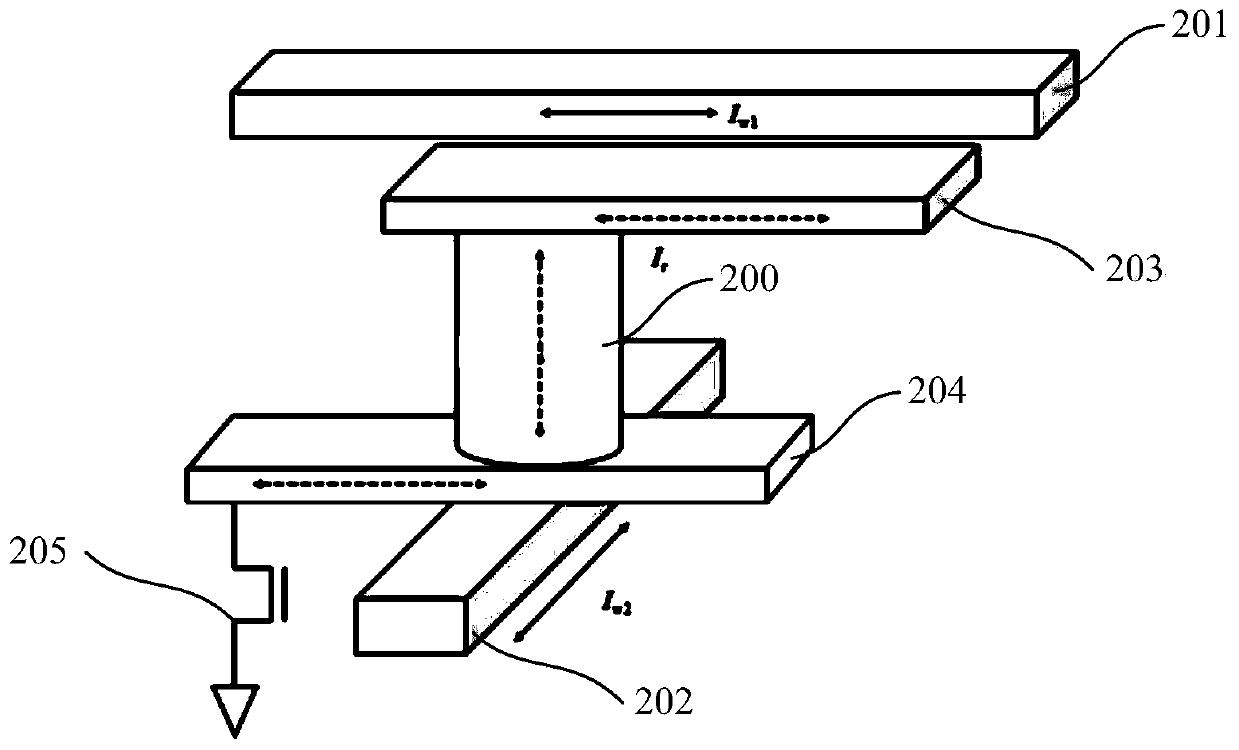

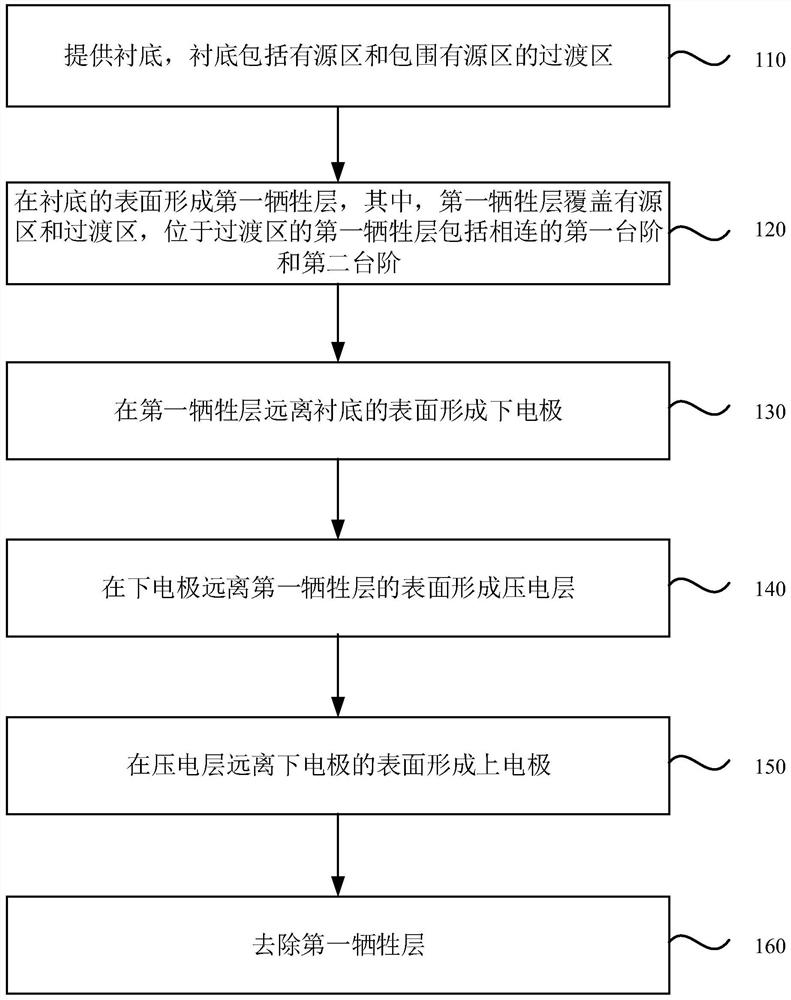

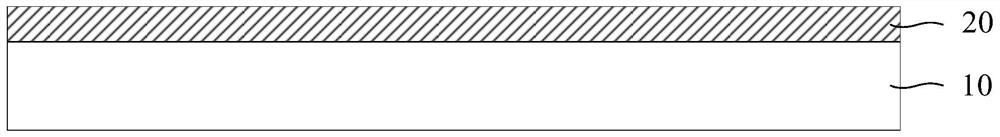

Preparation method of bulk acoustic wave resonator and bulk acoustic wave resonator

PendingCN112953446AThe process steps are simpleAvoid lossImpedence networksAcoustic waveMaterials science

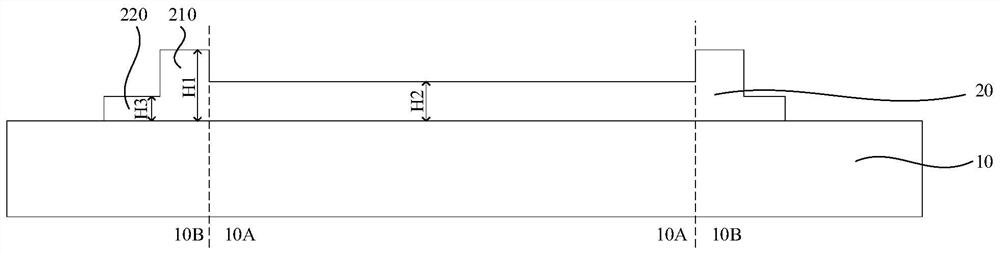

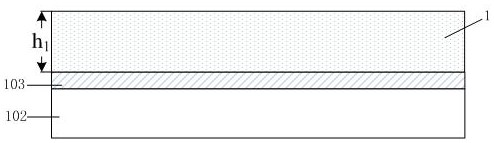

The invention discloses a preparation method of a bulk acoustic wave resonator and the bulk acoustic wave resonator. The preparation method of the bulk acoustic wave resonator comprises the following steps: providing a substrate, wherein the substrate comprises an active region and a transition region surrounding the active region; forming a first sacrificial layer on the surface of the substrate, wherein the first sacrificial layer covers the active region and the transition region; the first sacrificial layer in the transition region comprises a first step and a second step which are connected; the height of the first step is larger than that of the first sacrificial layer in the active region; and the height of the second step is smaller than that of the first sacrificial layer in the transition region; and the height of the second step is smaller than that of the first sacrificial layer in the active region; forming a lower electrode on the surface, away from the substrate, of the first sacrificial layer; forming a piezoelectric layer on the surface, away from the first sacrificial layer, of the lower electrode; forming an upper electrode on the surface, away from the lower electrode, of the piezoelectric layer; and removing the first sacrificial layer. According to the technical scheme provided by the embodiment of the invention, the process steps for preparing the bulk acoustic wave resonator are simplified, and the yield of the bulk acoustic wave resonator is improved.

Owner:SUZHOU HUNTERSUN ELECTRONICS CO LTD

Method for forming interlaminar capacitor

InactiveCN101197256AReduce depositionReduce the number of etchSemiconductor/solid-state device manufacturingDielectricEtching

The invention discloses a forming method of layer capacitor, which uses an etch stop layer as capacitor medium without extra medium layer to deposit and form the capacitor medium, and form an upper metal connecting line and a capacitor upper pole plate by using the same metal layer. The method specifically comprises the following steps of: depositing the etch stop layer and an inter-level dielectrics film after a capacitor lower pole plate is formed; a capacitor plate groove is formed in the inter-level dielectrics firm by etching, wherein, the capacitor plate groove passes the inter-level dielectrics film and stops at the etch stop layer and part of the etch stop layer is exposed, and further the exposed etch stop layer is used as the capacitor medium; and forming the capacitor upper pole plate in the capacitor plate groove. Compared with the prior art, the invention reduces times for depositing and etching and simplifies the process flow.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

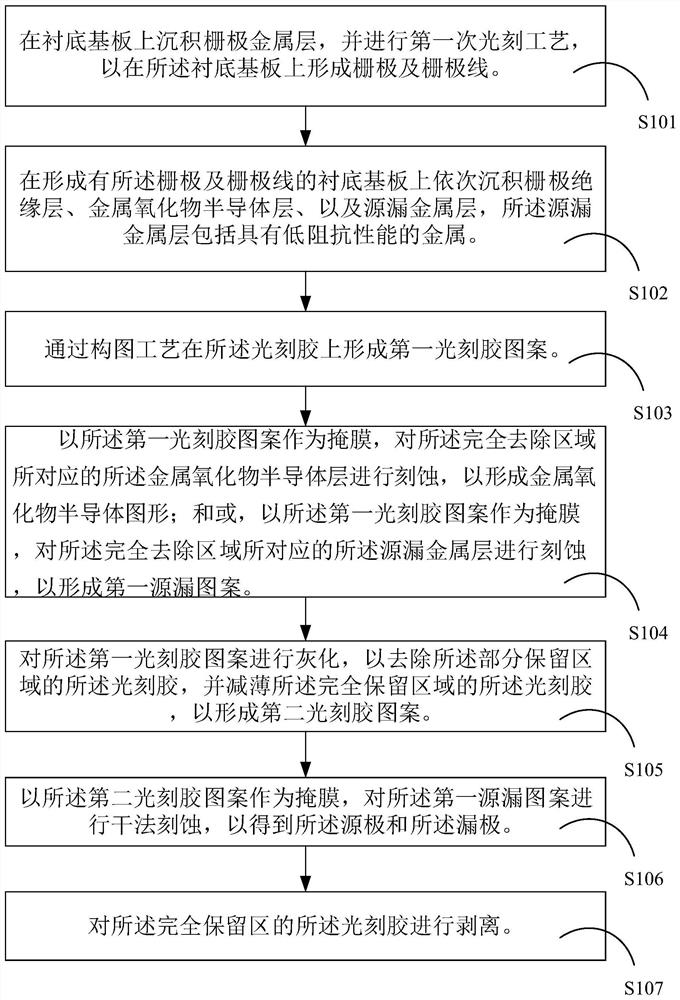

Array substrate manufacturing method and array substrate

ActiveCN112309970AReduce manufacturing costReduce thicknessSolid-state devicesSemiconductor/solid-state device manufacturingMetallic materialsPhysical chemistry

The invention provides an array substrate manufacturing method and an array substrate. The array substrate manufacturing method comprises the steps: sequentially depositing a grid electrode, a grid electrode insulating layer, a metal oxide semiconductor layer and a source and drain metal layer on a substrate, enabling an impedance value per square of a metal material of the source and drain metallayer to be lower than 0.08 ohm / m<2>, and enabling the thickness of the source and drain metal layer to be 100nm-300nm; forming a first photoresist pattern on the source and drain metal layer; carrying out primary wet etching on the metal oxide semiconductor layer and the source and drain metal layer; performing primary ashing processing on the first photoresist pattern to form a second photoresist pattern; and performing primary dry etching on the patterned source and drain metal layer to form a channel. According to the manufacturing method of the array substrate and the array substrate provided by the invention, a risks of a parasitic capacitance and the like of a product can be reduced.

Owner:CHENGDU ZHONGDIAN PANDA DISPLAY TECH CO LTD

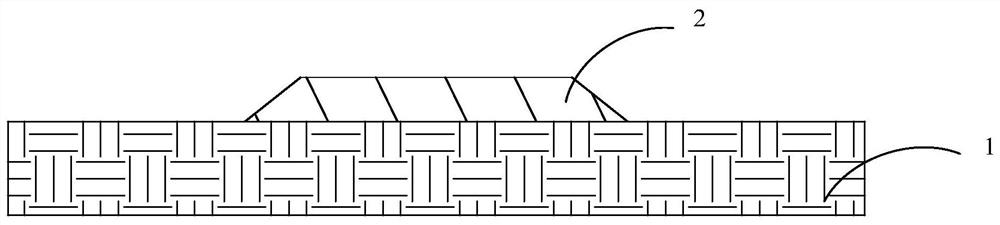

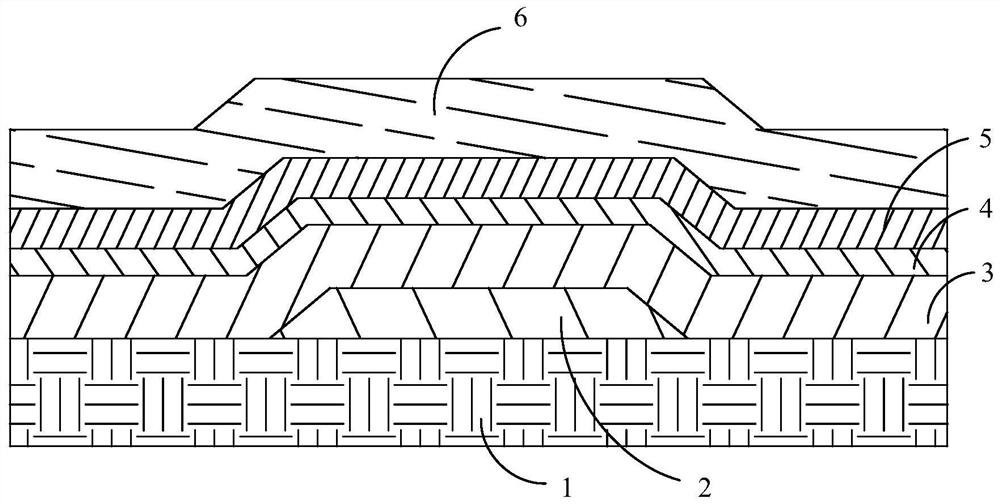

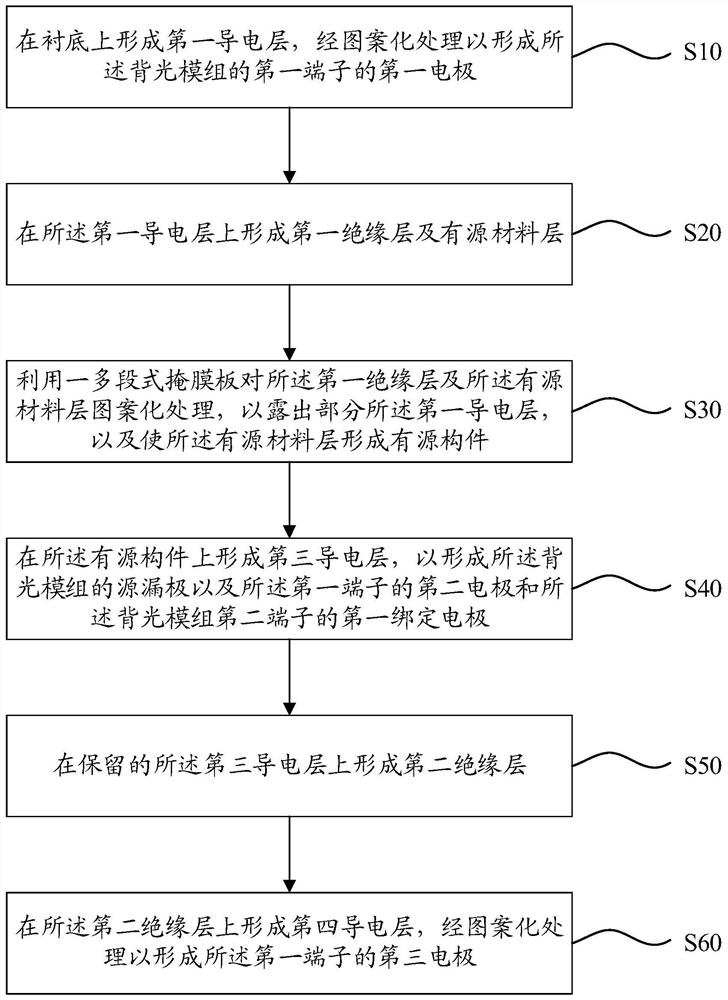

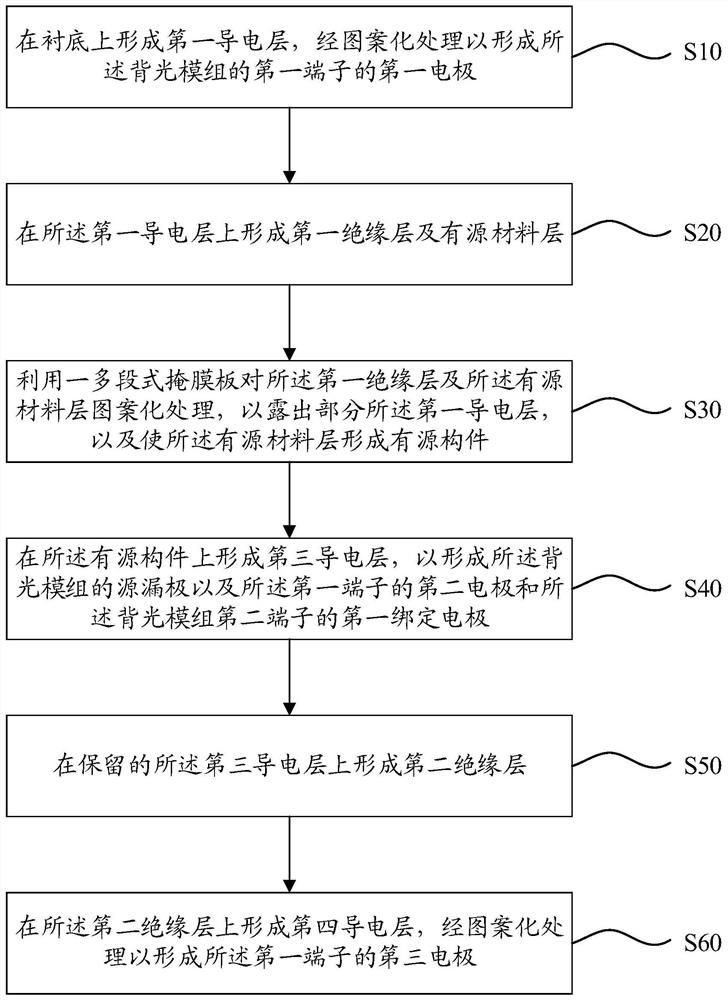

Backlight module and manufacturing method thereof

ActiveCN112309967AReduce the number of etchSimplify processing difficultySolid-state devicesSemiconductor/solid-state device manufacturingFlexible circuitsSource material

The invention provides a manufacturing method of a backlight module. The manufacturing method comprises the steps: forming a first conducting layer and a first insulating layer on a substrate; formingan active material layer on the first insulating layer; patterning the first insulating layer and the active material layer by using a multi-section mask plate so as to expose part of the first conducting layer and enable the active material layer to form an active member; and forming a third conducting layer on the active member to form a source electrode and a drain electrode of the backlight module. According to the invention, the openings of the active member and the first electrode of the binding terminal of the flexible circuit board are simultaneously formed by using the multi-sectionmask plate, so that the third conducting layer can simultaneously form the source and drain electrodes, the second electrode of the binding terminal of the flexible circuit board and the binding end of the light-emitting element, the etching frequency of a manufacturing process is reduced, the process difficulty of the backlight module is simplified, and the process efficiency is improved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Preparation method of semiconductor device

ActiveCN110707089AReduce depositionReduce the number of etchSolid-state devicesSemiconductor devicesVertical planeDevice material

The invention provides a preparation method of a semiconductor device, and the preparation method comprises the following steps: providing a substrate, forming N layers of steps at the end part of thesubstrate, and connecting the horizontal plane of one layer of step with the vertical plane of the adjacent layer of step to form a corner; forming a barrier layer on the top surface of the substrate; forming a protective layer covering the corner, the protective layer having a side portion covering the vertical surface and an extension portion extending in a direction away from the vertical surface, the extension portion covering a part of the horizontal surface; etching the substrate by taking the barrier layer and the protective layer as masks to form a new step; and after the extension part is removed, continuously etching the substrate along the barrier layer and the protective layer so as to form a new step again. The technical problems that due to the fact that the number of timesof exposure and etching is large, the preparation speed of the three-dimensional memory is low, and the preparation cost is increased are solved.

Owner:YANGTZE MEMORY TECH CO LTD

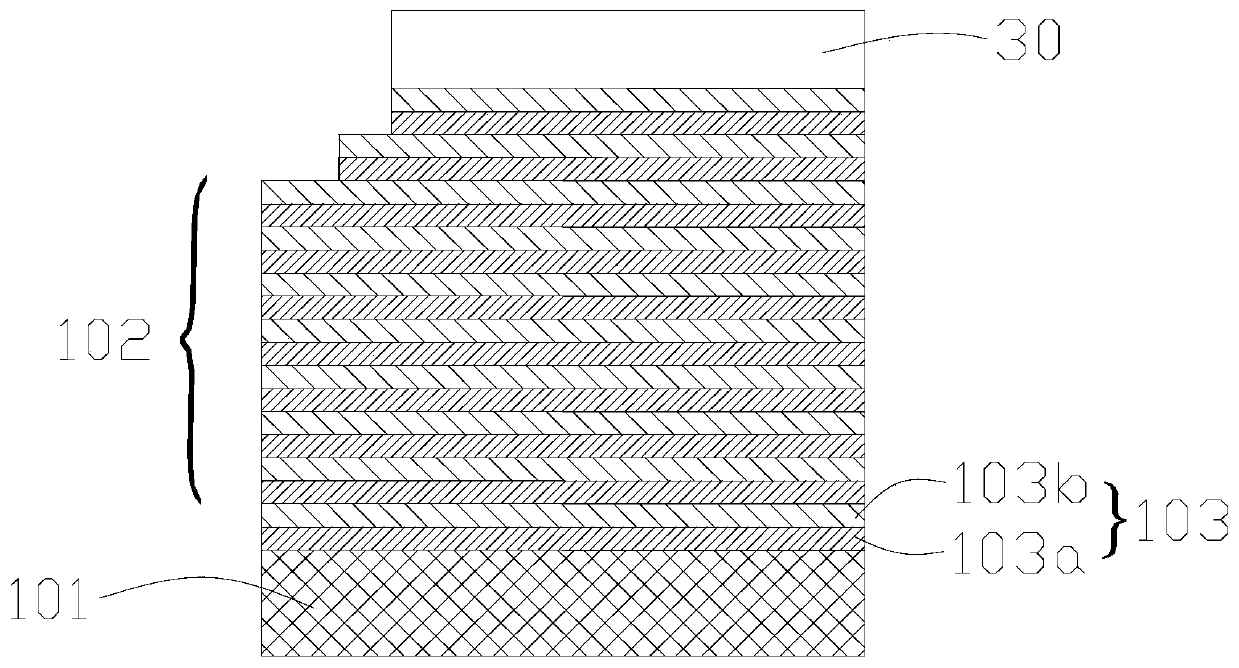

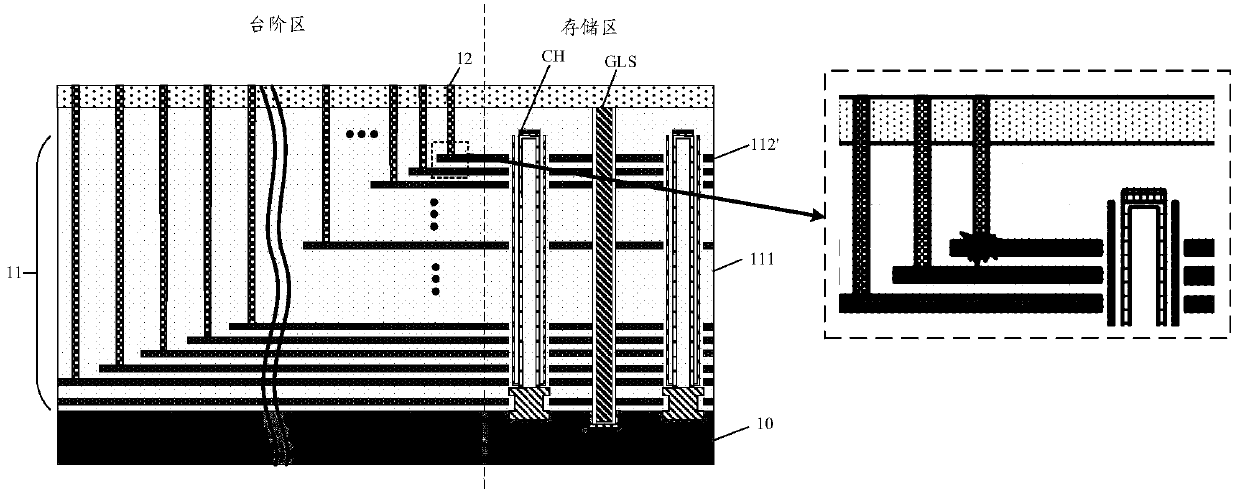

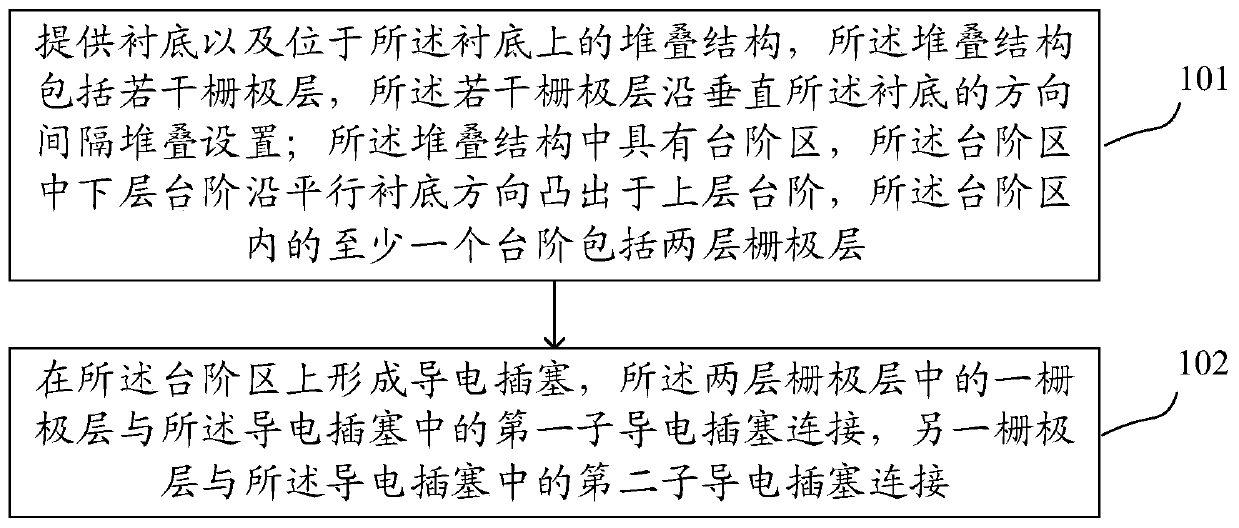

A kind of three-dimensional memory and its preparation method

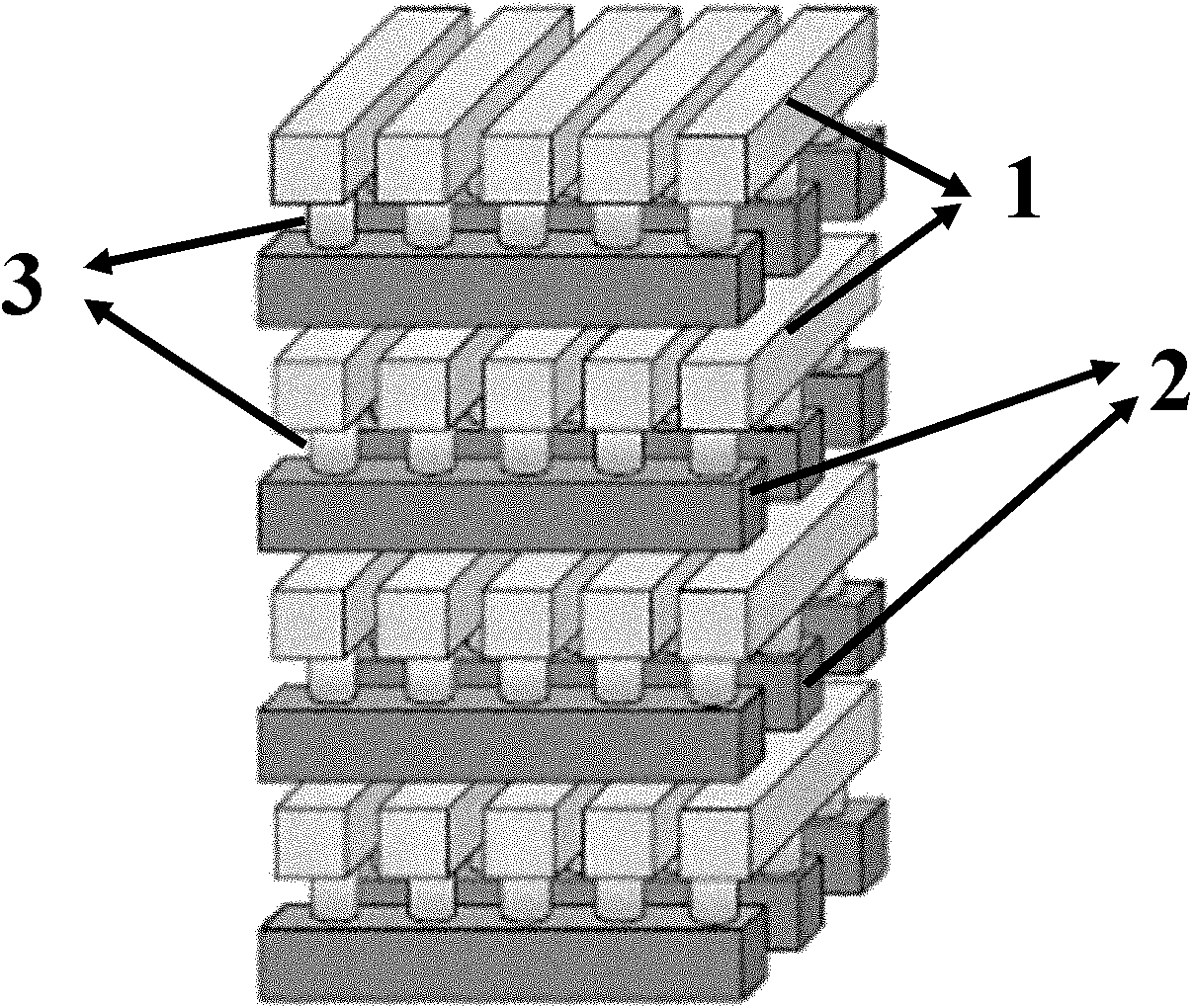

ActiveCN110335868BReduce the number of stepsReduce exposureSolid-state devicesSemiconductor devicesCondensed matter physicsMaterials science

The embodiment of the present invention discloses a three-dimensional memory, including: a substrate, and a stacked structure on the substrate; the stacked structure includes several gate layers, and the several gate layers are arranged along the The direction is stacked at intervals; the stacked structure has a step area, and the lower step in the step area protrudes from the upper step along the direction parallel to the substrate; at least one step in the step area includes two gate layers, the One of the two gate layers is connected to the first sub-conductive plug, and the other gate layer is connected to the second sub-conductive plug. In addition, the embodiment of the invention also discloses a method for preparing a three-dimensional memory.

Owner:YANGTZE MEMORY TECH CO LTD

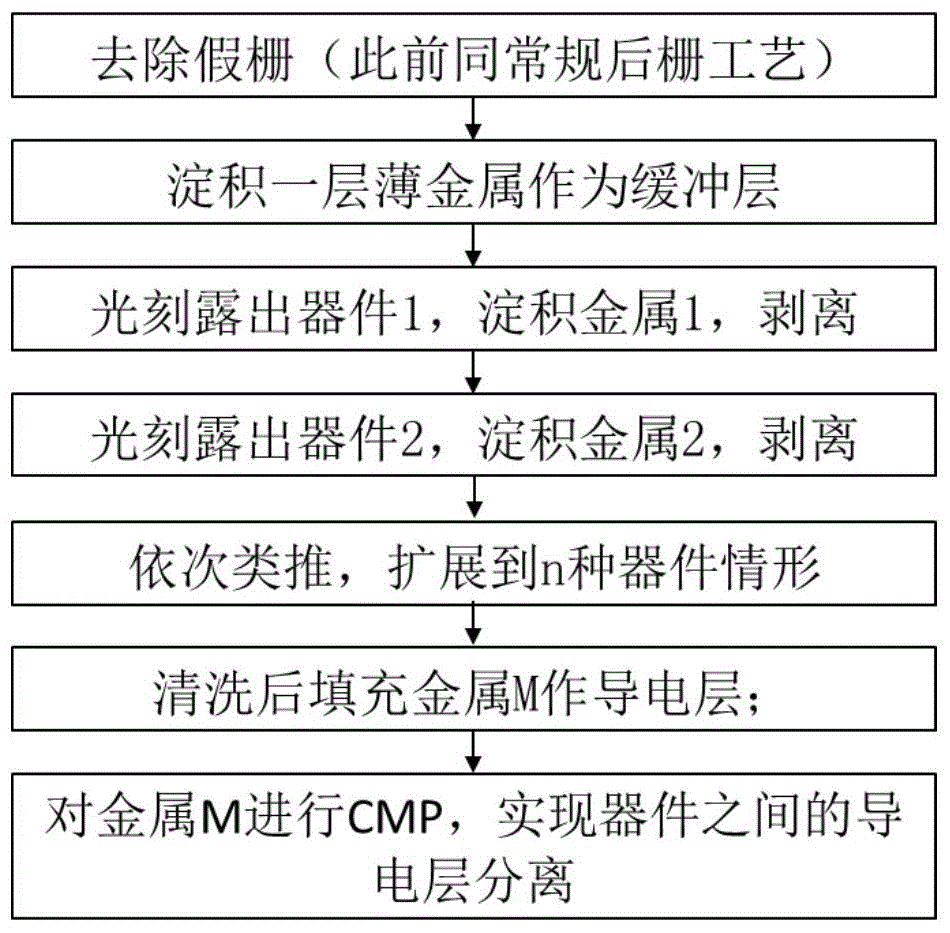

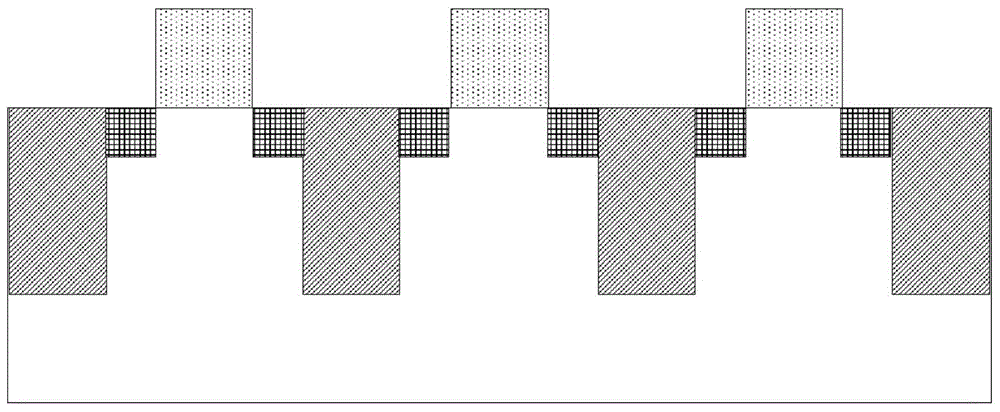

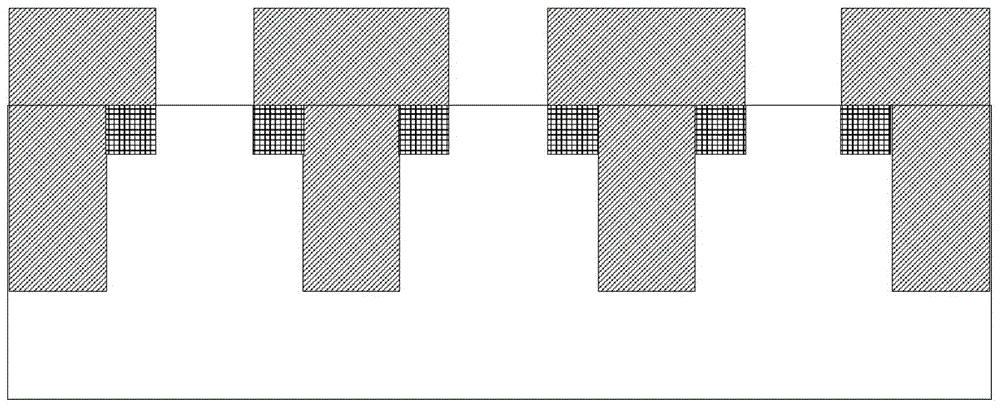

Integrating method for multiple metal gates

InactiveCN105206575AReduce the number of etchingReduce etch damageSemiconductor/solid-state device manufacturingIntegrated circuit manufacturingControllability

The invention discloses an integrating method for multiple metal gates, and belongs to the technical field of super-large-scale integrated circuit manufacturing. The integrating method for the multiple metal gates is achieved on the basis of successive stripping of an undergate technology by adopting a stripping technology. Compared with a depositing-annealing alloy method of Takashi Matsukawa and the like, the method has the advantages that no additional heat budget exists, the uniformity and controllability of the technology are improved, etching damage is reduced, the technological difficulty is reduced, and the material selection range is widened.

Owner:PEKING UNIV

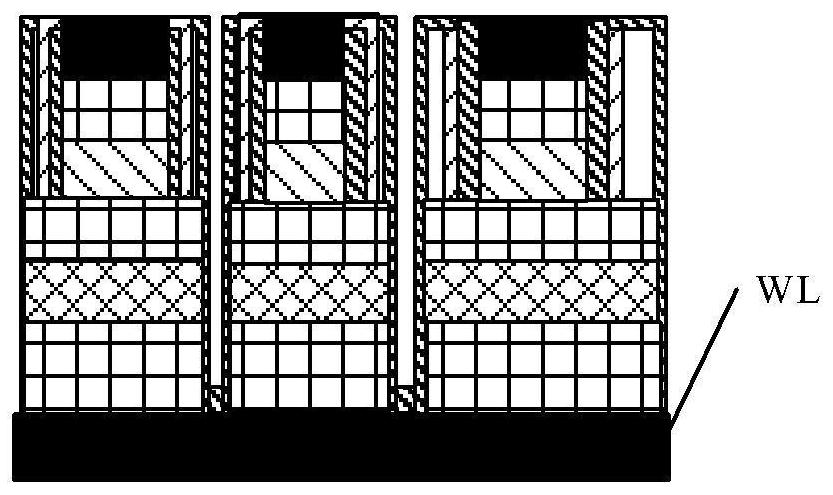

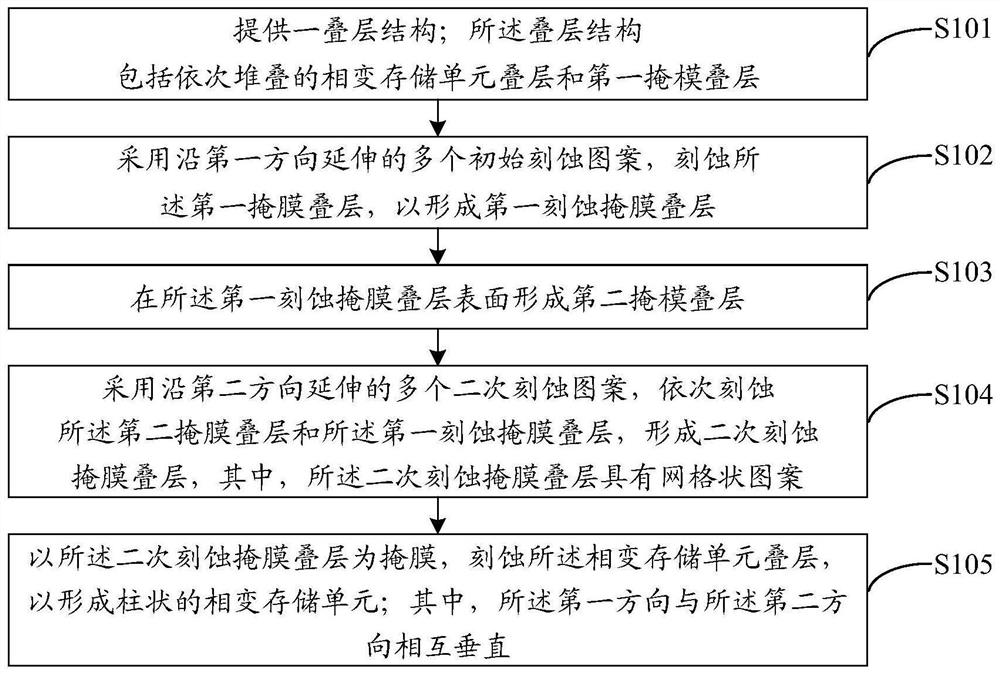

Forming method of three-dimensional phase change memory and three-dimensional phase change memory

PendingCN114512600AReduce the number of etchReduce sedimentationSolid-state devicesSemiconductor devicesPhase-change memoryMechanical engineering

The embodiment of the invention provides a forming method of a three-dimensional phase change memory and the three-dimensional phase change memory, and the method comprises the steps: employing a plurality of initial etching patterns which extend along a first direction, and etching a first mask lamination layer, so as to form a first etching mask lamination layer; forming a second mask lamination layer on the surface of the first etching mask lamination layer; a plurality of secondary etching patterns extending in the second direction are adopted, the second mask lamination layer and the first etching mask lamination layer are etched in sequence, a secondary etching mask lamination layer is formed, and the secondary etching mask lamination layer is provided with latticed patterns; and etching the phase change storage unit lamination layer by taking the secondary etching mask lamination layer as a mask so as to form a columnar phase change storage unit.

Owner:YANGTZE ADVANCED MEMORY INDUSTRIAL INNOVATION CENTER CO LTD

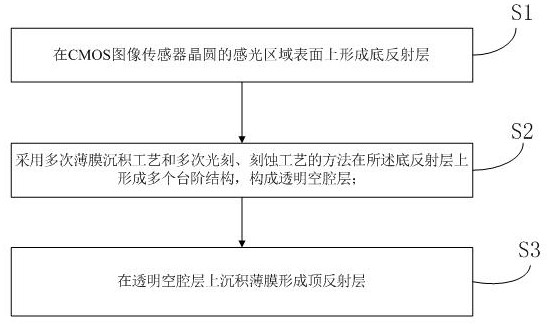

A hyperspectral image sensor monolithic integration method, sensor and imaging device

The invention provides a monolithic integration method of a hyperspectral image sensor, comprising: forming a bottom reflection layer on the surface of the photosensitive area of a CMOS image sensor wafer; adopting multiple thin film deposition processes and multiple photolithography and etching processes A plurality of stepped structures are formed on the bottom reflective layer to form a transparent cavity layer; a thin film is deposited on the transparent cavity layer to form a top reflective layer. The monolithic integration method of the hyperspectral image sensor provided by the present invention realizes the precise control of the thickness of each step of the transparent cavity layer by controlling the thin film deposition process conditions, and optimizes the accumulation of inhomogeneity caused by the etching process in the prior art The problem. The invention also provides a hyperspectral image sensor and an imaging device containing the hyperspectral image sensor.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Three-dimensional memory and method of forming the same

ActiveCN110444544BSimple manufacturing processReduce manufacturing costSolid-state devicesSemiconductor devicesManufacturing technologyEngineering physics

The invention relates to the technical field of semiconductor manufacturing, in particular to a three-dimensional memory and a forming method thereof. The forming method of the three-dimensional memory includes the following steps: providing a substrate with a stacked layer on the substrate, the stacked layer including a core area and a stepped area located at the periphery of the core area; The stepped area; forming a plurality of sub-regions arranged along the first direction in the partitioned stepped structure region, each of the sub-regions includes a plurality of sub-structures arranged in a step-like manner along the first direction, and each of the The substructures are multi-level ladders arranged along the second direction, and the heights of the steps in any two sub-regions are different. The invention simplifies the manufacturing process of the three-dimensional memory, reduces the manufacturing cost of the three-dimensional memory, and simultaneously realizes the improvement of the performance of the three-dimensional memory.

Owner:YANGTZE MEMORY TECH CO LTD

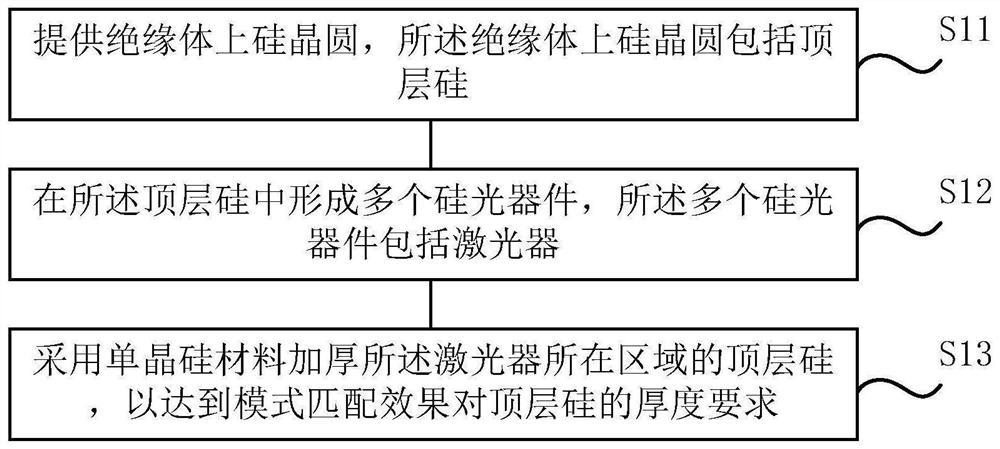

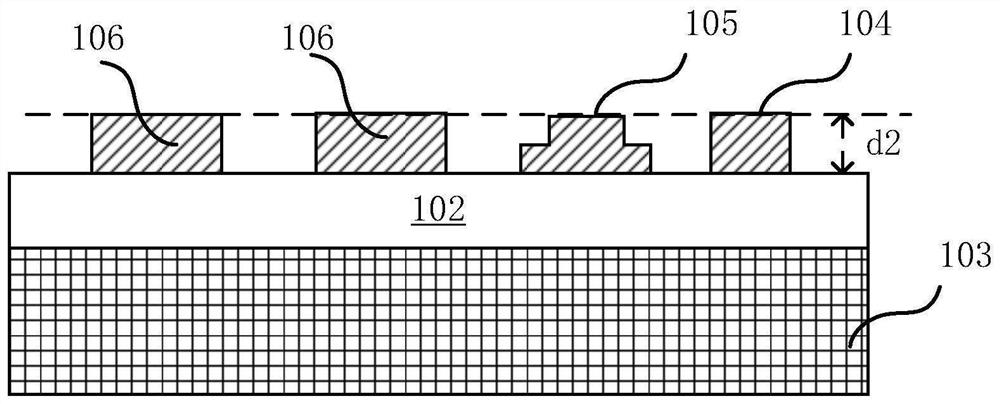

Semiconductor device and preparation method thereof

PendingCN111785679AReduce manufacturing costAvoid it happening againSemiconductor/solid-state device manufacturingDevice materialEngineering

The invention discloses a semiconductor device and a preparation method thereof, and the method comprises the following steps: providing a silicon-on-insulator wafer which comprises top silicon; forming a plurality of silicon optical devices in the top silicon, wherein the plurality of silicon optical devices comprise lasers; and thickening the top silicon of the area where the laser is located soas to meet the requirement of the mode matching effect on the thickness of the top silicon.

Owner:UNITED MICROELECTRONICS CENT CO LTD

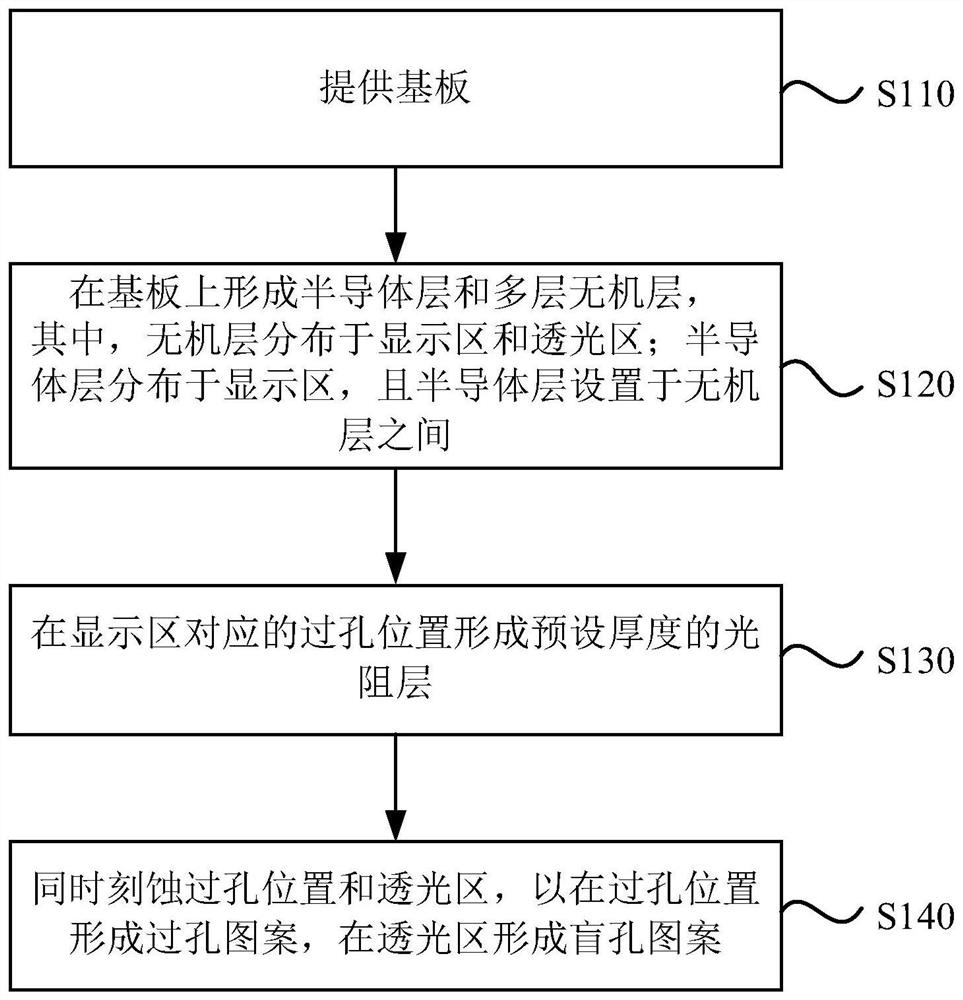

Manufacturing method of display panel and display panel

PendingCN113053983AReduce the number of etchReduce complexitySolid-state devicesSemiconductor devicesPhysicsPhotoresist

The embodiment of the invention discloses a manufacturing method of a display panel and the display panel. The manufacturing method of the display panel comprises the steps that a substrate is provided; a semiconductor layer and a plurality of inorganic layers are formed on the substrate, and the inorganic layers are distributed in a display area and a light-transmitting area; the semiconductor layer is distributed in the display area and is arranged between the inorganic layers; a photoresist layer with a preset thickness is formed at the position of the via hole corresponding to the display area; and the via hole position and the light-transmitting area are etched at the same time so as to form a via hole pattern at the via hole position and form a blind hole pattern in the light-transmitting area. Compared with the prior art, the technical scheme provided by the embodiment of the invention can simultaneously etch the via hole position and the light-transmitting area through one etching process to respectively form the via hole pattern and the blind hole pattern so that the etching times when the hole areas are formed at different positions can be reduced in the manufacturing process of the display panel, the complexity of the etching process is reduced, and the manufacturing efficiency of the display panel is improved.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

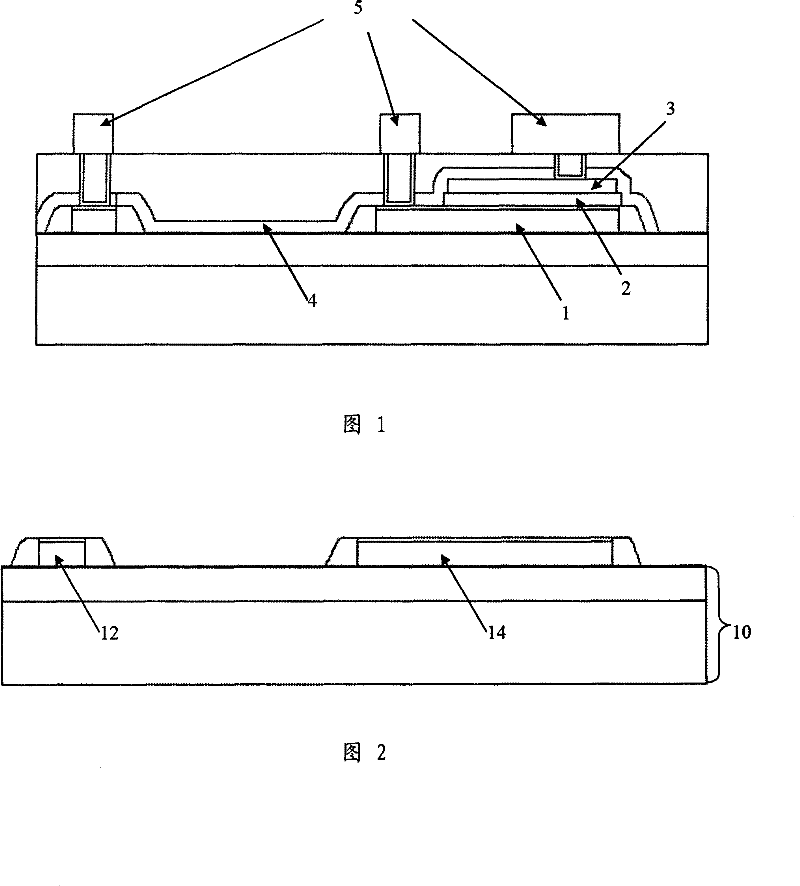

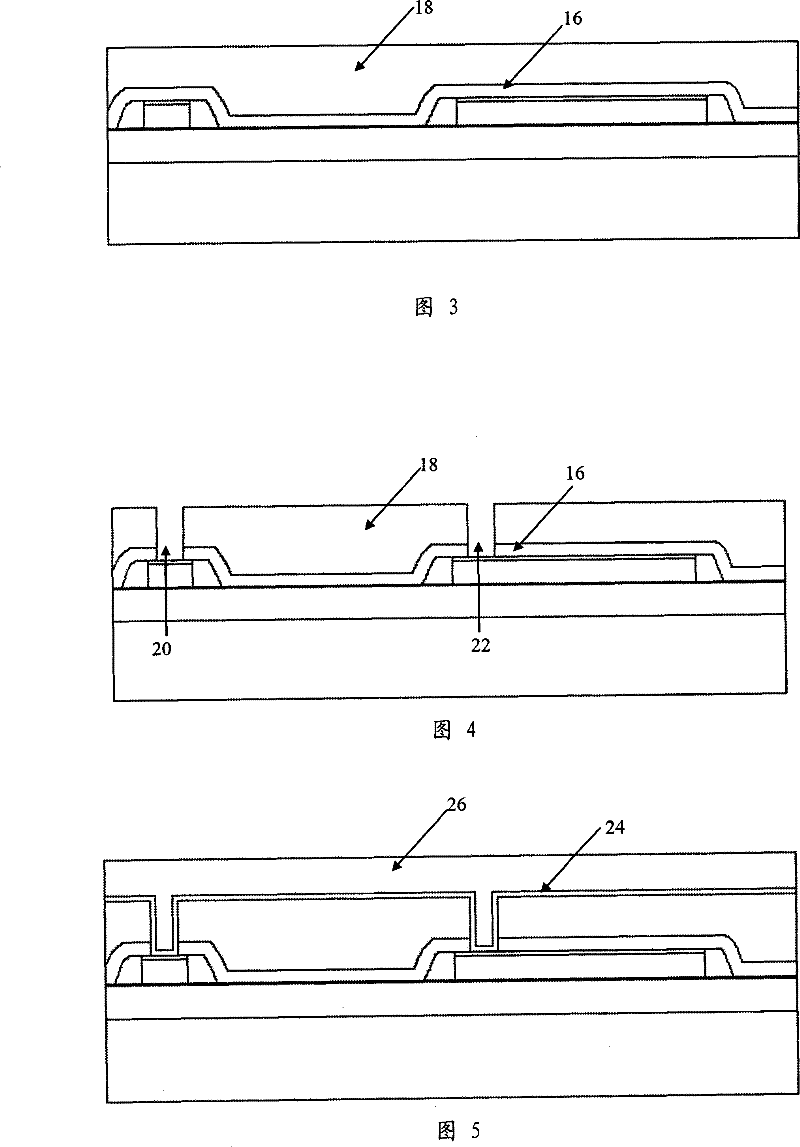

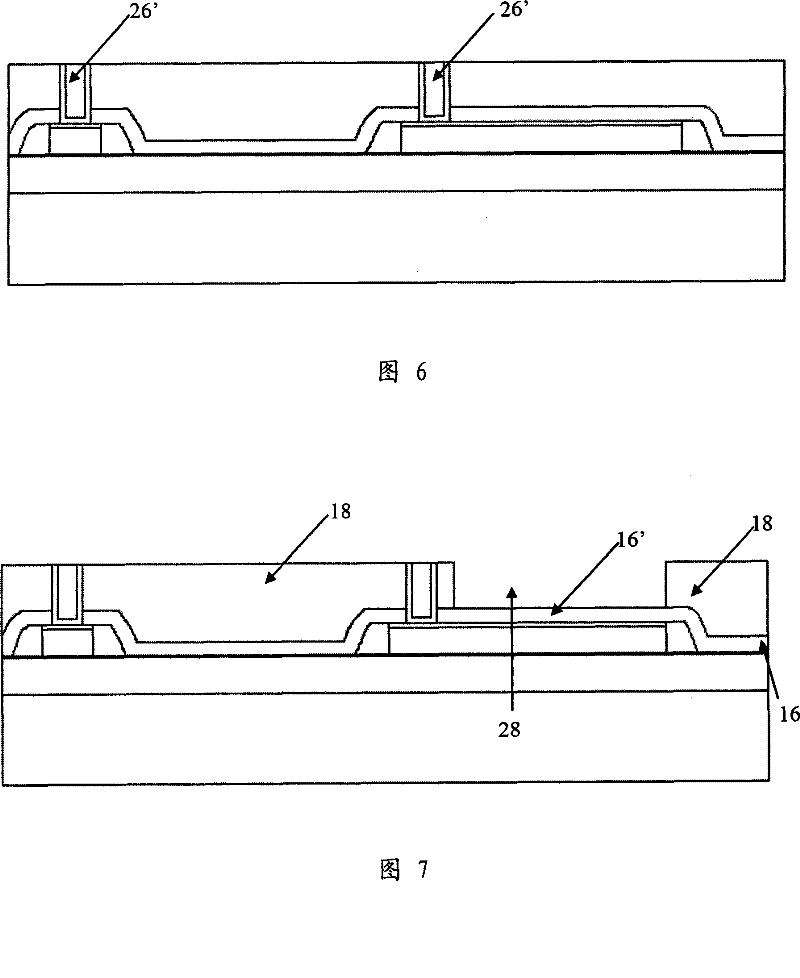

Process for Damascus

ActiveCN101546727BReduce developmentReduce the number of etchSemiconductor/solid-state device manufacturingInter layerMedia layer

The invention discloses a process for Damascus, which can reduce the times of the development and etching in the process of forming grooves or inter-layered through holes on a substrate. The process comprises the following steps: (1) continuously carrying out exposure processing on a plurality of photoresist layers without development processing so as to form an exposure area; (2) carrying out the development processing on the exposure area so as to obtain a development area corresponding to the exposure area; and (3) etching a medium layer through the development area to form the required grooves or through holes. The process carries out the development and etching for one time on the exposure area obtained after multiple times of the exposure processing so as to obtain the required grooves or the through holes. Compared the prior art, the process centralizes to complete the development processing after each time of exposure processing at a time, thereby reducing the times of the development and etching and improving the efficiency.

Owner:SEMICON MFG INT (SHANGHAI) CORP

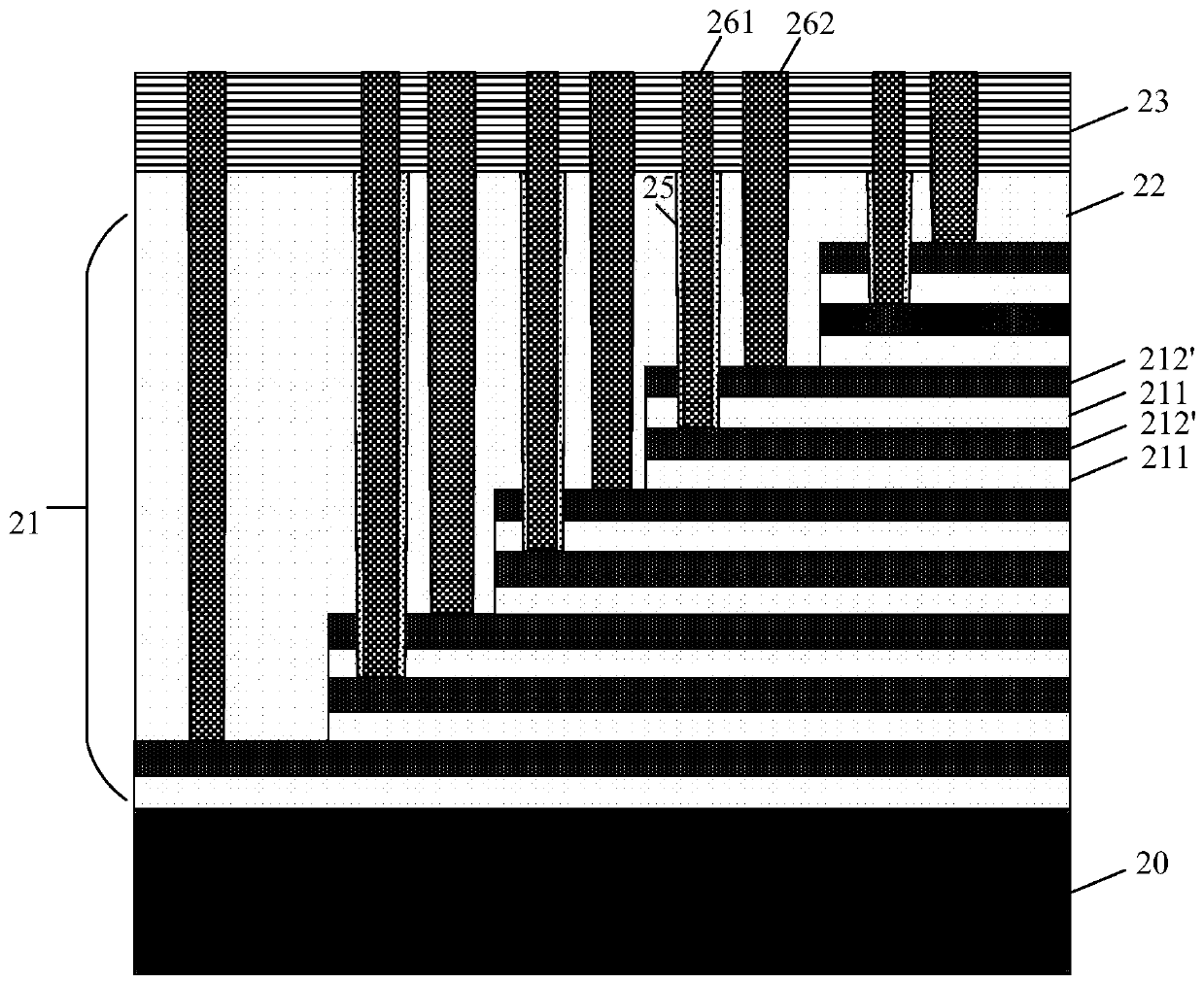

Three-dimensional memory and method of forming the same

ActiveCN110534527BSimple manufacturing processReduce manufacturing costSolid-state devicesSemiconductor devicesManufacturing technologyEngineering physics

The present invention relates to the technical field of semiconductor manufacturing, and in particular, to a three-dimensional memory and a method for forming the same. The method for forming the three-dimensional memory includes the following steps: providing a substrate with a stack layer on the substrate, the stack layer including a core region and a stepped region distributed around the periphery of the core region; forming a plurality of partitioned stepped structure regions in the stepped area; a plurality of sub-partition structures arranged along a first direction are formed in the sub-division stepped structure area, and the heights of the plurality of the sub-partition structures are gradually changed along the first direction, and the first direction is the The stepped area points in the direction of the core area. The invention can reduce the number of masks and the times of etching, thereby simplifying the manufacturing process of the three-dimensional memory and reducing the manufacturing cost of the three-dimensional memory.

Owner:YANGTZE MEMORY TECH CO LTD

Backlight module and manufacturing method thereof

ActiveCN112309967BReduce the number of etchSimplify processing difficultySolid-state devicesSemiconductor/solid-state device manufacturingFlexible circuitsSource material

The present application proposes a method for manufacturing a backlight module, including: forming a first conductive layer and a first insulating layer on a substrate; forming an active material layer on the first insulating layer; using a multi-stage mask patterning the first insulating layer and the active material layer to expose part of the first conductive layer, and making the active material layer form an active component; forming a third conductive layer on the active component , to form the source and drain of the backlight module. In this application, a multi-segment mask is used to simultaneously form the active component and the opening of the first electrode of the binding terminal of the flexible circuit board, so that the third conductive layer can simultaneously form the source and drain electrodes and the opening of the binding terminal of the flexible circuit board. The second electrode and the binding end of the light-emitting element reduce the etching times of the manufacturing process, simplify the process difficulty of the backlight module, and improve the process efficiency.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Memory array structure and manufacturing method, memory and writing method and reading method

ActiveCN109860192BGuaranteed working voltageSimple manufacturing processSolid-state devicesSemiconductor devicesComputer architectureMagnetic memory

The invention provides a storage array structure and preparation method, memory, writing method and reading method. The array structure includes: at least one storage unit, including superconducting devices and magnetic storage devices stacked in series; at least one superconducting upper electrode , is arranged above the memory unit, at least one superconducting lower electrode is arranged below the memory unit, at least one superconducting word line is arranged above the memory unit, or is arranged below the memory unit, and the superconducting word line is close to the superconducting electrode in the memory unit. Guide device settings. The invention organically combines a magnetic memory device with a superconducting integrated circuit, and uses the superconducting device to realize the switching effect of the circuit, thereby replacing the CMOS logic circuit, enabling the memory to work at low temperatures, and ensuring that the MRAM can achieve high speed and high speed at low operating voltage. High-density storage realizes the above work based on different writing methods, forming an information reading method suitable for superconducting logic processes. The structural design is simple, which is beneficial to reducing the number of etching times.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

A mim capacitor and its manufacturing method

ActiveCN111199953BReduce photolithography processReduce the number of etchSemiconductor/solid-state device detailsSolid-state devicesCapacitanceEtching

The present invention provides a MIM capacitor and a manufacturing method thereof, the manufacturing method comprising: providing a semiconductor substrate, forming a first metal layer on the semiconductor substrate; forming an anti-reflection layer on the first metal layer; Engraving and etching the first metal layer and the anti-reflection layer to define a MIM capacitor area, the first metal layer in the MIM capacitor area serves as the lower plate of the MIM capacitor, and in the MIM capacitor area The anti-reflection layer is used as the dielectric layer of the MIM capacitor; the upper plate of the MIM capacitor is formed on the anti-reflection layer in the region of the MIM capacitor. In the manufacturing method of the present invention, the anti-reflection layer retained in the etched area is used as the dielectric layer of the capacitor at the same time, and the metal is continued to be filled in the etched area as the upper plate, and no additional dielectric layer of the capacitor is required. , and no additional photolithography process is required to define the upper plate area, reducing the number of photolithography and etching, thereby reducing the process cost and shortening the process cycle.

Owner:CSMC TECH FAB2 CO LTD

Method for forming interlaminar capacitor

InactiveCN101197256BReduce depositionReduce the number of etchSemiconductor/solid-state device manufacturingDielectricEtching

The invention discloses a forming method of layer capacitor, which uses an etch stop layer as capacitor medium without extra medium layer to deposit and form the capacitor medium, and form an upper metal connecting line and a capacitor upper pole plate by using the same metal layer. The method specifically comprises the following steps of: depositing the etch stop layer and an inter-level dielectrics film after a capacitor lower pole plate is formed; a capacitor plate groove is formed in the inter-level dielectrics firm by etching, wherein, the capacitor plate groove passes the inter-level dielectrics film and stops at the etch stop layer and part of the etch stop layer is exposed, and further the exposed etch stop layer is used as the capacitor medium; and forming the capacitor upper pole plate in the capacitor plate groove. Compared with the prior art, the invention reduces times for depositing and etching and simplifies the process flow.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

A kind of preparation method of junction terminal of sic high voltage power device

InactiveCN107546114BHigh blocking voltageReduce the number of etchSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingPhysical chemistry

The invention discloses a preparation method of a SiC high-voltage power device junction terminal. Firstly, according to blocking voltage requirement of different levels, a number (2n) of steps is determined and the mask pattern structure design is carried out; then a multi-level step structure is formed on a SiC sample through multiple times of step preparation process (including preparing a hardmask layer, etching a step region, and removing a silicon oxide hard mask layer), and finally steps of 2n levels are formed through (n+1) times of step etching. For making the SiC high-voltage powerdevice junction terminal with the steps of multiple levels, the terminal can be prepared only with very few times of step etching, thus while the steps of multiple levels can be realized and SiC high-voltage power device blocking voltage is greatly raised, the preparation process of the multi-step junction terminal can be greatly simplified, and thus the method has a great application prospect inthe SiC high-voltage power device.

Owner:INST OF ELECTRONICS ENG CHINA ACAD OF ENG PHYSICS

Formation method of semiconductor structure

PendingCN113808998AHigh graphic precisionImprove performance and reliabilitySemiconductor/solid-state device manufacturingDopingSemiconductor structure

A method for forming a semiconductor structure comprises the following steps: providing a substrate which comprises a first region and a second region; forming a plurality of source-drain doping layers, a plurality of gate structures and an initial first dielectric layer in the substrate in the first region and the second region respectively; forming a first mask layer on the surface of the initial first dielectric layer, wherein a plurality of first openings are formed in the first mask layer on the first region and the first mask layer on the second region respectively, the first openings are located in the source-drain doping layer, and the density of the first openings in the first region is different from the density of the first openings in the second region; and forming a plurality of second openings in the first mask layer of the first region and the second region, wherein the second openings are located on the gate structure. Therefore, the performance and the reliability of the semiconductor structure are improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

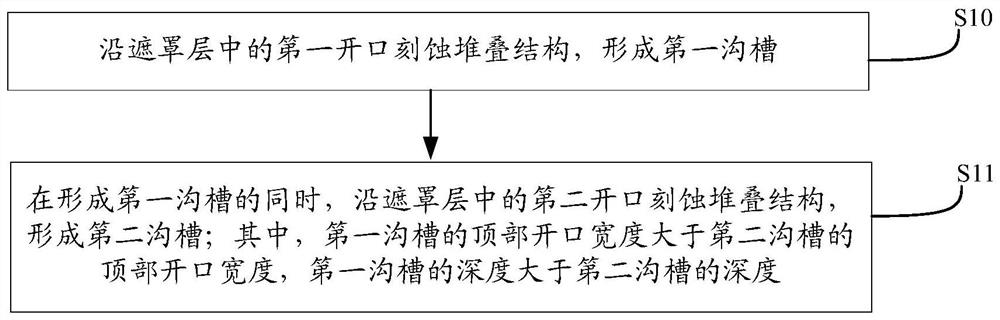

Formation method of three-dimensional memory

ActiveCN110391251BReduce in quantityReduce the number of etchSolid-state devicesSemiconductor devicesEngineering physicsMaterials science

The embodiment of the present invention discloses a method for forming a three-dimensional memory, the forming method comprising: etching the stack structure along the first opening in the mask layer to form a first trench; while forming the first trench , etching the stacked structure along the second opening in the mask layer to form a second trench; wherein, the width of the top opening of the first trench is greater than the width of the top opening of the second trench, so The depth of the first groove is greater than the depth of the second groove.

Owner:YANGTZE MEMORY TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com