A high-speed and low-power level shift circuit

A technology of level shift circuit and low power consumption, which is applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, electronic switches, etc. Increased circuit power consumption and other issues to achieve the effect of increasing the maximum operating frequency, reducing chip power consumption, and reducing turn-off and turn-on time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

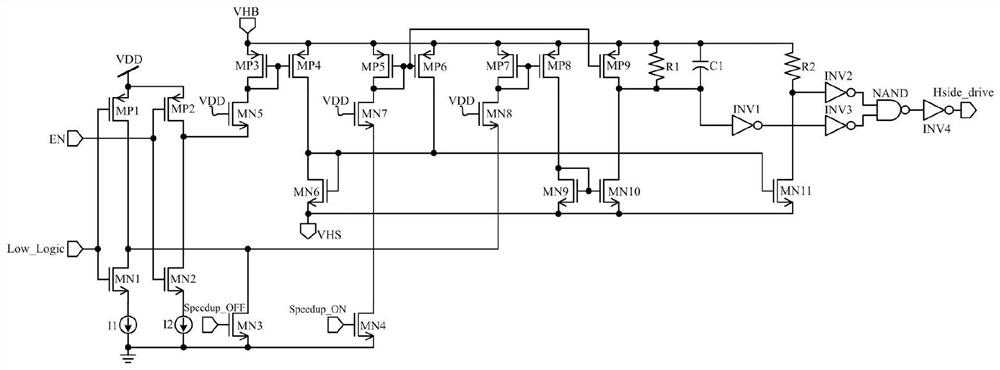

[0025] The present invention provides a high-speed and low-power level shift circuit, the structure of which is as follows: figure 2 shown. The high-speed and low-power level shift circuit includes: resistors R1-R2, capacitors C1, NMOS transistors MN1-MN11, PMOS transistors MP1-MP9, current sources I1-I2, inverters INV1-INV4 and dual-input NAND gates NAND1.

[0026]Specifically, the resistor R1 is connected in parallel with the two ends of the capacitor C1, and one end of the resistor R1 and the capacitor C1 is connected to the floating power supply VHB together, and the other end is connected to the input end of the inverter INV1; the drain ends of the NMOS transistor MN1 and the PMOS transistor MP1 Interconnection, the gate terminal is connected to the low-voltage control logic Low_Logic, the source terminal of the NMOS transistor MN1 is connected to the current source I1; the drain terminals of the NMOS transistor MN2 and the PMOS transistor MP2 are interconnected, and th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More