Detection method for electric connection defect of chip

A detection method and defect technology, which is applied in the directions of electronic circuit test, optical test defect/defect, electrical measurement, etc., can solve the problems of electrical connection structure defects, difficulty in meeting the requirements of failure analysis of three-dimensional storage devices, etc., and achieve reduction of superposition phenomenon, The effect of improving detection accuracy and improving detection efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

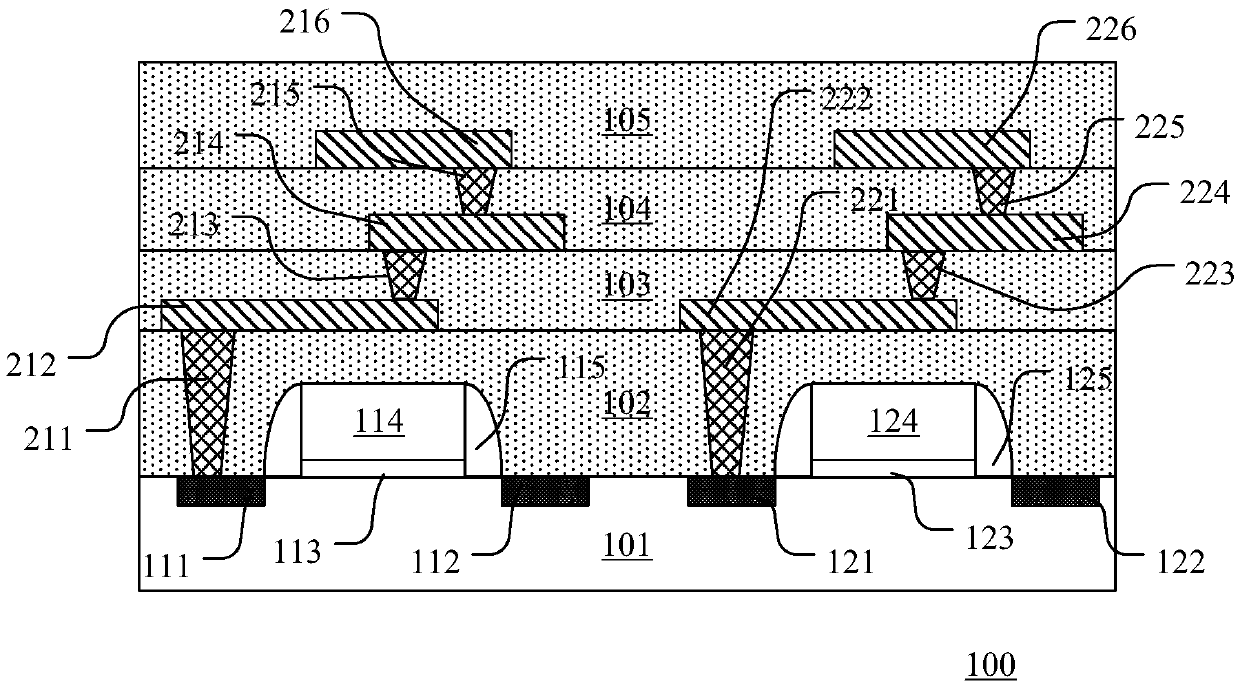

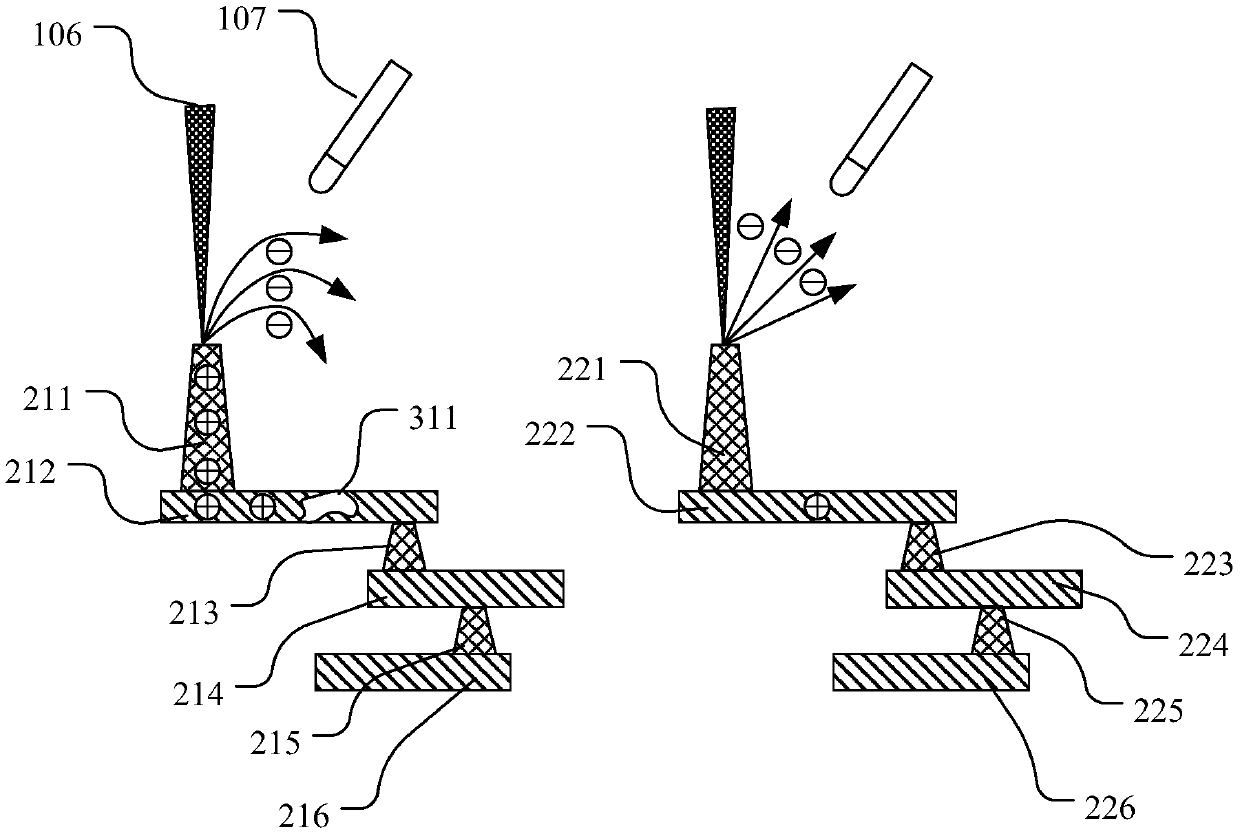

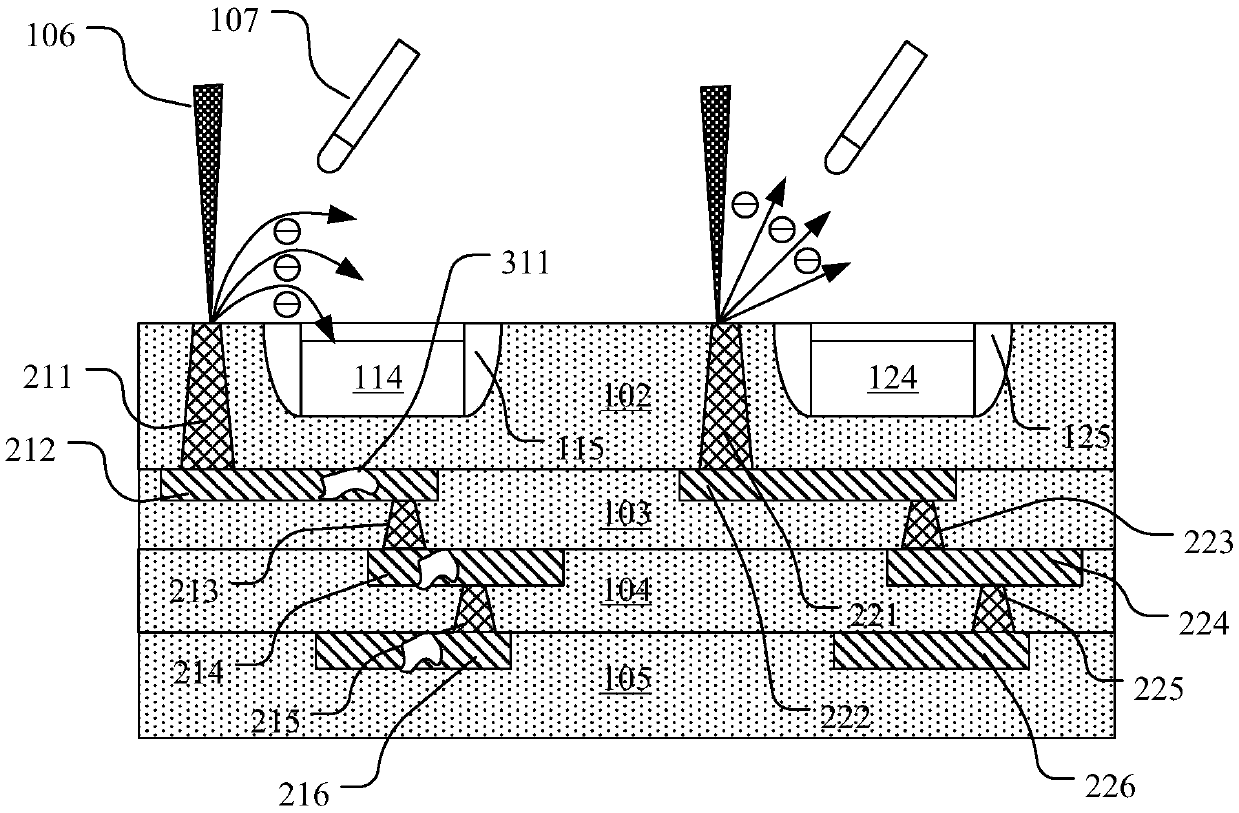

[0021] Hereinafter, the present invention will be described in more detail with reference to the accompanying drawings. In the various figures, identical elements are indicated with similar reference numerals. For the sake of clarity, various parts in the drawings have not been drawn to scale.

[0022] The inventors found that the detection of electrical connection defects using a nano-probe station can only obtain the detection results of the contact position, and the spatial resolution of the detection is limited by the size of the probe. For a chip with a large area, multi-point detection is required, resulting in a long detection time. too long. Therefore, it is difficult for nanoprobe stations to meet the large-area inspection requirements of three-dimensional memory devices. Scanning electron microscopy can be used to obtain the topography of the field of view, and the defect position can be found by observing the topography image of the chip layer by layer. The spati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More