Radio frequency chip system-level package structure with sealed casing made of metal and process thereof

A technology of system-level packaging and airtight housing, applied in the field of semiconductors, can solve problems such as high cost and complex implementation, and achieve the effects of airtightness, electromagnetic shielding, and circuit interconnection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

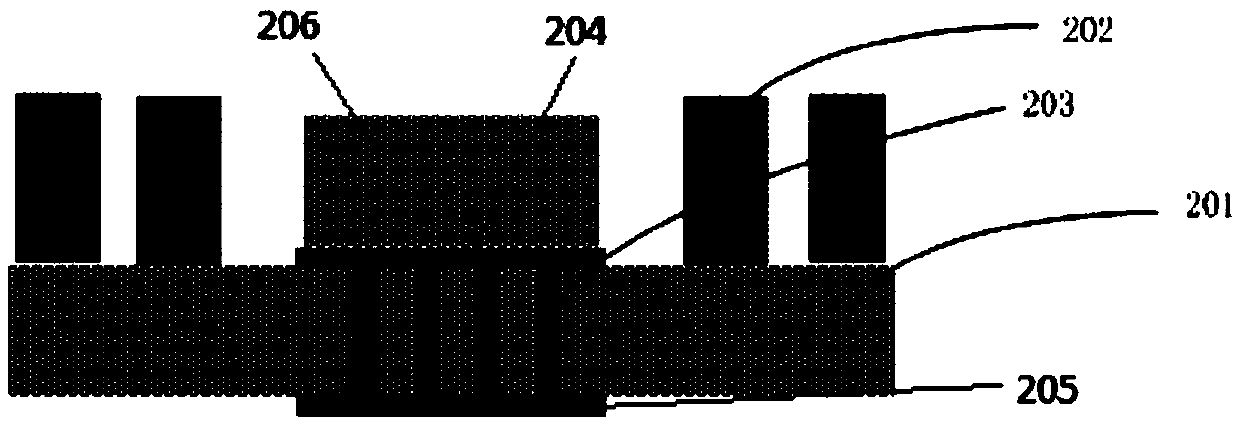

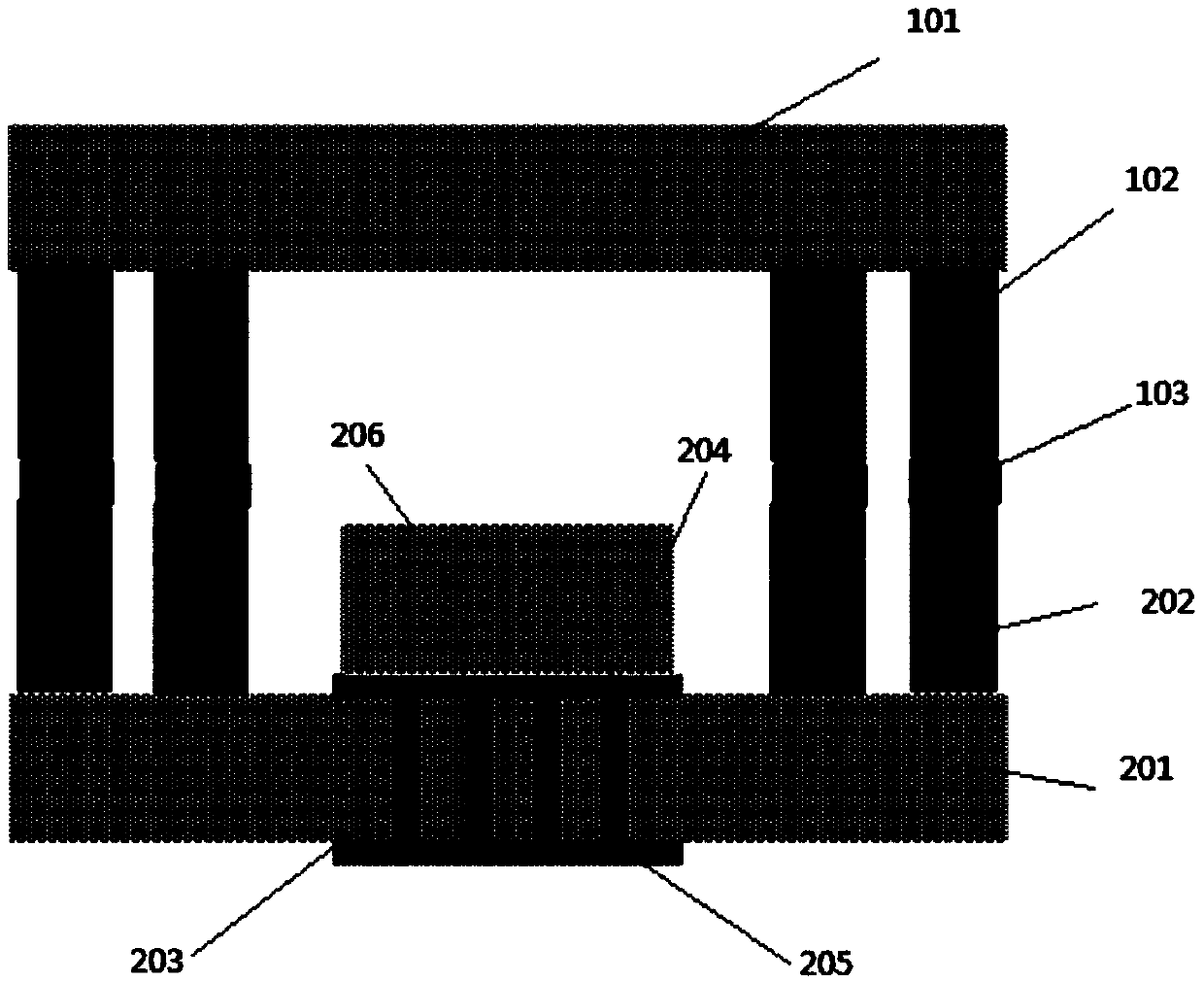

[0049] Embodiment 1, with reference to attached Figure 1-3 .

[0050] The present invention provides a radio frequency chip system-in-package structure with a metal airtight casing, including a base wafer 201 and a cover wafer 101, and the base wafer 201 and the cover wafer 101 are bonded together through a wafer-level process.

[0051] Both the outer surfaces of the base wafer 201 and the cover wafer 101 are provided with an insulating layer, and the middle part of the base wafer 201 is provided with a TSV layout area, and a plurality of TSV holes 203 arranged in parallel are provided in the TSV layout area. The hole 203 runs through the base wafer 201 in the thickness direction, copper is cast in the TSV hole 203 to form a TSV copper column, an upper RDL structure 204 is provided on the upper surface of the hole layout area, and a lower RDL structure 205 is provided on the lower surface of the hole layout area , the upper and lower ends of the TSV copper pillar are respect...

Embodiment 2

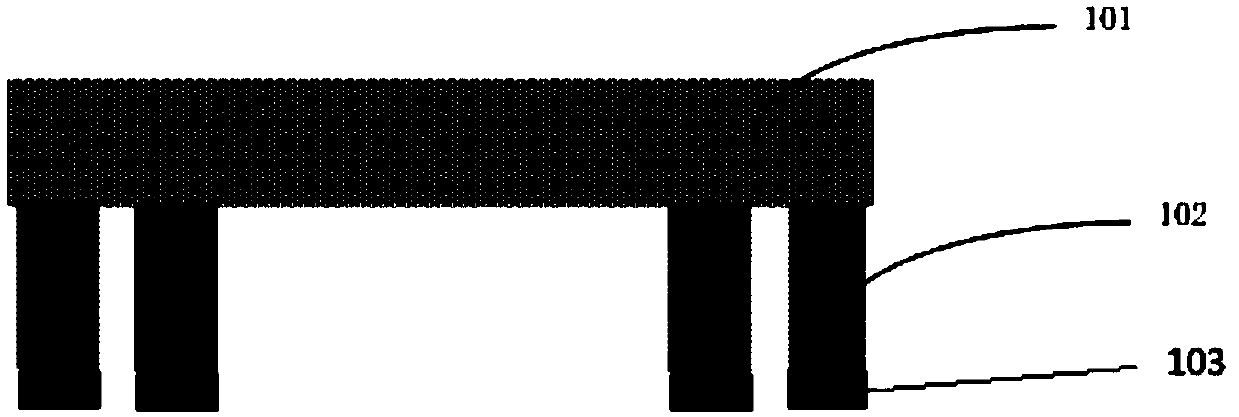

[0065] Embodiment 2, with reference to attached Figure 4-6 .

[0066] In this embodiment, the cover plate metal part 102 is a metal wall, and other implementation modes of this embodiment are the same as those in Embodiment 1.

Embodiment 3

[0067] Embodiment 3, with reference to attached Figure 7-9 .

[0068] In this embodiment, the base metal part 202 is a single row of metal pillars, and the arrangement direction of the metal pillars is perpendicular to the width direction of the metal wall. Other implementation modes of this embodiment are the same as those of Embodiment 2.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More