Same-frequency continuous serial data synchronization method and device

A serial data, synchronization device technology, applied in the direction of electrical digital data processing, digital computer parts, instruments, etc., can solve the problems of increasing clock tree consumption, single-shot data signal sampling error, data sampling error, etc., to improve sampling Accuracy, reduce chip cost, and ensure the effect of correctness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other.

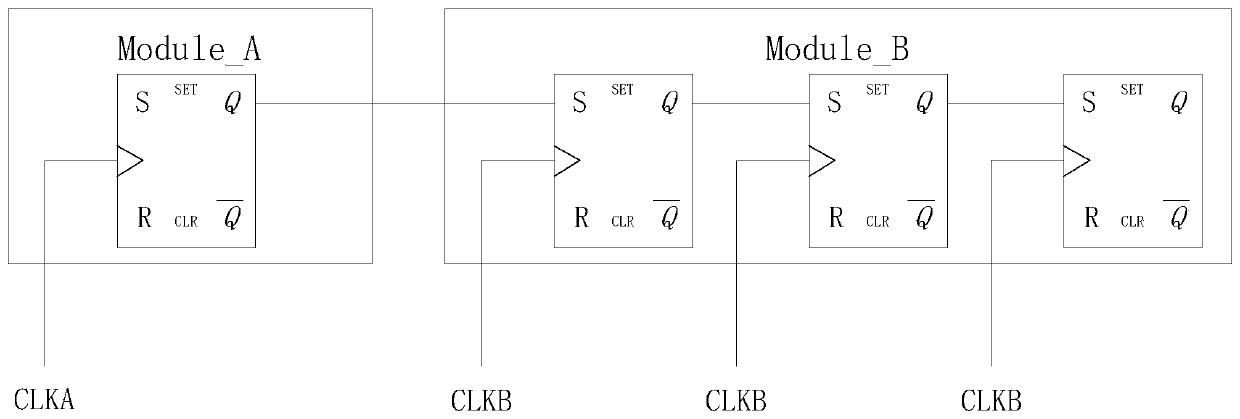

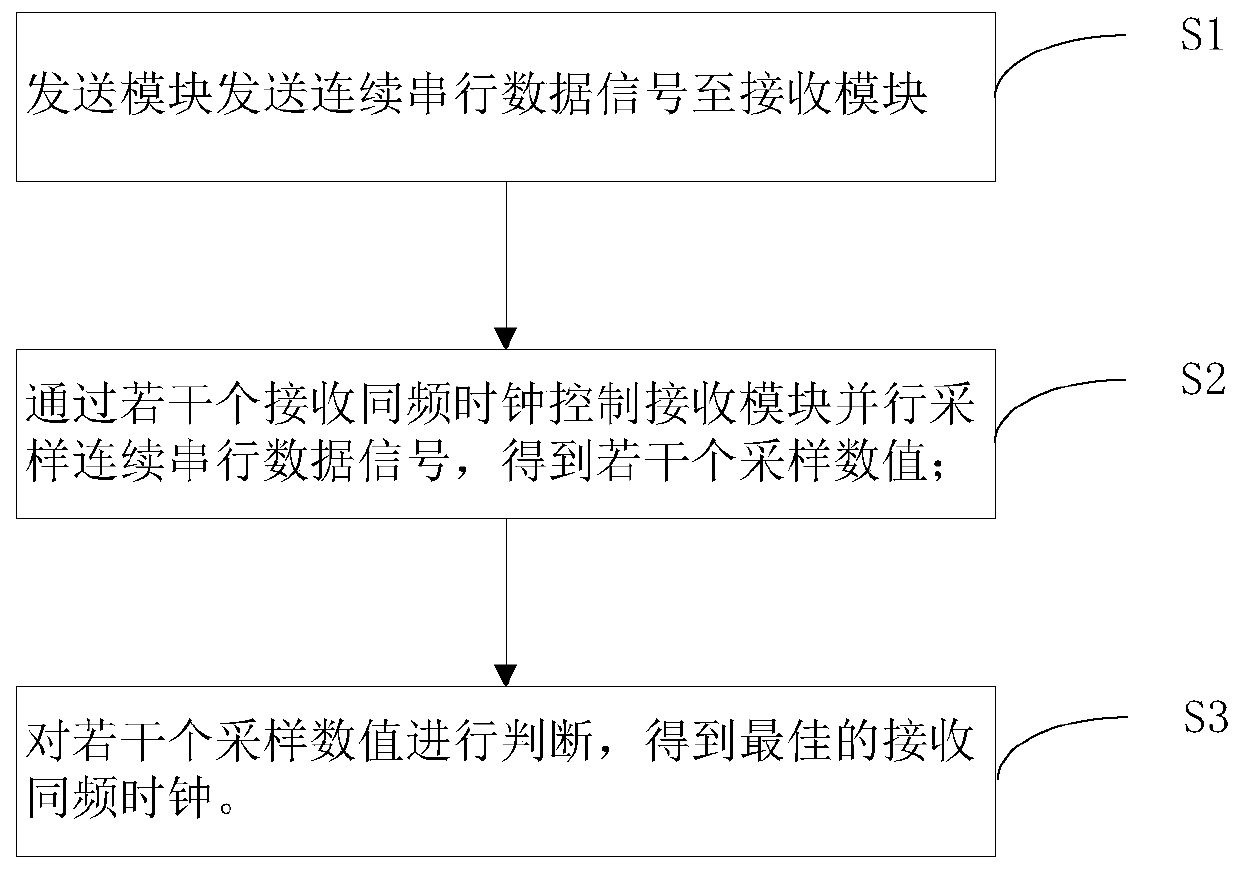

[0039] image 3 It is a schematic flow chart of a method for synchronizing continuous serial data at the same frequency in an embodiment of the present invention, refer to image 3 , a method for synchronizing continuous serial data at the same frequency, comprising the steps of:

[0040] S1, the sending module sends continuous serial data signals to the receiving module;

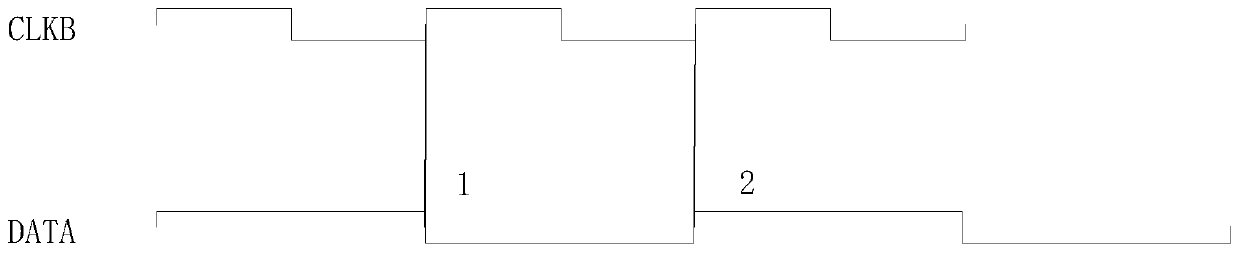

[0041] S2, controlling the receiving module to sample continuous serial data signals in parallel through several receiving clocks of the same frequency to obtain several sampling values; wherein, the phases of several receiving clocks of the same frequency are different;

[0042] S3. Judgment is made on several sampled values to obtain the best received clock with the same frequency.

[0043] In this embodiment, step S1 specificall...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com