Method and device for testing logic model in a chip

A logic model and test method technology, applied in the direction of measuring devices, measuring electricity, measuring electrical variables, etc., can solve the problems of uncoverable testing, limited number of logic resources, and limited number of boundary scan chains, etc., to improve test efficiency and fault coverage High efficiency, reduced implementation and operation and maintenance costs, simple structure and easy realization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

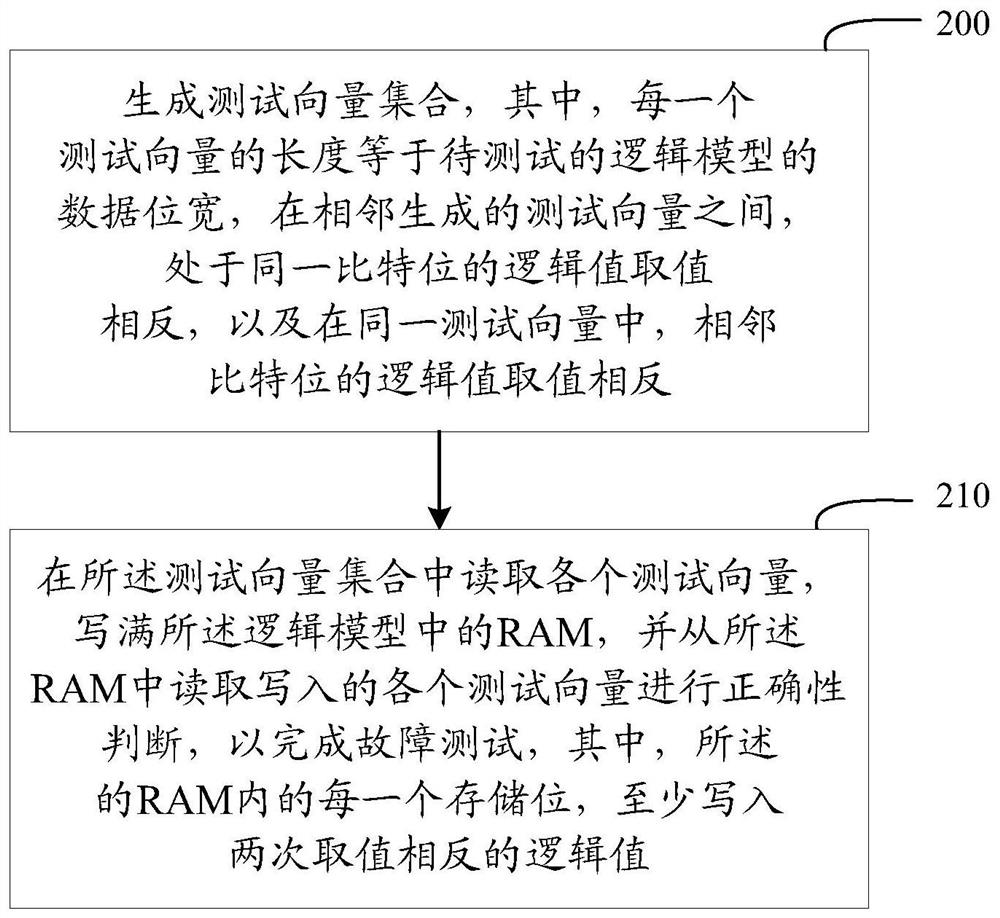

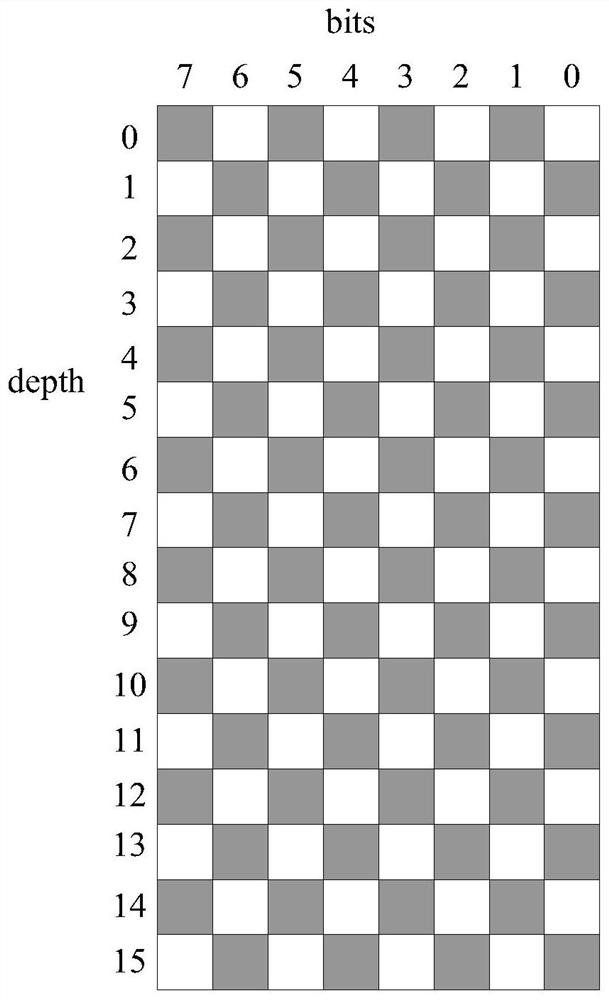

[0071] In order to improve the test efficiency and fault coverage of the logic model without occupying a large amount of logic resources, in the embodiment of the present invention, a set of test vectors is generated according to a preset checkerboard format, and is passed through the RAM in the logic model to be tested. Write and read the test vectors in the test vector set to complete the fault test of the RAM.

[0072] In this way, there is no need to download a separate test configuration file separately, and the built-in self-test for the logic model can be completed in the chip reset initialization stage, occupying less resources, and covering the main failure modes that can be generated by the logic model.

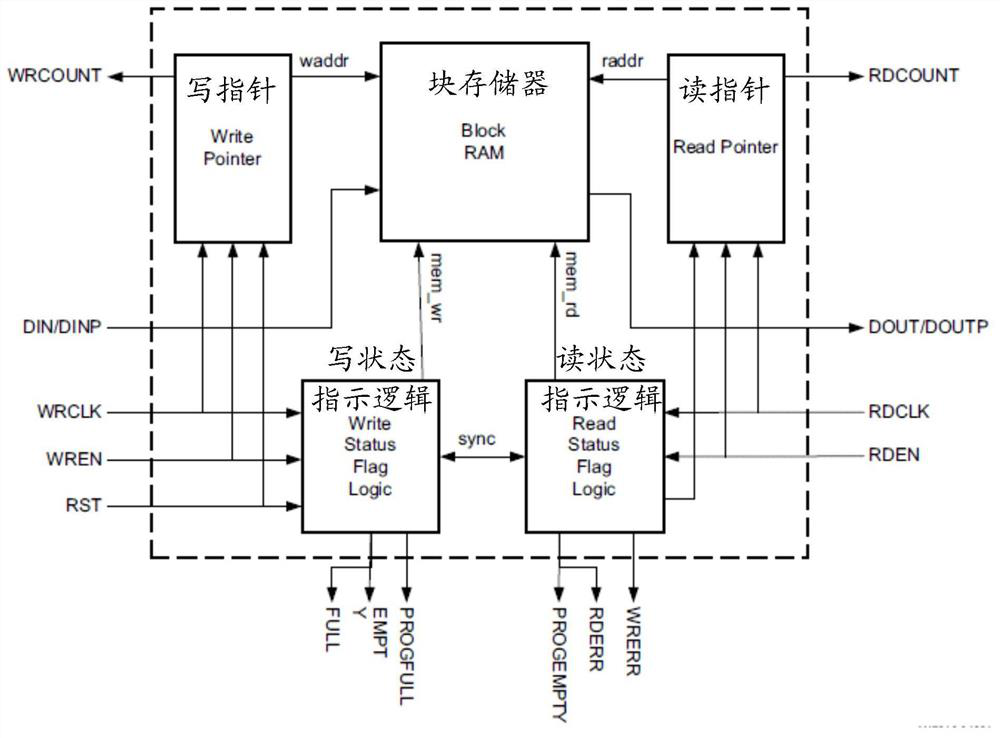

[0073] In the embodiment of the present invention, taking the logic model to be tested as an example of a FIFO model, the internal testing process of the FPGA chip is introduced in detail.

[0074] First of all, in the FIFO model, the read-write address of RAM is de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More