Integrated micro-channel heat dissipation structure, preparation method and wafer-level packaging structure

A heat-dissipating structure and micro-channel technology, applied in micro-structure devices, manufacturing micro-structure devices, micro-structure technology, etc., can solve the problem of unsatisfactory chip heat dissipation effect, achieve super-large heat-dissipation capacity, ultra-high integration, and solve heat-dissipation problems. effect of the problem

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

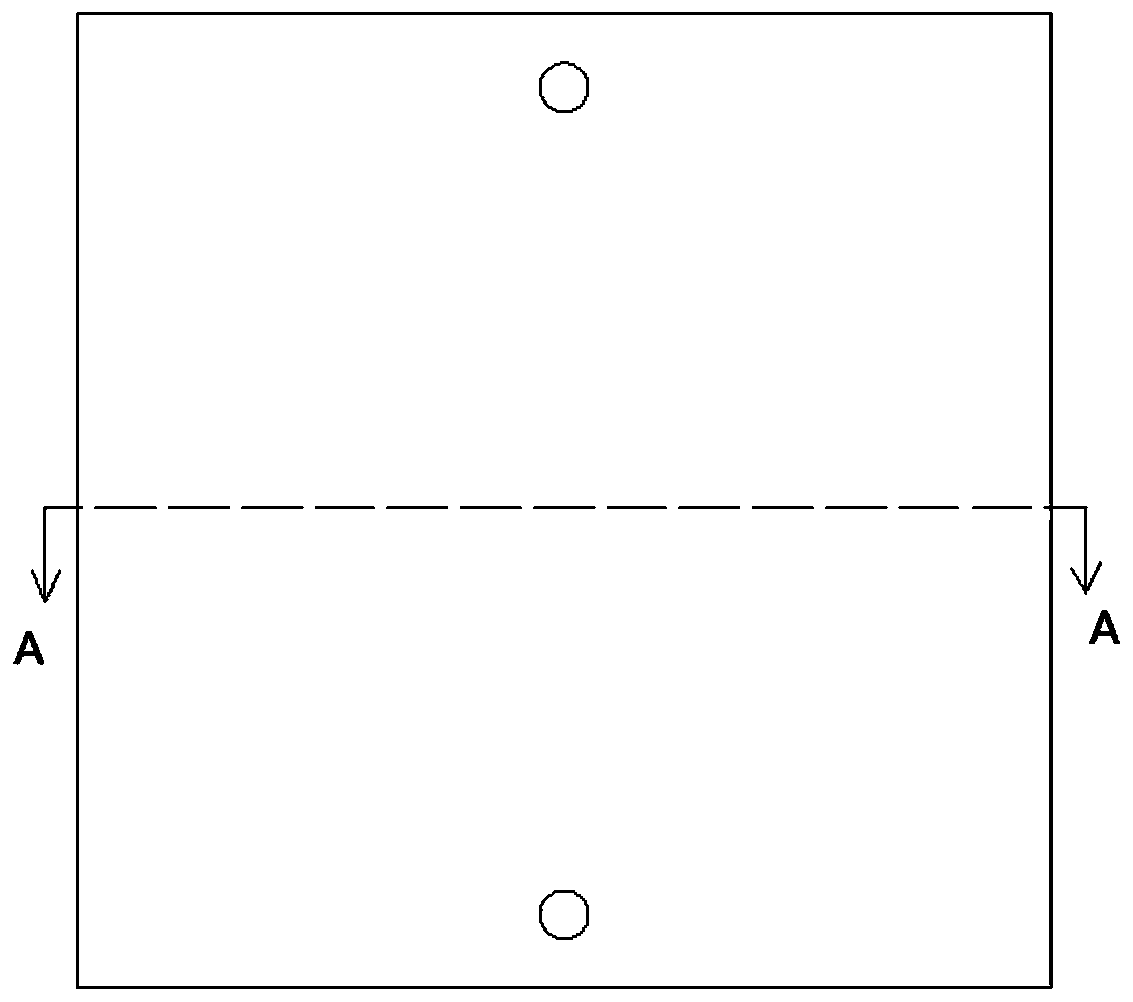

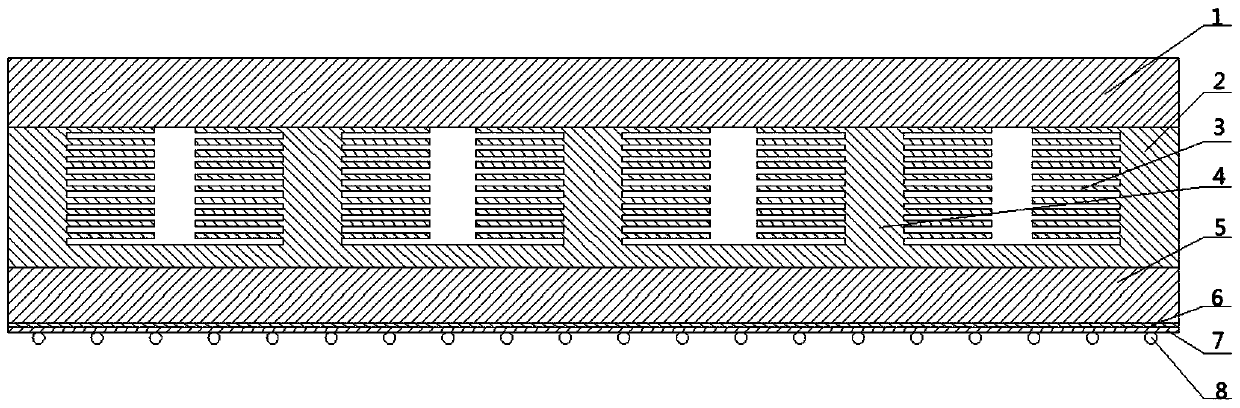

[0038] Such as figure 1 , figure 2 As shown, in this embodiment, the integrated microchannel heat dissipation structure includes a first cover plate 1, a second cover plate 2, primary fins 3, and secondary fins 4;

[0039] The first cover plate 1 and the second cover plate 2 form a housing with a cavity, and a plurality of primary fins 3 arranged in parallel at intervals are arranged in the cavity. The inner side is provided with secondary fins 4, and the secondary fins 4 are a plurality of sheet-like heat sinks arranged at intervals, and the heat dissipation surface formed is dozens of times that of the chip itself, and the top surface of the shell is provided with a liquid inlet hole for the cooling medium to enter 11 and a liquid outlet 12 through which the cooling medium flows out. The heat exchange channels are formed by the gaps between the primary fins 3 and the gaps between the secondary fins 4 .

[0040] to combine image 3 , Figure 4 , Figure 5 As shown, the...

Embodiment 2

[0044] Such as Figure 5 , Figure 6 As shown, the two sides of the inner bottom surface of the second cover plate 2 are respectively provided with a distribution groove 21 and a confluence groove 22 corresponding to the liquid inlet 11 and the liquid outlet 12, and the distribution groove 21 passes between the adjacent primary fins 3 The space between the secondary fins 4 and the space between the secondary fins 4 communicate with the flow groove 22. The distributing groove 21 can realize that the liquid is stored in the distributing groove 21 first, and then flows to the confluence groove 22 respectively through the gaps between the adjacent primary fins 3 and the gaps between the secondary fins 4, so as to realize the uniformity of the cooling medium. distribute.

[0045] The present invention also provides a method for preparing a wafer-level packaging structure with an integrated microchannel heat dissipation structure, comprising the following steps:

[0046] SO1: Pre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com