V-BY-ONE signal conversion method, V-BY-ONE signal conversion device and electronic equipment

A V-BY-ONE, signal conversion device technology, applied in the field of signal processing, can solve the problems of increasing the difficulty of PCB design, low integration, poor versatility, etc., to enhance the anti-interference ability of clocks and signals, and improve signal output. quality, the effect of increasing system stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

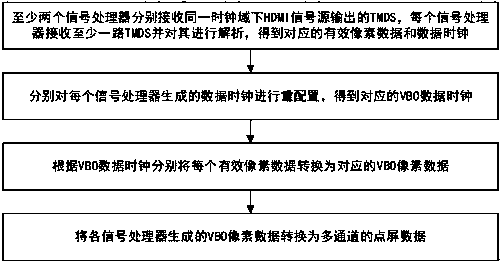

[0055] figure 1 It is a flowchart of a V-BY-ONE signal conversion method provided in this embodiment, see figure 1 , the method includes the following steps:

[0056] S1: At least two signal processors respectively receive the minimum transmission differential signal output by the HDMI signal source in the same clock domain through the HDMI interface, and each signal processor receives at least one minimum transmission differential signal and analyzes it to obtain the corresponding valid pixel data and data clock;

[0057] The HDMI interface uses Transition Minimized Differential Signaling (TMDS), including 4 channels, of which 3 channels are used to transmit TMDS data, and one channel is used to transmit TMDS clock; in addition, the built-in I2C interface of the HDMI interface performs Command transmission; therefore, one HDMI interface transmission minimizes the transmission of differential signals including TMDS data, TMDS clock and I2C commands.

[0058] After receiving...

Embodiment 2

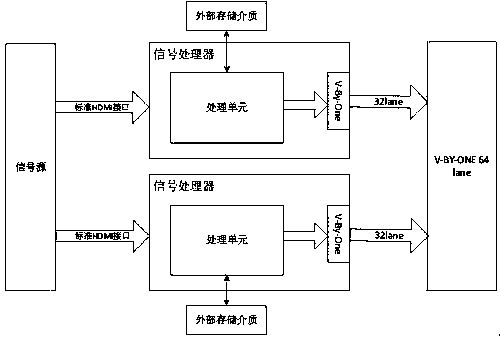

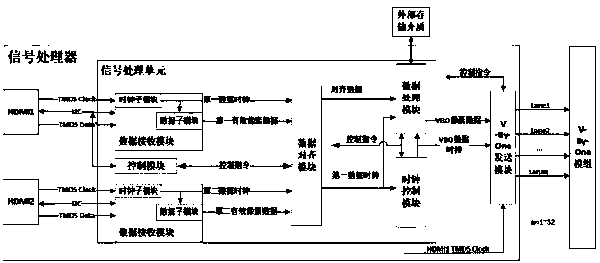

[0074] This embodiment provides a device for realizing the above V-BY-ONE signal conversion method, figure 2 It is a schematic diagram of the composition and structure of the V-BY-ONE signal conversion device provided in this embodiment, image 3 It is a logical block diagram of the signal processor in the V-BY-ONE signal conversion device provided by this embodiment; see figure 2 , 3 As shown, the device includes two signal processors with HDMI interfaces; wherein, the HDMI interfaces of the two signal processors are used to receive the minimum transmission differential signal output by the HDMI signal source in the same clock domain; the signal processor can use a dedicated Integrated circuits or FPGAs, which are not specifically limited in this embodiment;

[0075] Each signal processor includes at least one processing unit and at least one storage unit, and the storage unit stores a computer program that can run on the processing unit. When the computer program is exec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com