SSD stacked packaging structure and preparation method thereof

A packaging structure and mounting technology, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve problems such as the large volume of SSD stacking packages, achieve low cost, reduce pressure, and prevent splitting Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

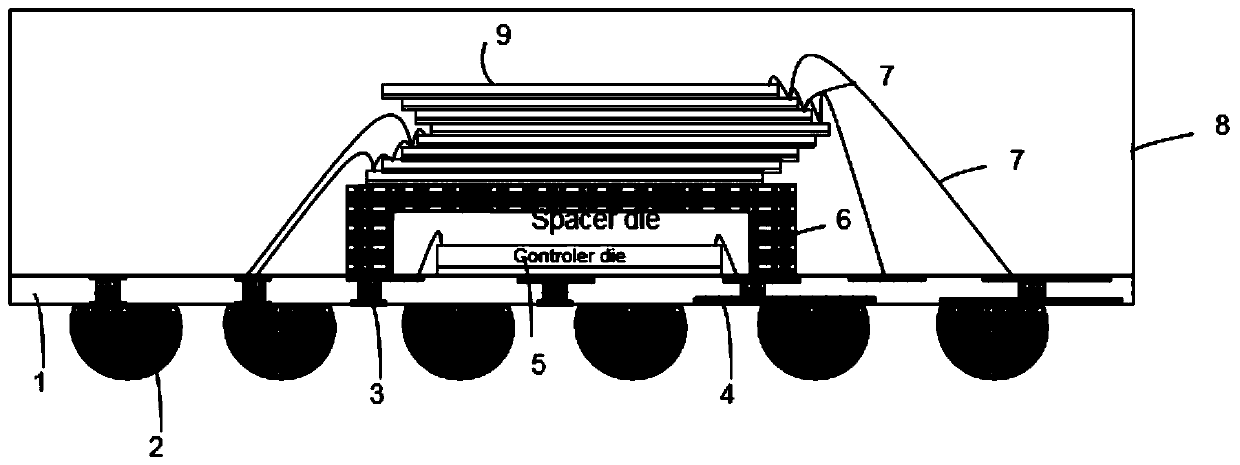

[0047] The method for preparing the above-mentioned SSD stack package structure includes the following steps:

[0048] An accommodating space is formed on the lower surface of the spacer 6;

[0049] Mounting a control chip 5 on the substrate 1 to electrically connect the control chip 5 to the substrate 1;

[0050] Mount the spacer 6 with the accommodation space on the substrate 1, and place the control chip 5 in the accommodation space;

[0051] Mounting the memory chip 9 on the upper surface of the spacer 6;

[0052] The spacer 6 is mounted on the substrate 1, and the control chip 5 is placed in the accommodating space; the circuit connection is realized by wire bonding;

[0053] Finally, the plastic package 8 wraps the substrate 1 , the spacer 6 , the memory chip 9 and the bonding wire 7 for plastic packaging.

[0054] The spacer 6 is etched and grooved to form an accommodating space of a U-shaped groove structure.

Embodiment

[0056] Figure 2 to Figure 4 It is the packaging structure manufacturing method of some embodiments of the present invention, and the specific manufacturing method is as follows:

[0057] figure 2 It is a schematic diagram of forming a U-shaped groove by etching and grooving, and then cutting to form a separate spacer. The material of the spacer is not limited, such as silicon material, and mainly plays a supporting role; when the spacer 6 is made of metal, the number of control chips 5 can be reduced. electromagnetic interference, and at the same time strengthen the heat dissipation of the upper stacked memory chips 9 .

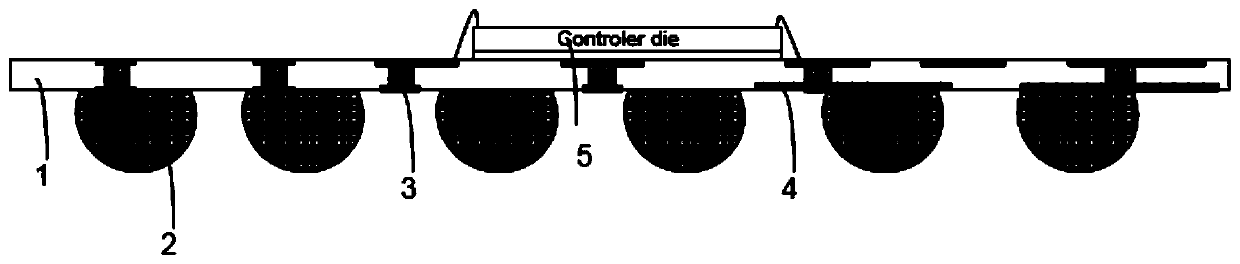

[0058] image 3 It is to provide a core on the substrate 1; mount the control chip 5 on the substrate 1;

[0059] Figure 4 exist image 3 On the basis of the secondary core (upper spacer); the spacer 6 is mounted on the substrate 1, and the control chip 5 is placed in the accommodating space;

[0060] Figure 5 is in Figure 4On the basis of adding...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com