Array substrate, manufacturing method and display panel

A technology of an array substrate and a manufacturing method, which are applied in the fields of an array substrate, a manufacturing method and a display panel, can solve the problems of inability to monitor the etching U% of an insulating layer, difficulty in process optimization, increase in cost, etc., so as to improve the process yield and save money. Power consumption, the effect of saving production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

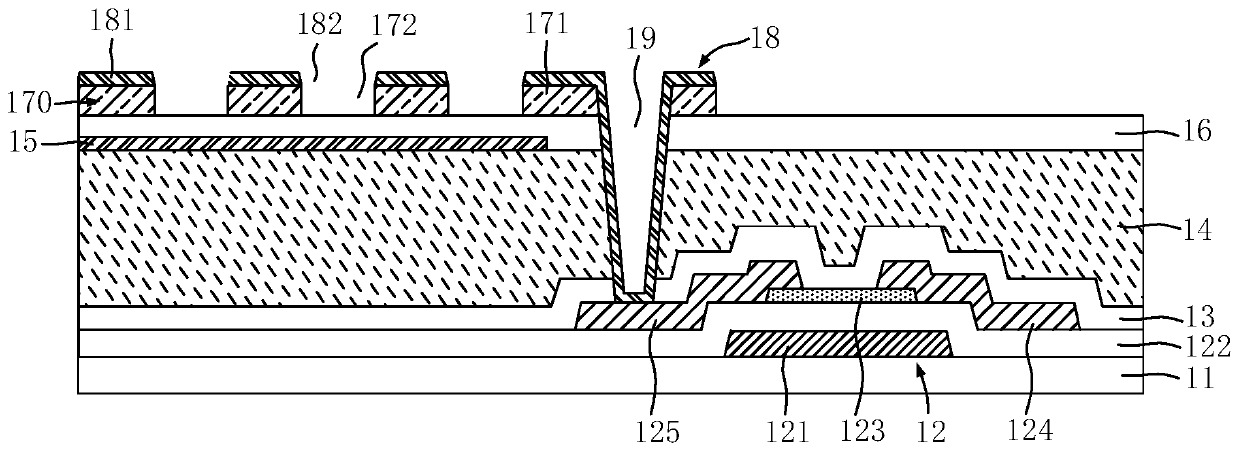

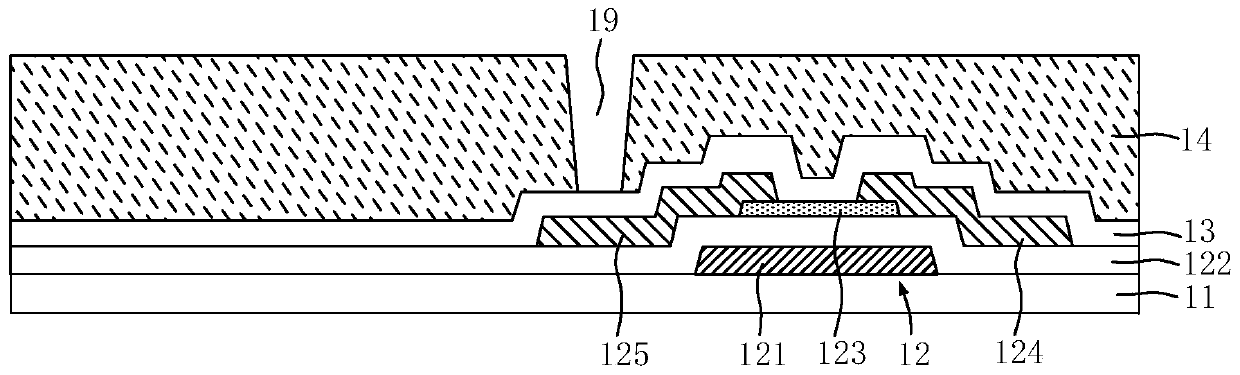

[0062] Figure 2a to Figure 2k It is a schematic diagram of the manufacturing process of the array substrate in the first embodiment of the present invention, which is used to manufacture the above-mentioned array substrate, such as Figure 2a to Figure 2k As shown, the manufacturing method includes: forming a plurality of TFTs 12 arranged in an array on the substrate 11 , each TFT 12 including a gate 121 , a gate insulating layer 122 , an active layer 123 , a source 124 and a drain 125 . Specifically, a first metal layer (not shown) is deposited on the substrate 11, and the first metal layer is patterned to form a scan line (not shown) and a gate 121; the gate is deposited on the substrate 11 The insulating layer 122, the gate insulating layer 122 covers the scan line and the gate 121; the active layer film is deposited on the gate insulating layer 122, and the active layer film is patterned to form the active layer 123, the active layer 123 It can be amorphous silicon (a-Si...

no. 2 example

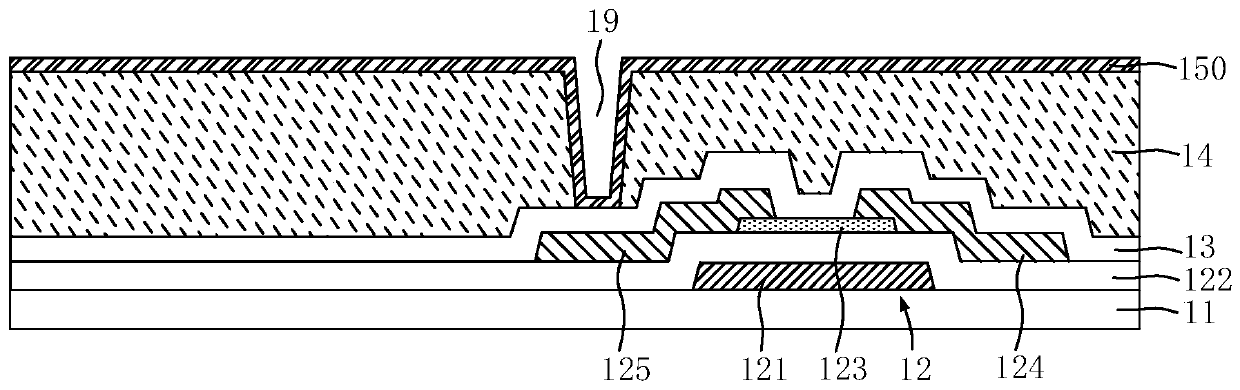

[0070] Figure 3a to Figure 3k It is a schematic diagram of the manufacturing process of the array substrate in the second embodiment of the present invention. The implementation of this embodiment is basically the same as that of the first embodiment, and the similarities will not be repeated here. The differences include:

[0071] forming a second insulating layer 16 covering the common electrode 15, and the second insulating layer 16 also covers the exposed planar layer 14 and the first insulating layer 13;

[0072] using a dry etching process to remove the second insulating layer 16 at the position of each contact hole 19, so as to expose the lower first insulating layer 13 at the position of each contact hole 19;

[0073] Form the third insulating layer 17 covering the second insulating layer 16, and the third insulating layer 17 also covers the exposed first insulating layer 13 at the same time, wherein the second insulating layer 16 adopts a material that can be dry etc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com