Semiconductor memory

A memory and semiconductor technology, applied in semiconductor devices, electric solid state devices, transistors, etc., to avoid short circuits between bit line contacts and side erosion problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

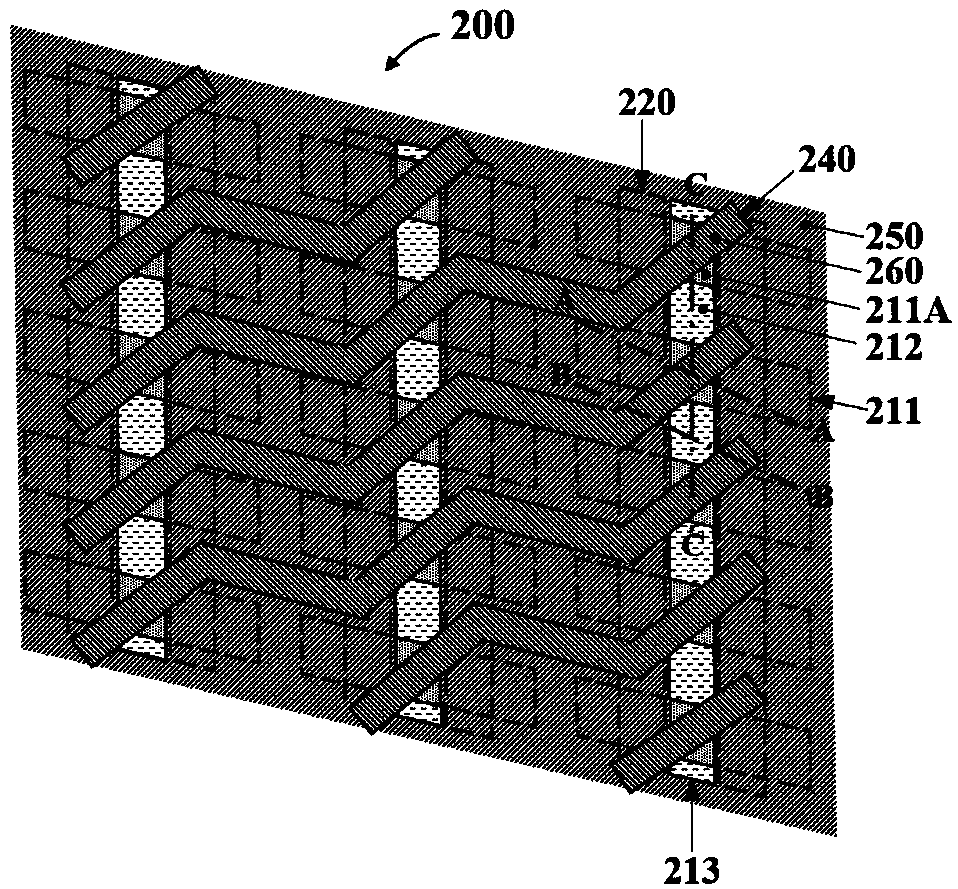

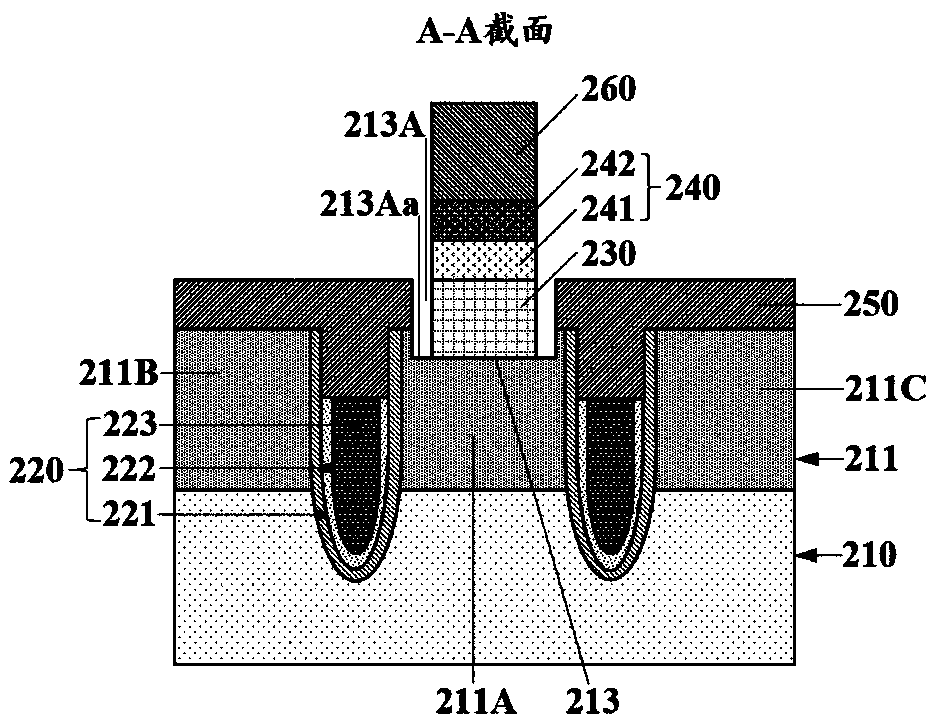

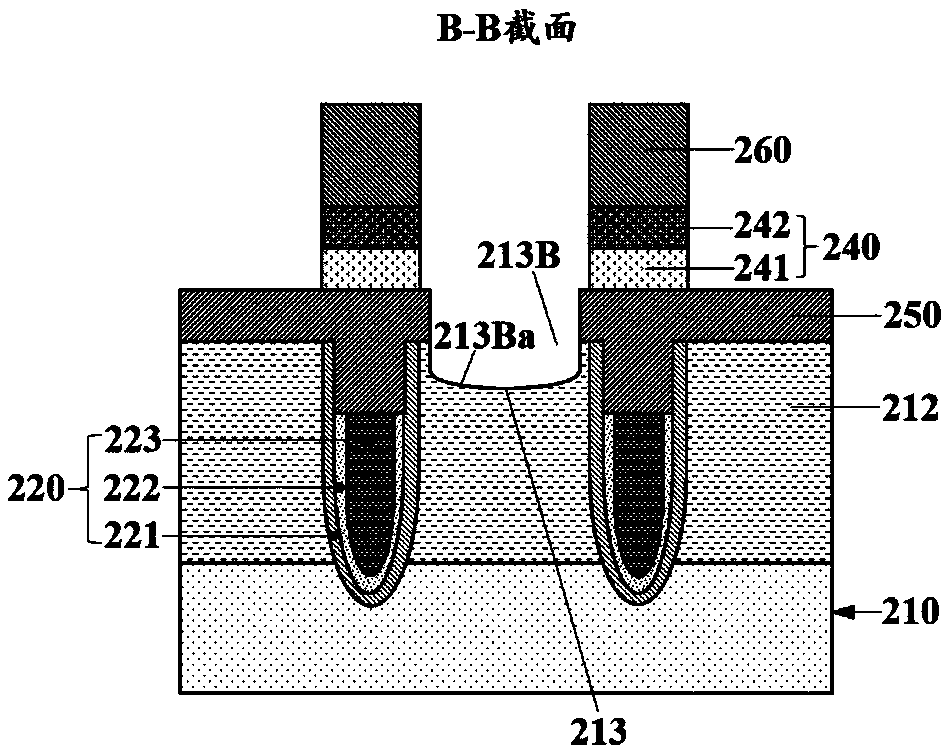

[0121] The present invention provides a semiconductor memory structure, including: a substrate 210, a word line 220, a bit line contact 230, a bit line 240, a protective layer 250 and a first barrier layer 260, such as Figures 1a-1d shown.

[0122] Wherein, the upper surface of the substrate 210 defines a plurality of active regions 211, and the active regions 211 are arranged at intervals to form an active region array, and the active regions 211 are formed on the surface of the substrate 210 and do not penetrate the substrate 210, such as Figure 1a , 1b shown. In one embodiment, the material of the active region 211 includes doped Si.

[0123] An isolation structure 212 is disposed between the active regions 211, and the isolation structure 212 is formed in the substrate 210 and insulates the active regions 211 from each other, such as Figure 1a , 1c . In one embodiment, the isolation structure 212 may be shallow trench isolation (Shallow Trench Isolation, STI), and th...

Embodiment approach 2

[0136] Another embodiment of the present invention selects different etchant gases in order to further reduce SiO 2 The etch selectivity ratio of / Si and the re-recess depth of the inter-window groove 213B.

[0137] A semiconductor memory structure, comprising: a substrate 210, a word line 220, a bit line contact 330, a bit line 240, a protection layer 250 and a first barrier layer 260, such as Figures 4a-4d shown.

[0138] Wherein, the upper surface of the substrate 210 defines a plurality of active regions 311, the active regions 311 are arranged at intervals to form an active region array, the active regions 311 are formed on the surface of the substrate 210 and do not penetrate the substrate 210, as Figure 4a , 4b shown. In one embodiment, the material of the active region 311 includes doped Si.

[0139] An isolation structure 312 is disposed between the active regions 311, and the isolation structure 312 is formed in the substrate 210 and insulates the active region...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More