Patents

Literature

46results about How to "Prevent side erosion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

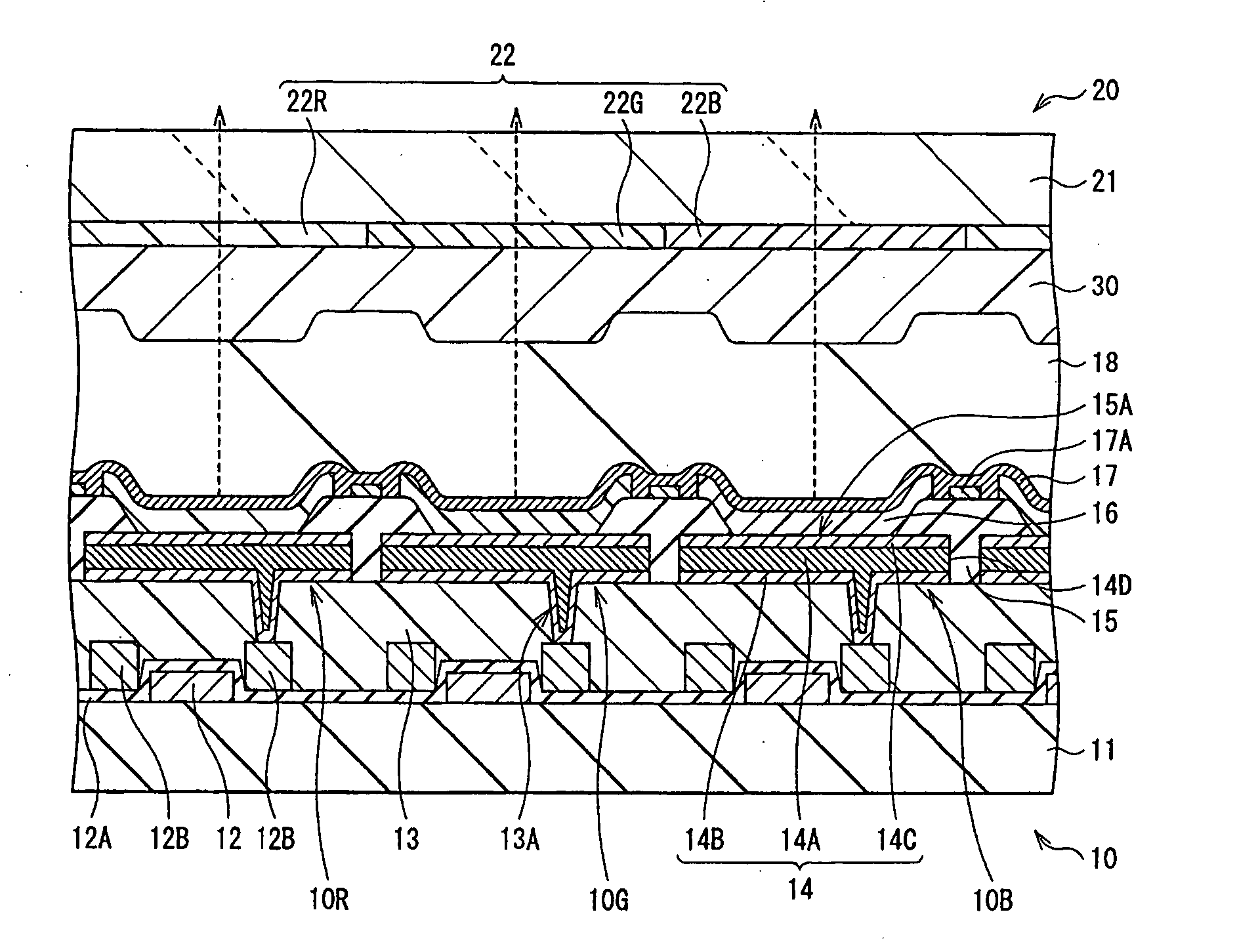

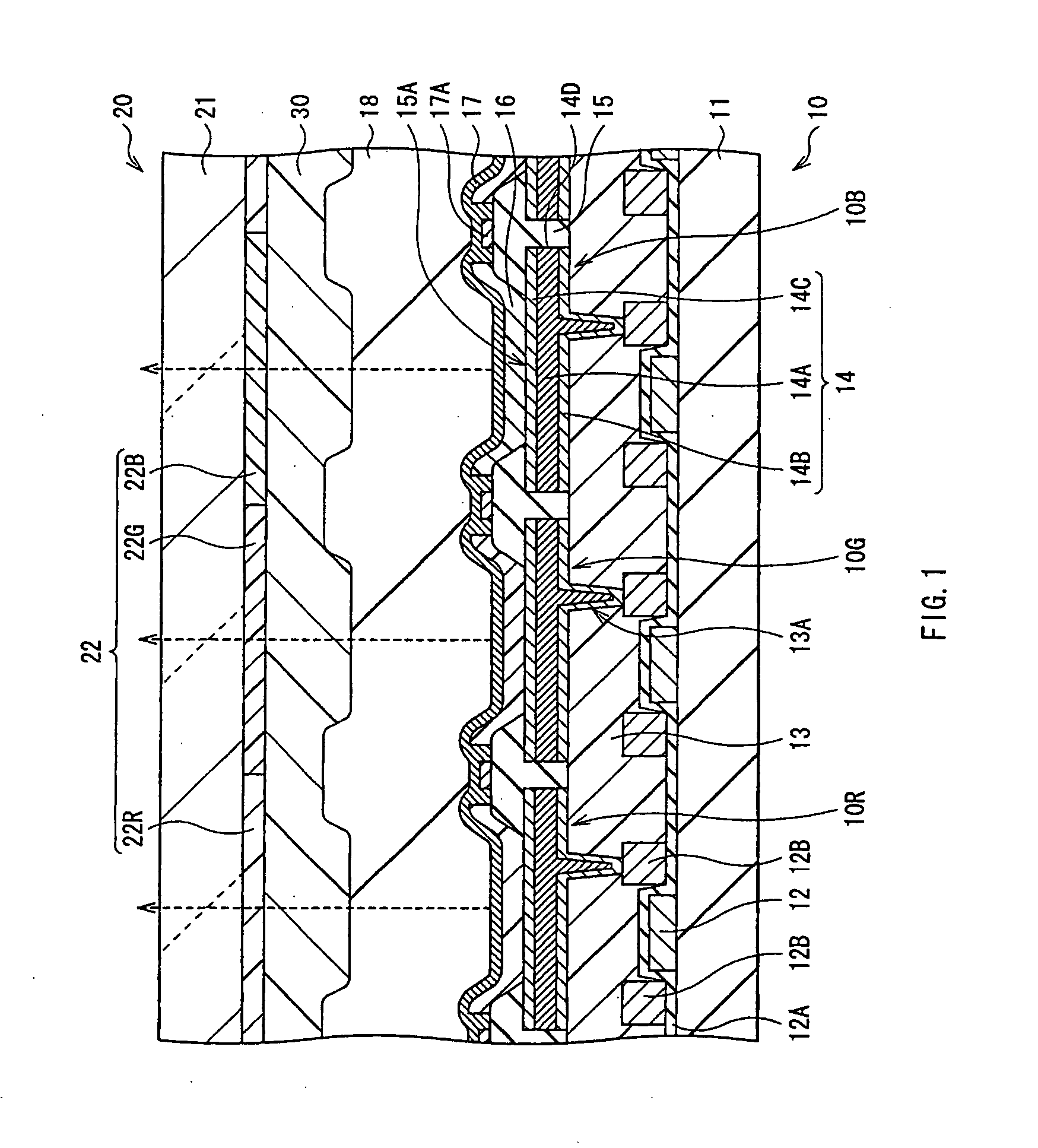

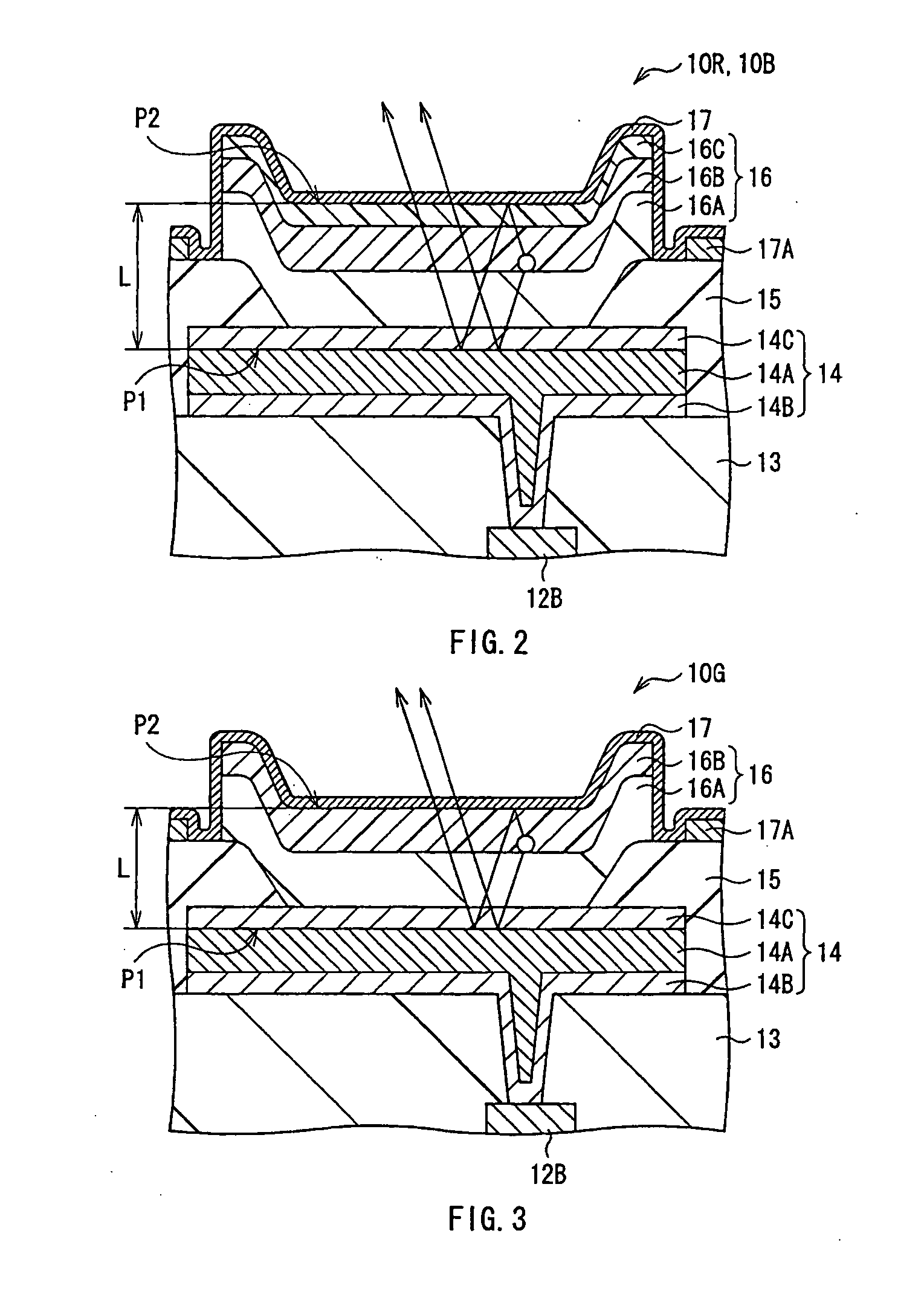

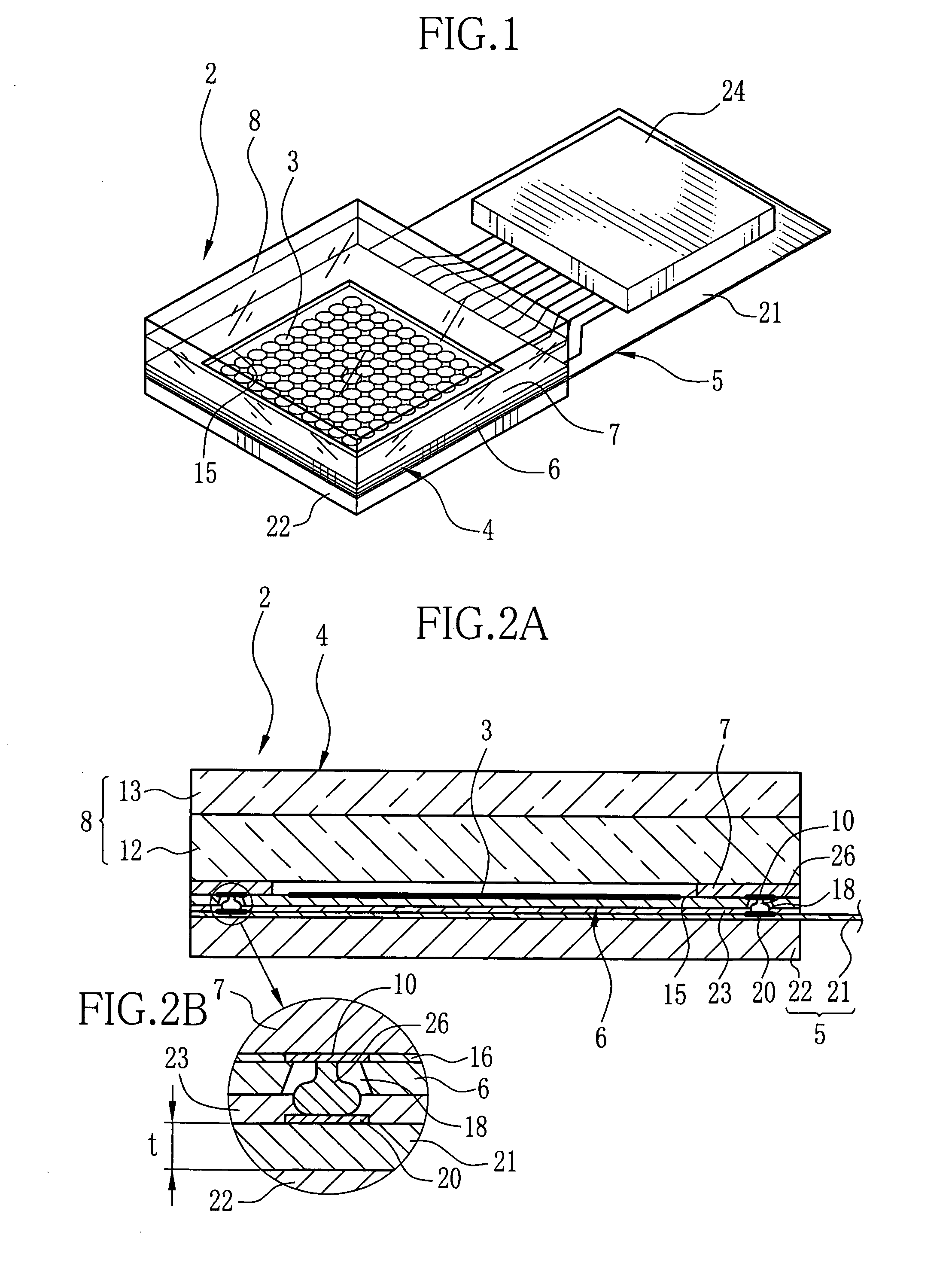

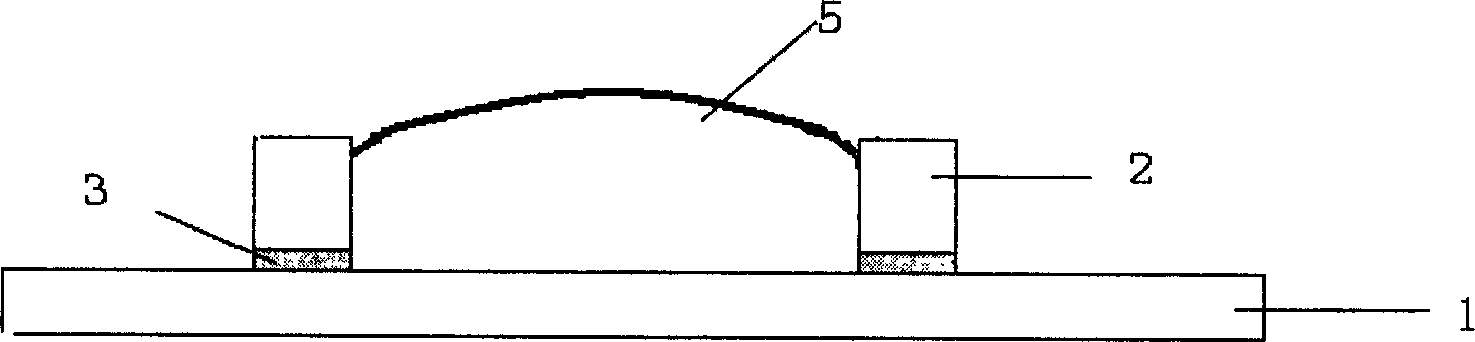

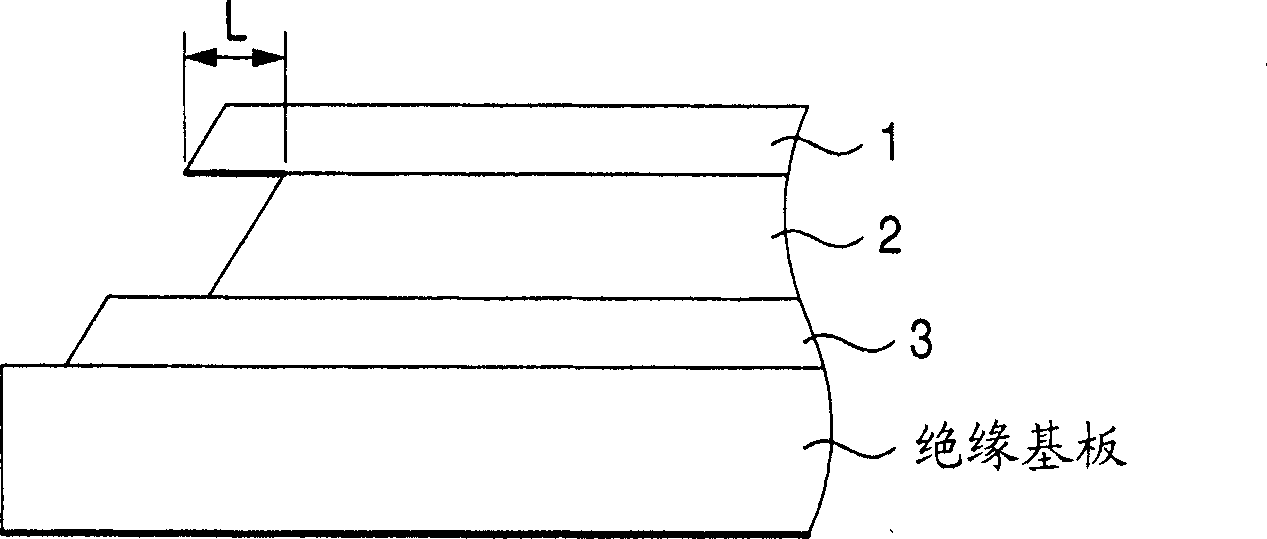

Method of manufacturing laminated structure, laminated structure, display device and display unit

InactiveUS20050007015A1Good body shapeReduce defectsDischarge tube luminescnet screensSemiconductor/solid-state device detailsEtchingLiquid-crystal display

A method of manufacturing a laminated structure capable of being patterned into a favorable shape by preventing side etching is provided. After an adhesive layer made of ITO or the like, a reflective layer made of silver or an alloy including silver, and a barrier layer made of ITO or the like are laminated in order on a substrate with a planarizing layer which is a base layer in between, a mask is formed on the barrier layer, and the adhesive layer, the reflective layer and the barrier layer are etched at once by using the mask to form a laminated structure. As an etching gas, for example, a gas including methane (CH4) is preferable. The laminated structure is used as an anode, and an insulating film, an organic layer including a light-emitting layer and a common electrode as a cathode are laminated in order on the laminated structure so as to form an organic light-emitting device. The laminated structure can be used as a reflective electrode, a reflective film or wiring of a liquid crystal display.

Owner:SONY CORP

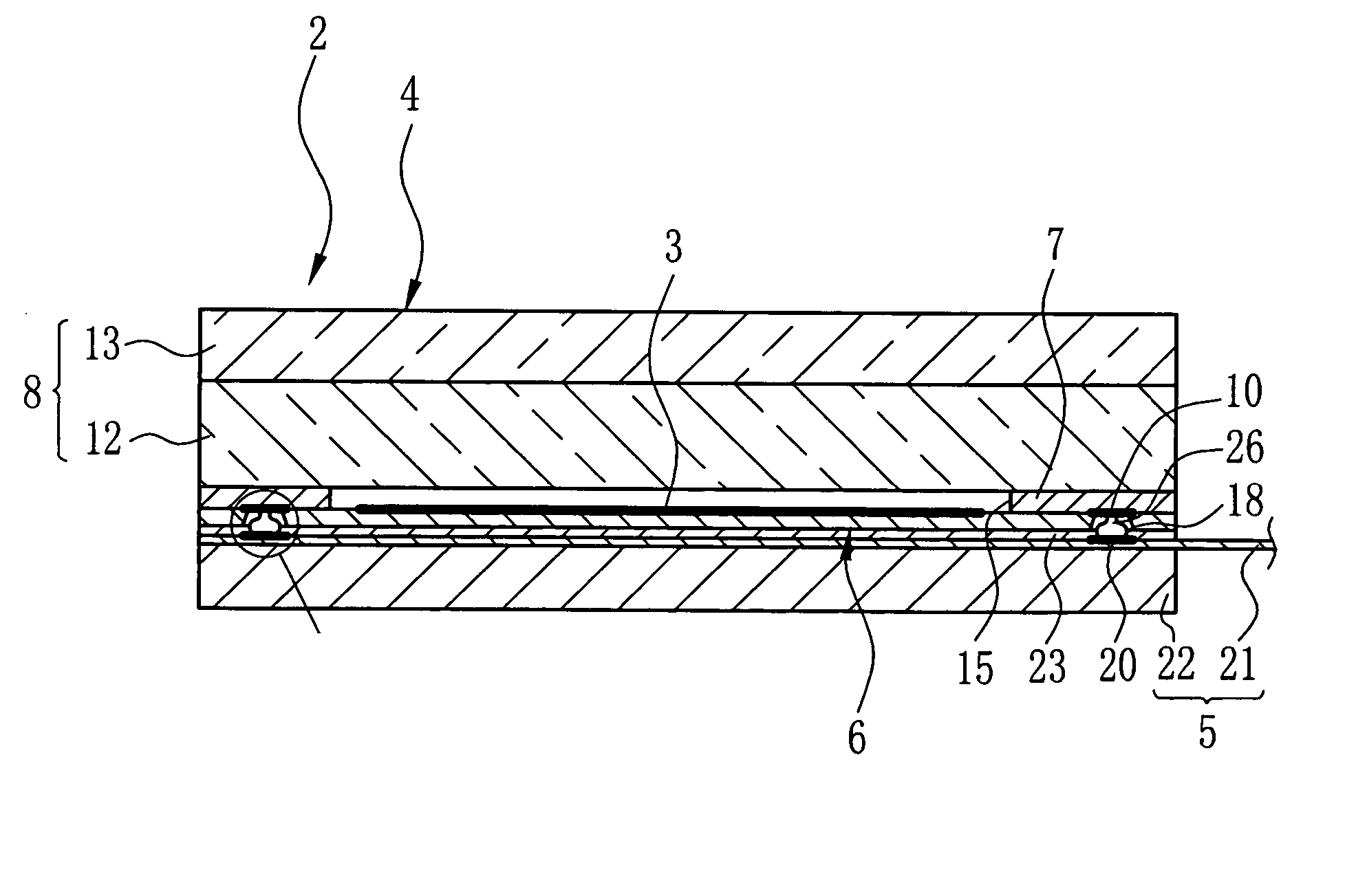

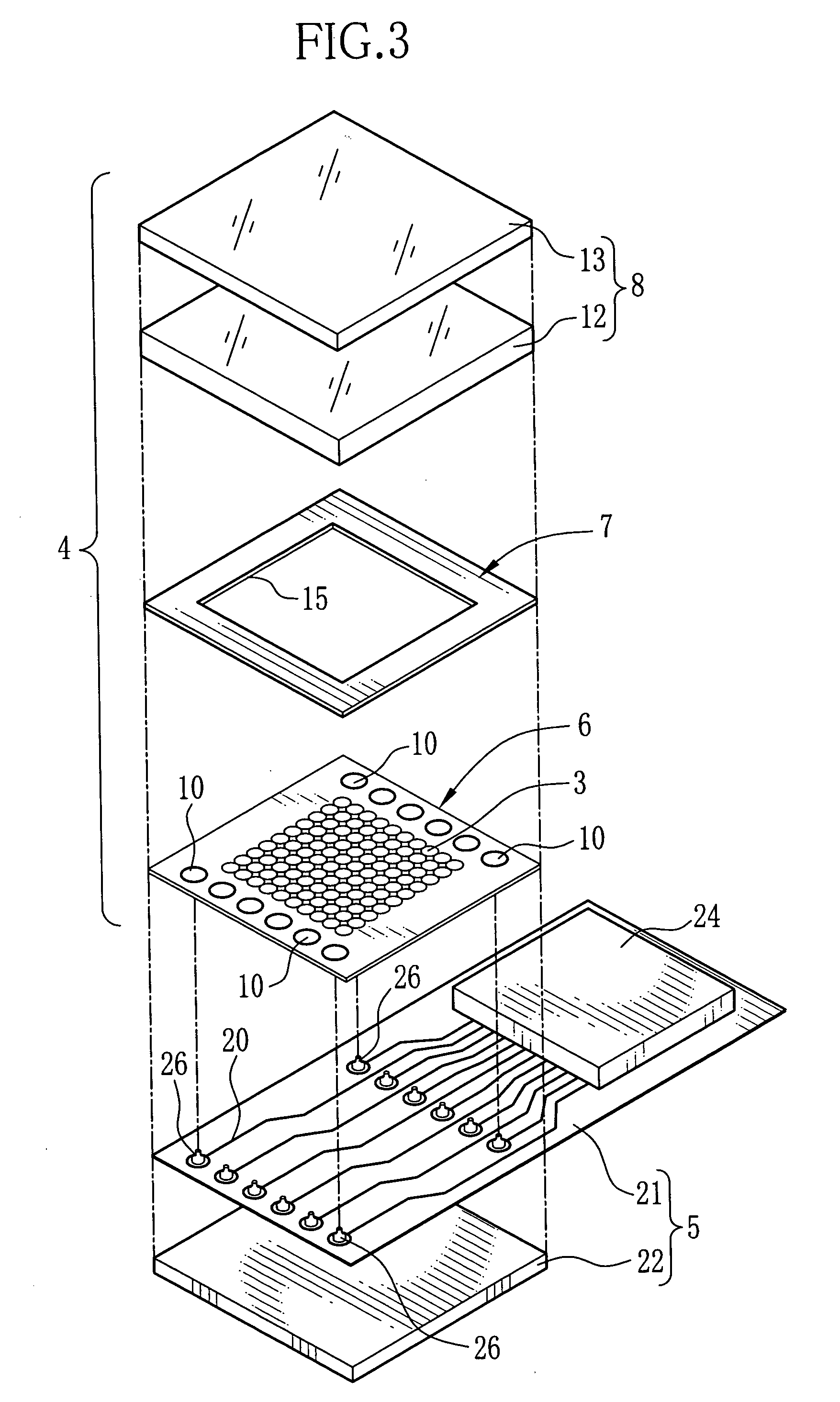

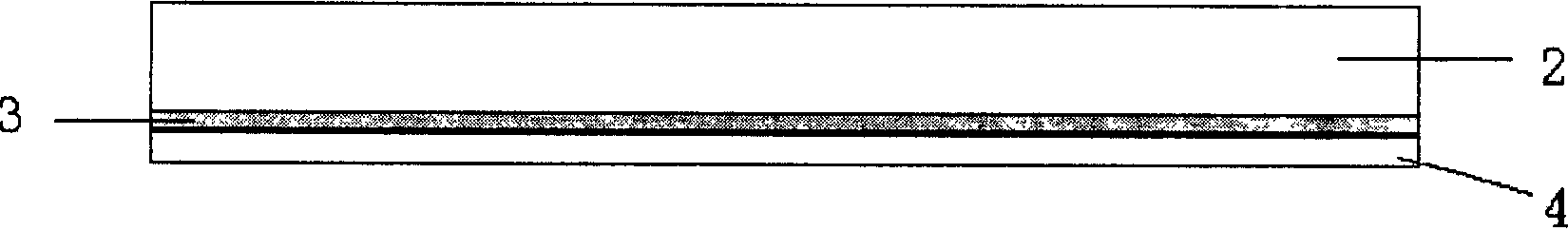

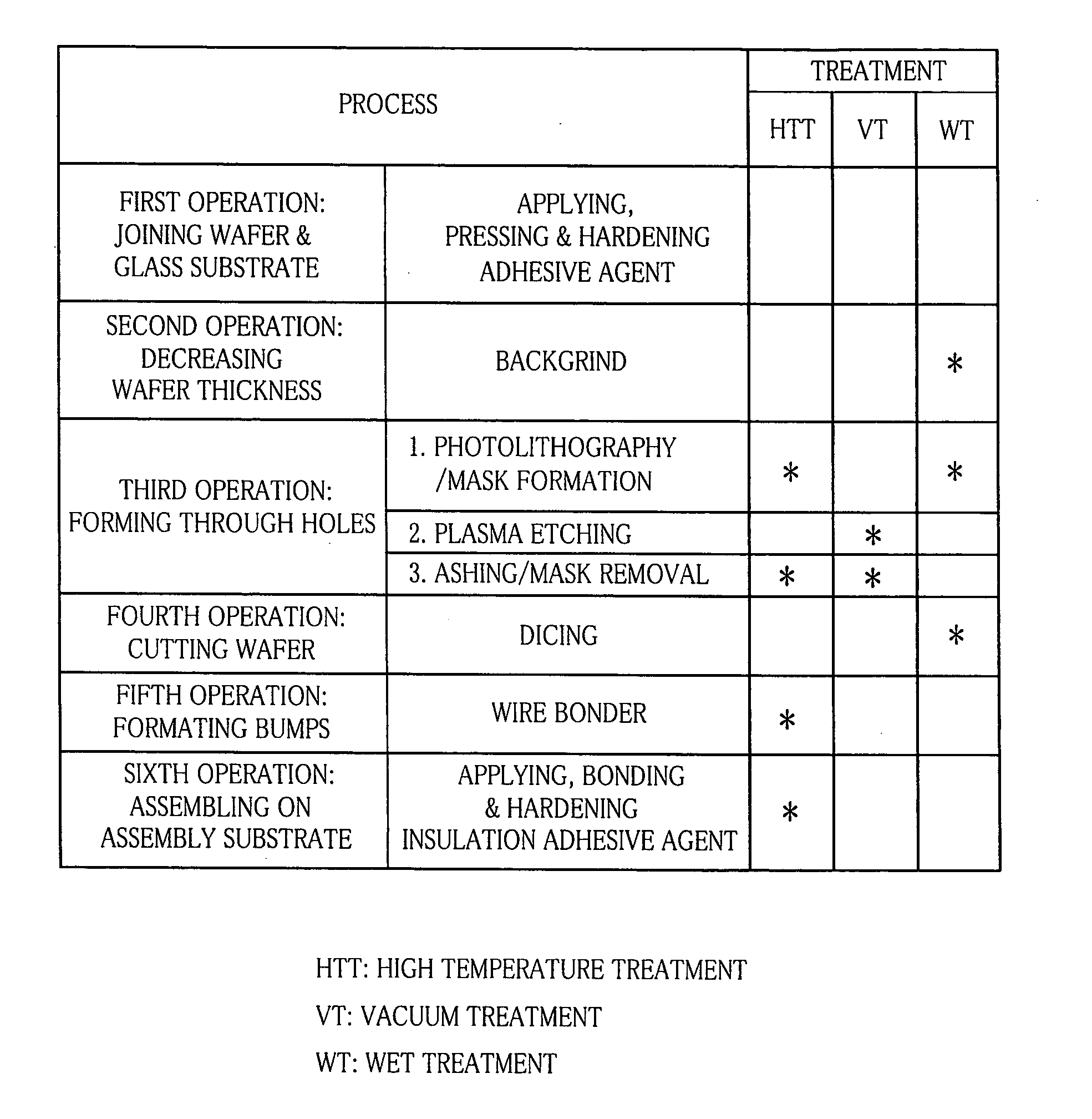

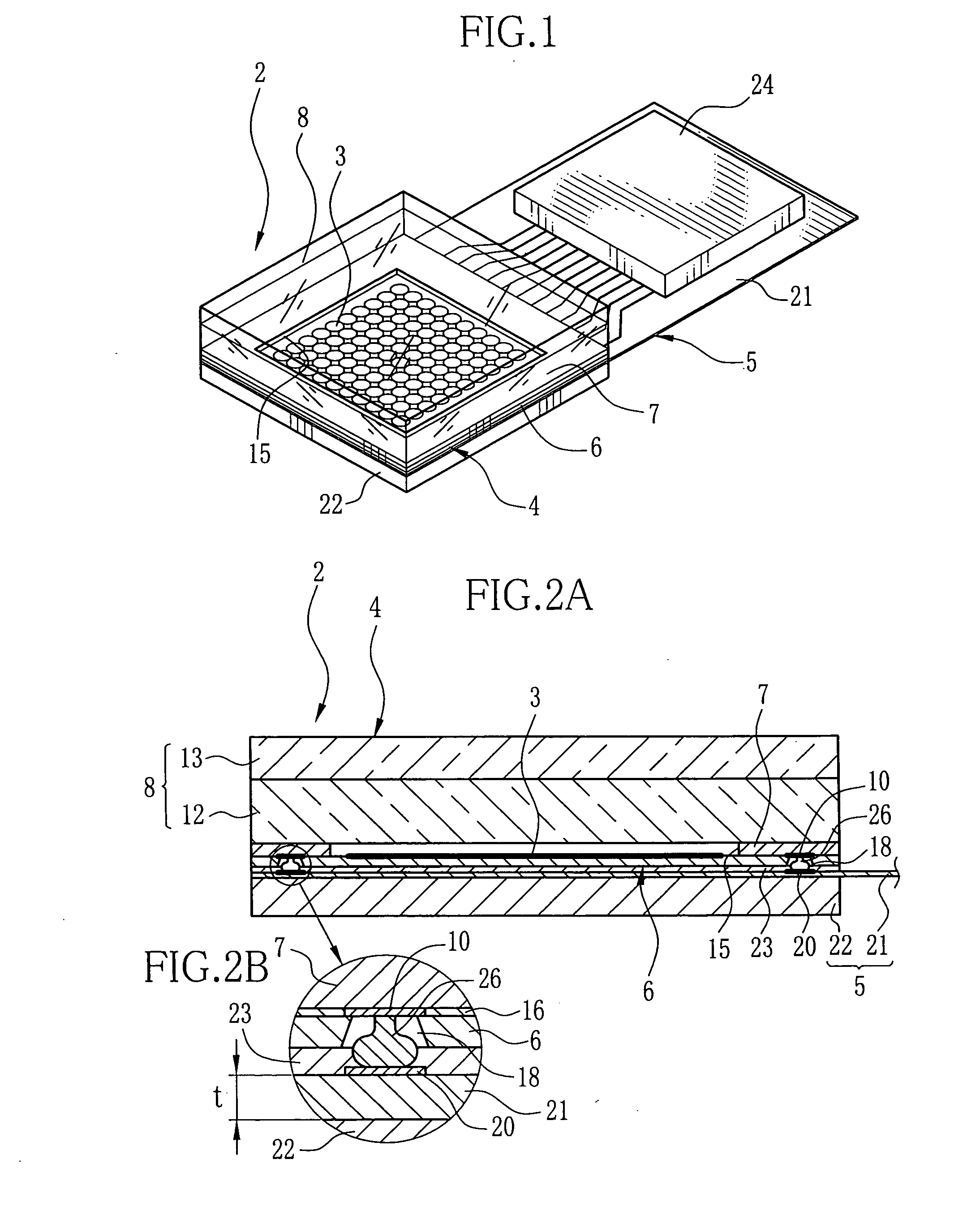

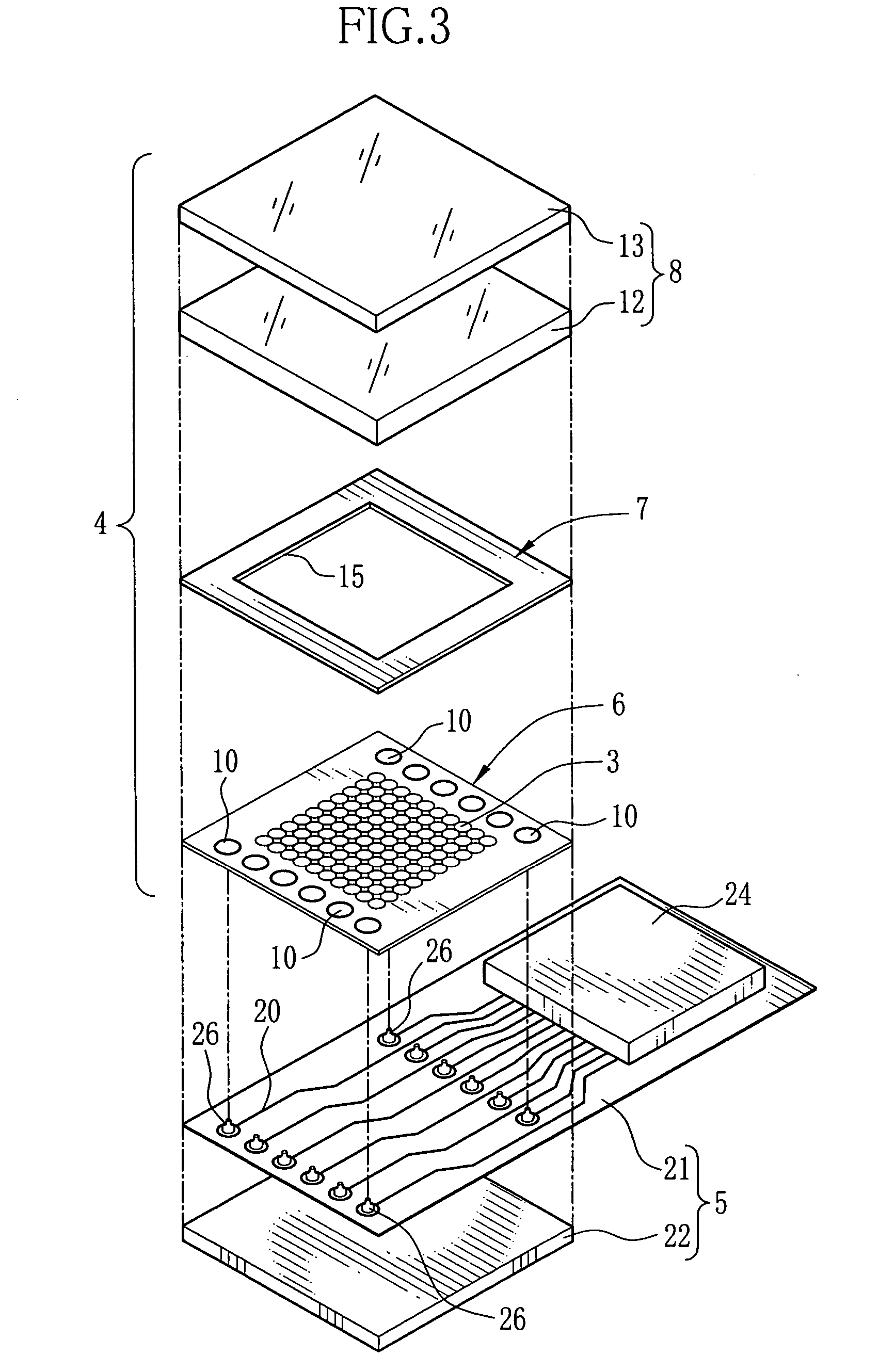

Solid state imaging device and producing method thereof

InactiveUS20050110107A1Low costReduce in quantitySemiconductor/solid-state device detailsSolid-state devicesEngineeringInterconnection

A semiconductor substrate of a solid state imaging device is connected to a cover glass, and then a backgrind is performed so as to make the thickness smaller. On a first face of the semiconductor substrate is formed plural units which is constructed of image sensors and plural contact terminals. At positions of the contact terminals, plural through-holes are formed on the bottom side of the semiconductor substrate, and the contact terminals appear on a second surface of the semiconductor substrate. On an interconnection circuit pattern of the assembly substrate are formed stud bumps. When the semiconductor substrate is assembled onto the assembly substrate, the stud bumps enter into the through-holes to contact to the contact terminals. Thus the interconnection circuit pattern is electrically connected to the image sensors.

Owner:FUJIFILM HLDG CORP +1

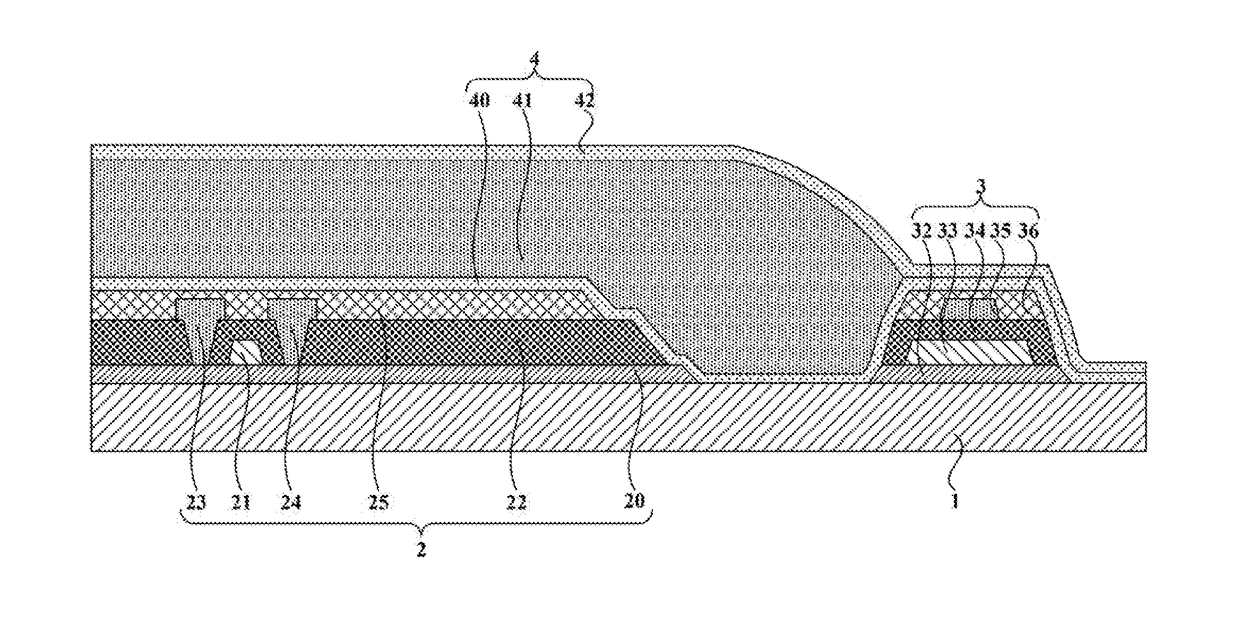

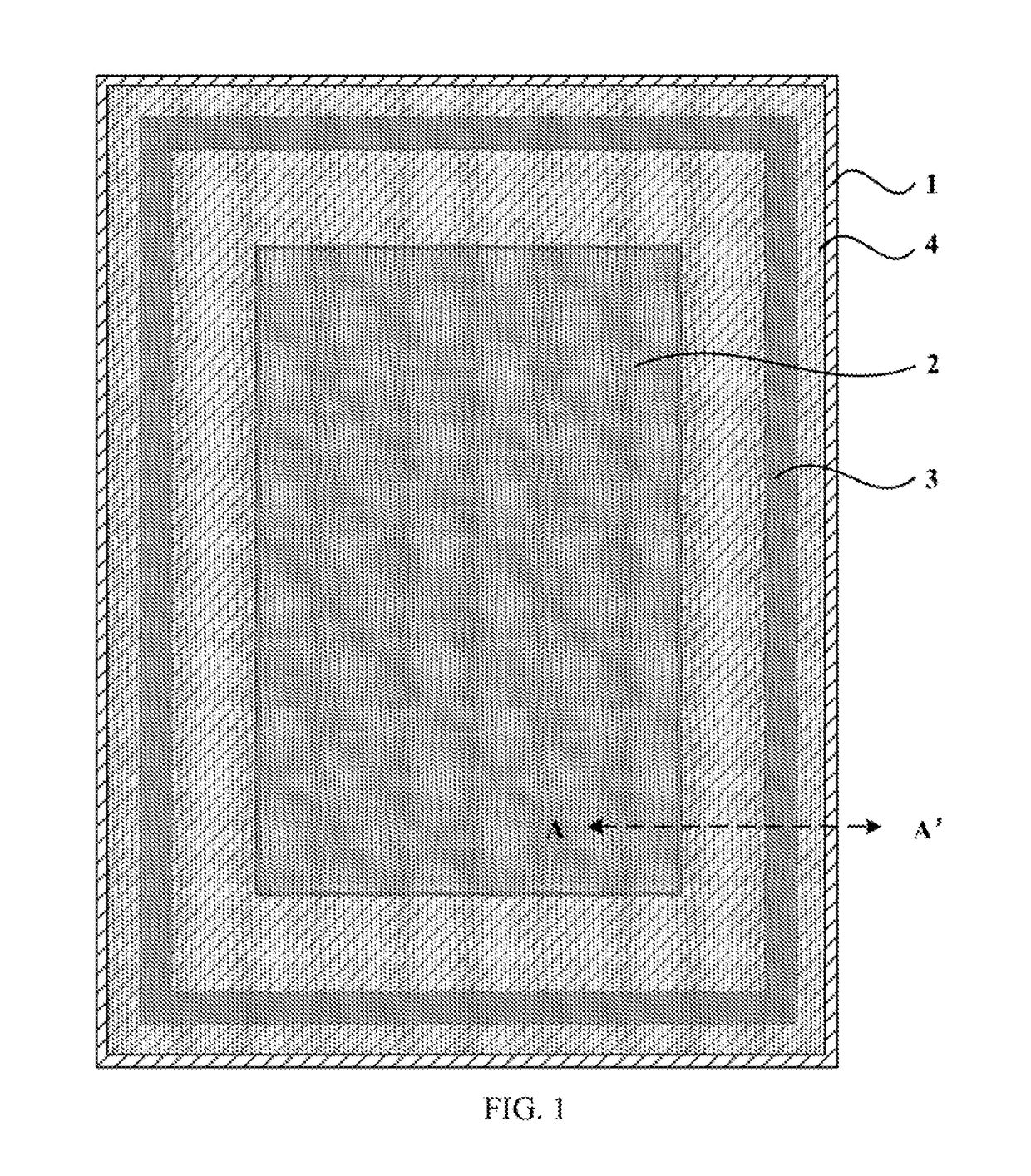

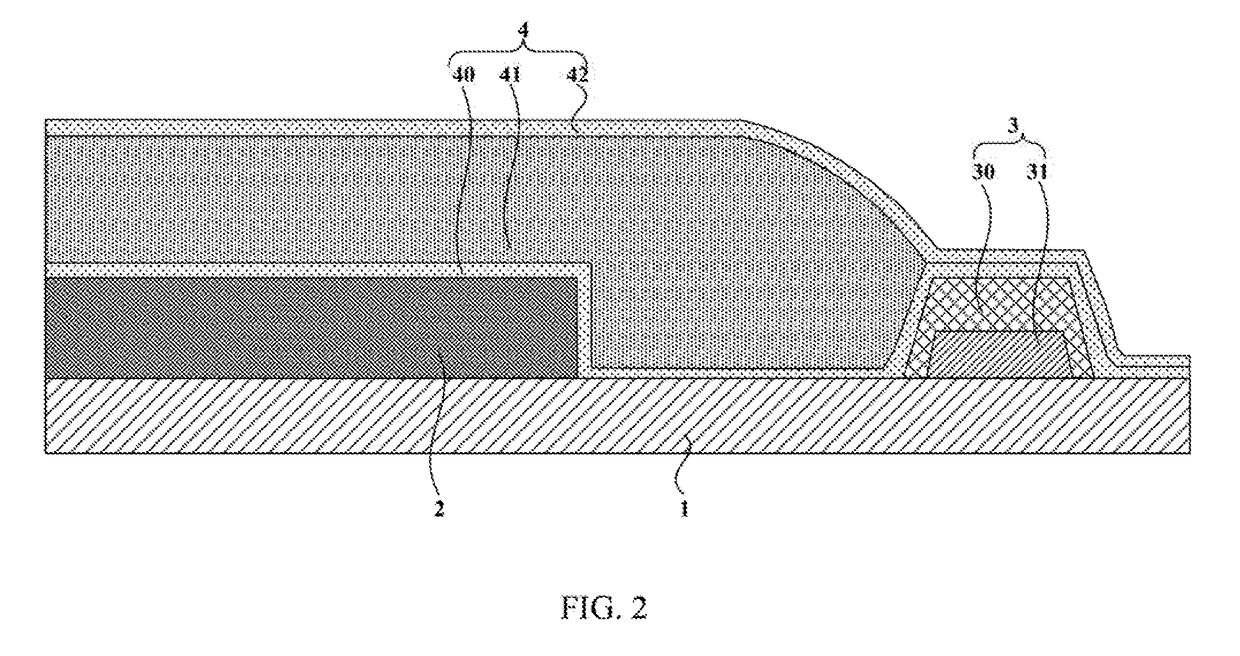

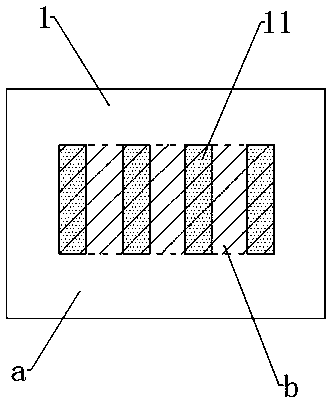

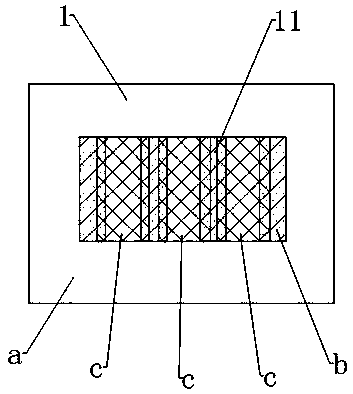

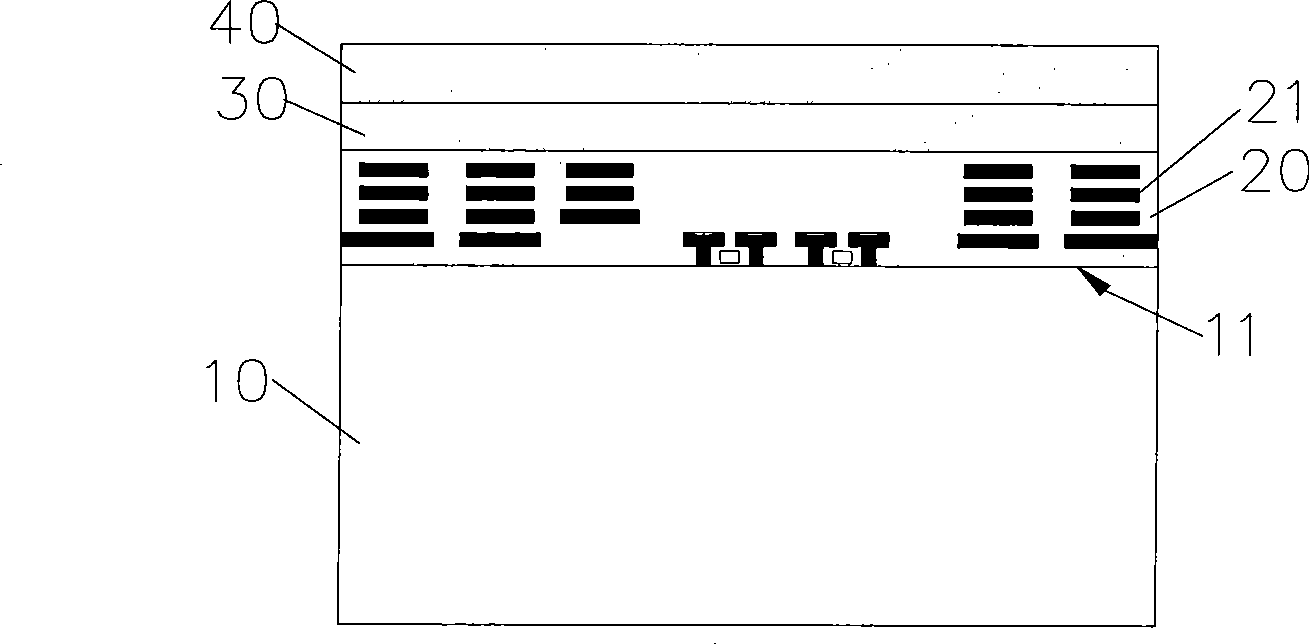

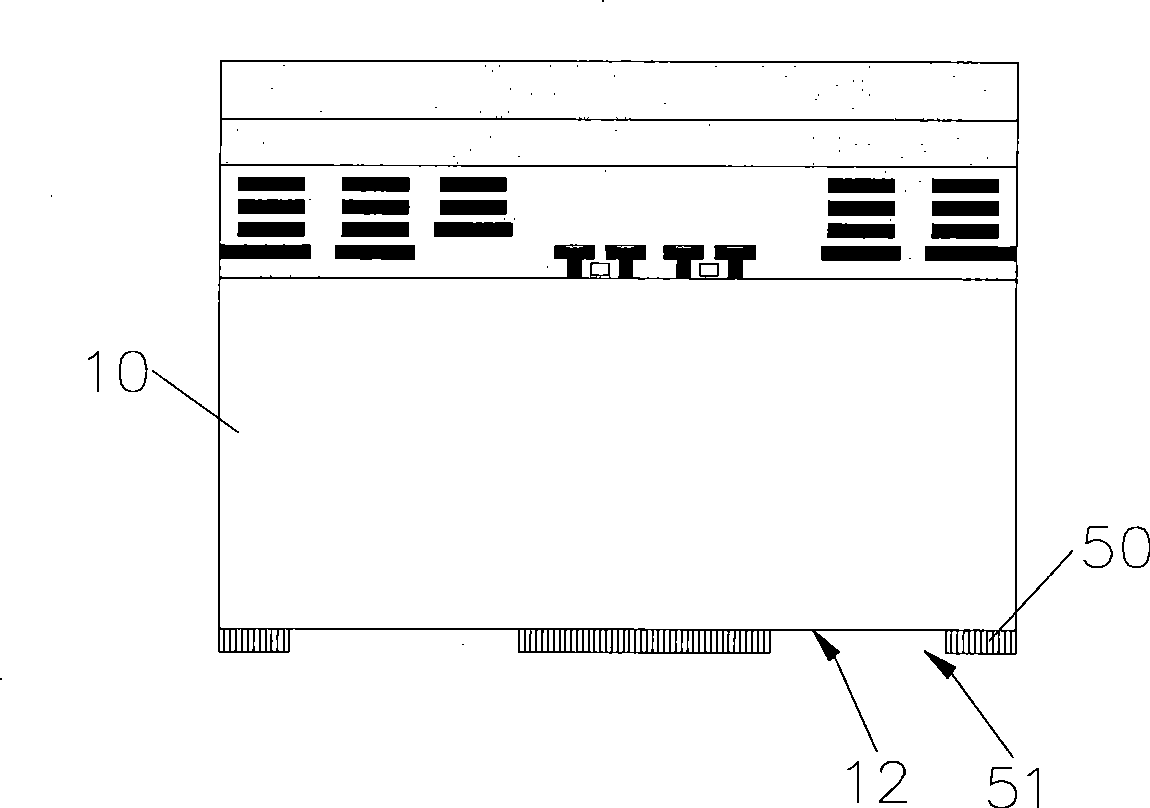

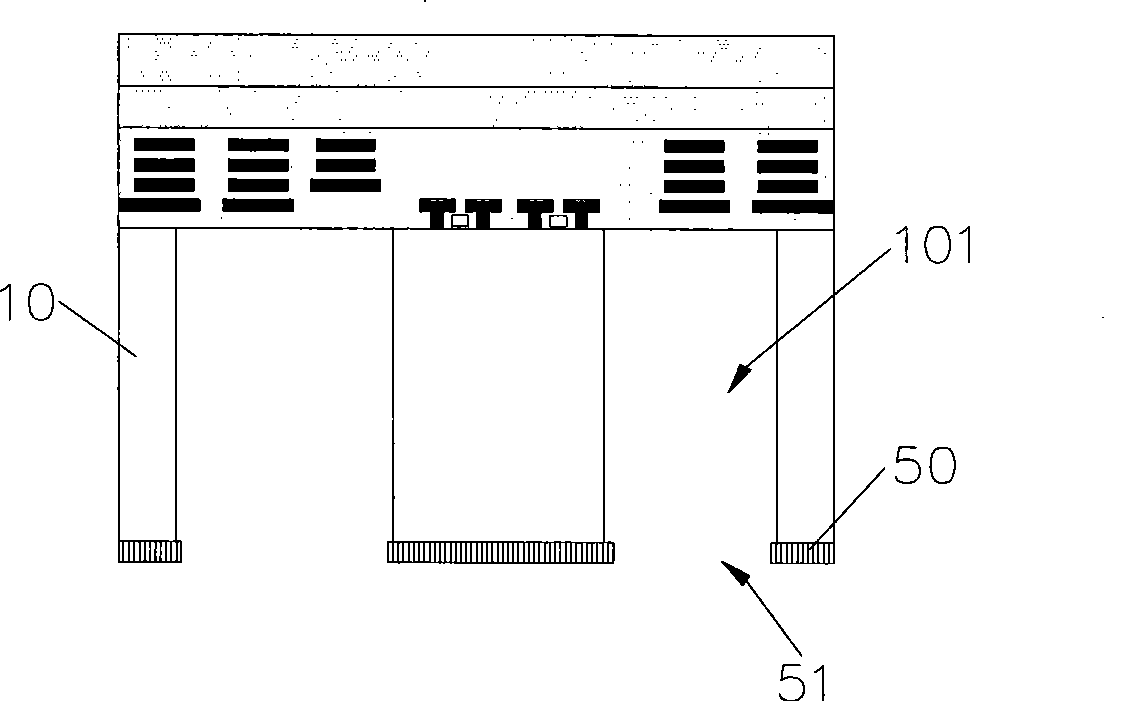

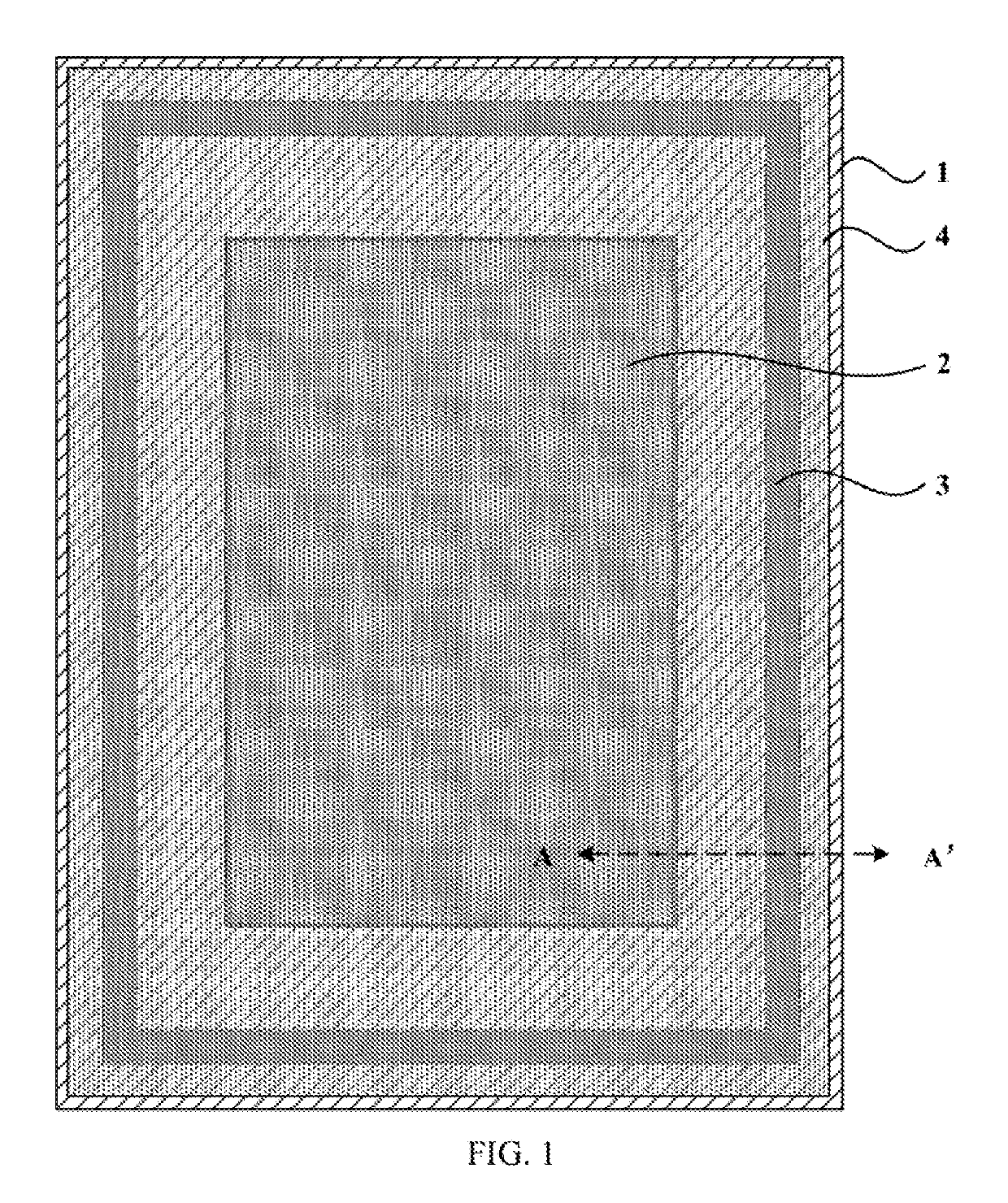

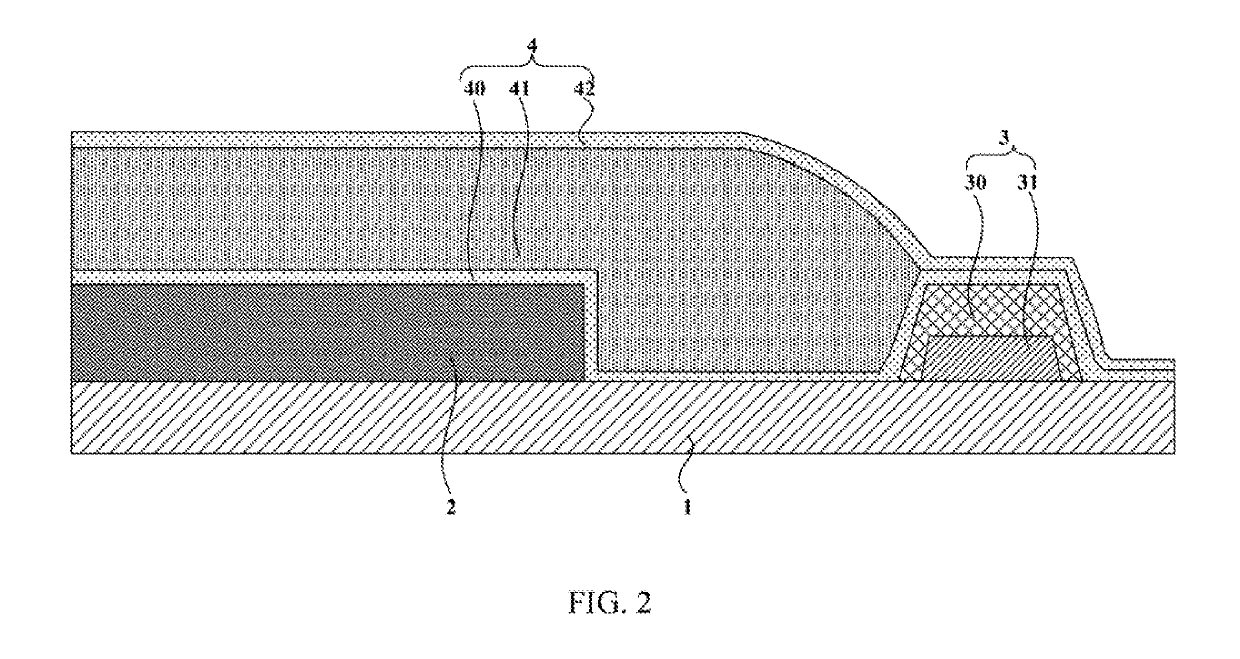

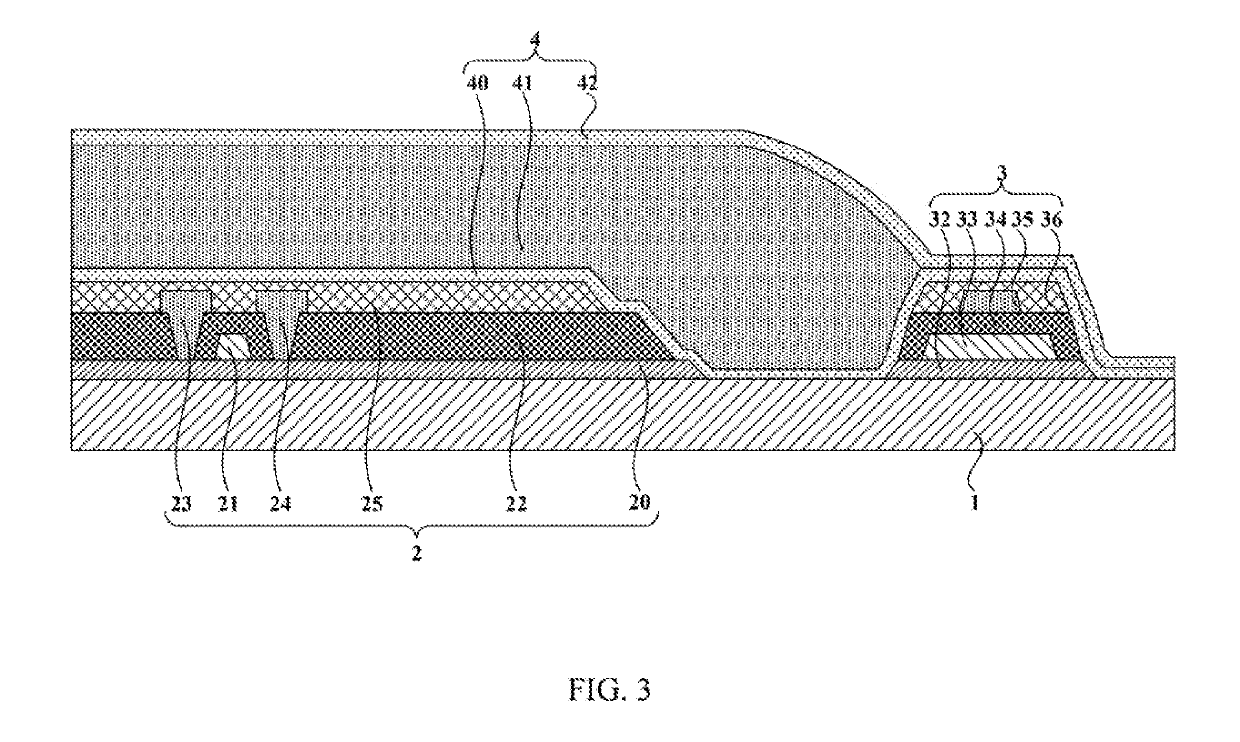

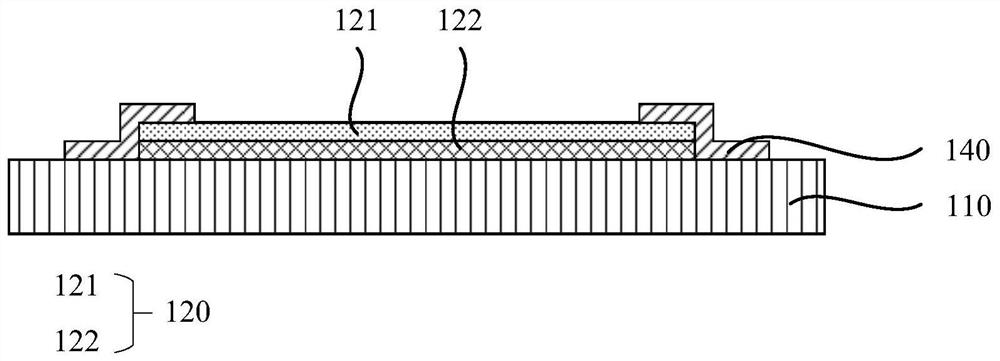

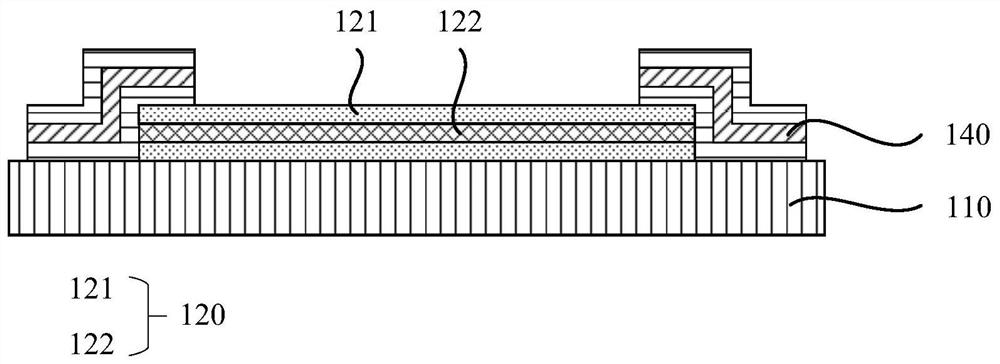

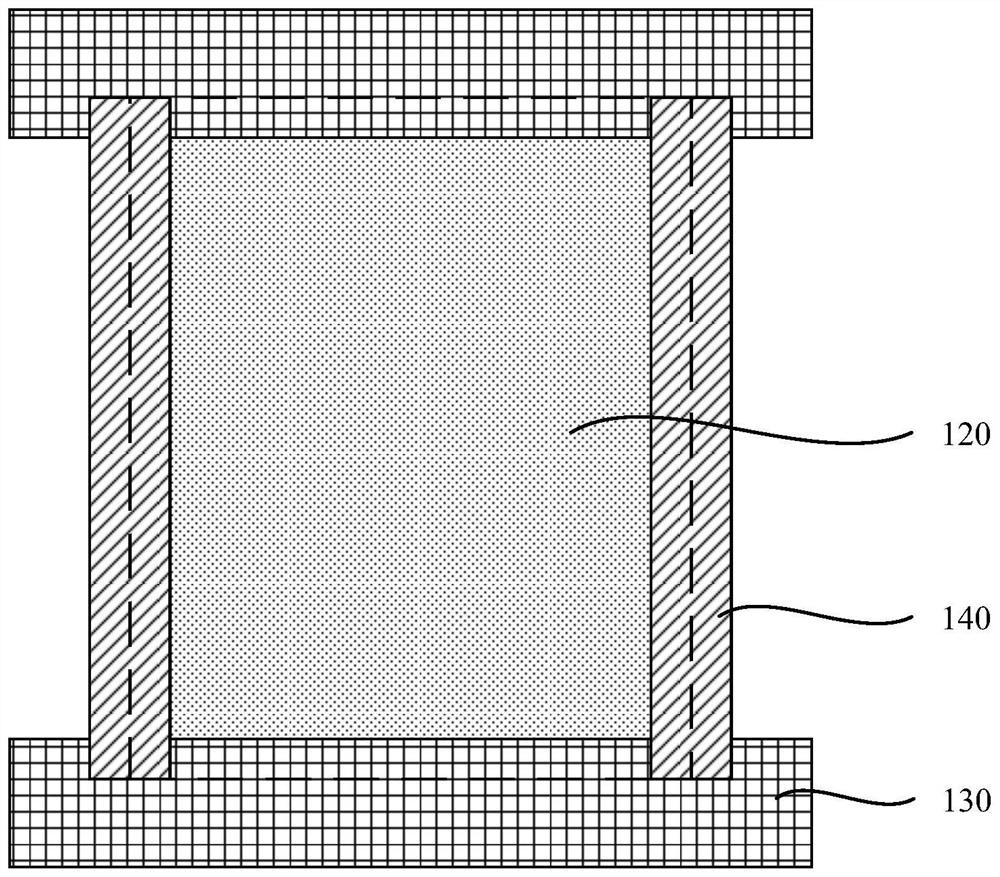

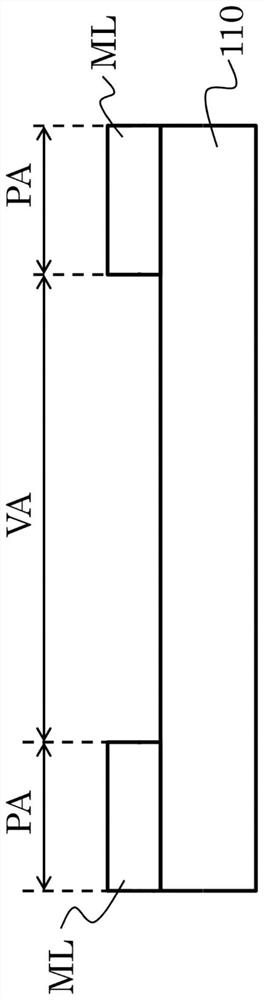

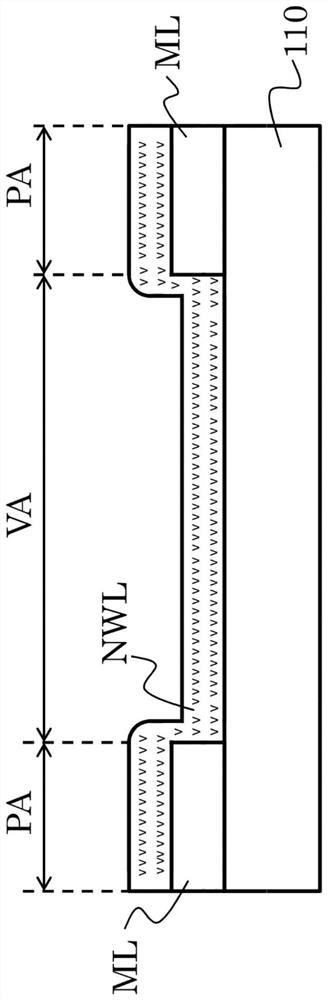

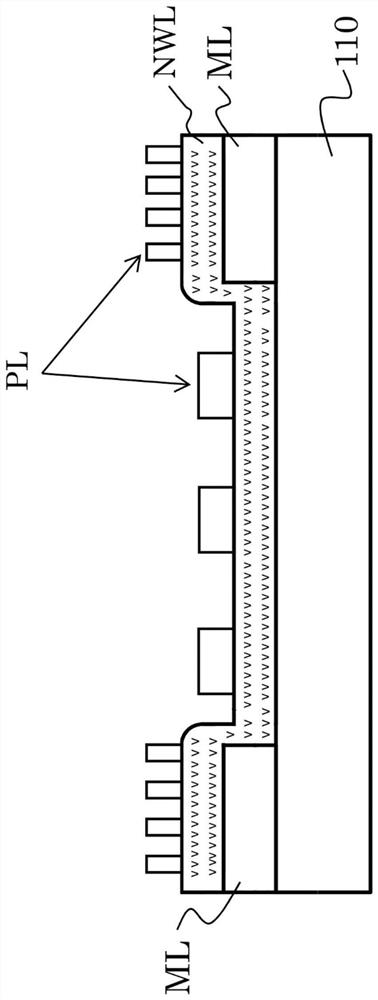

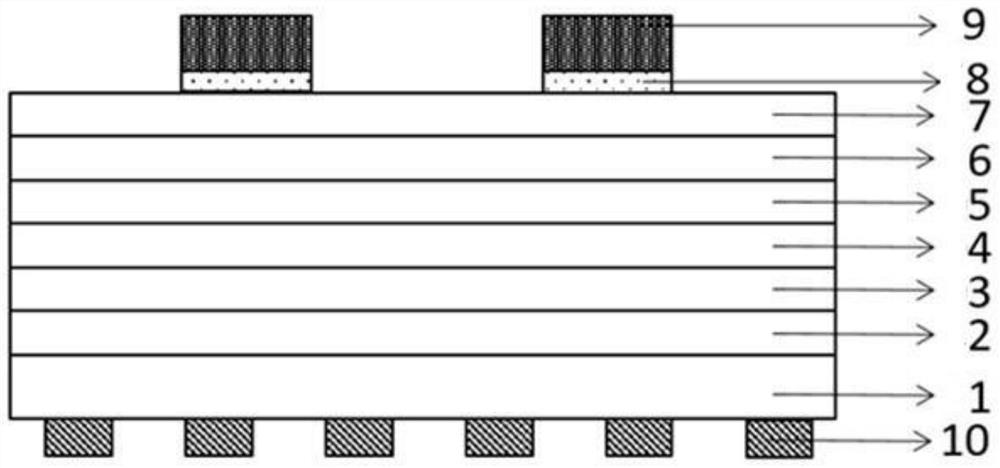

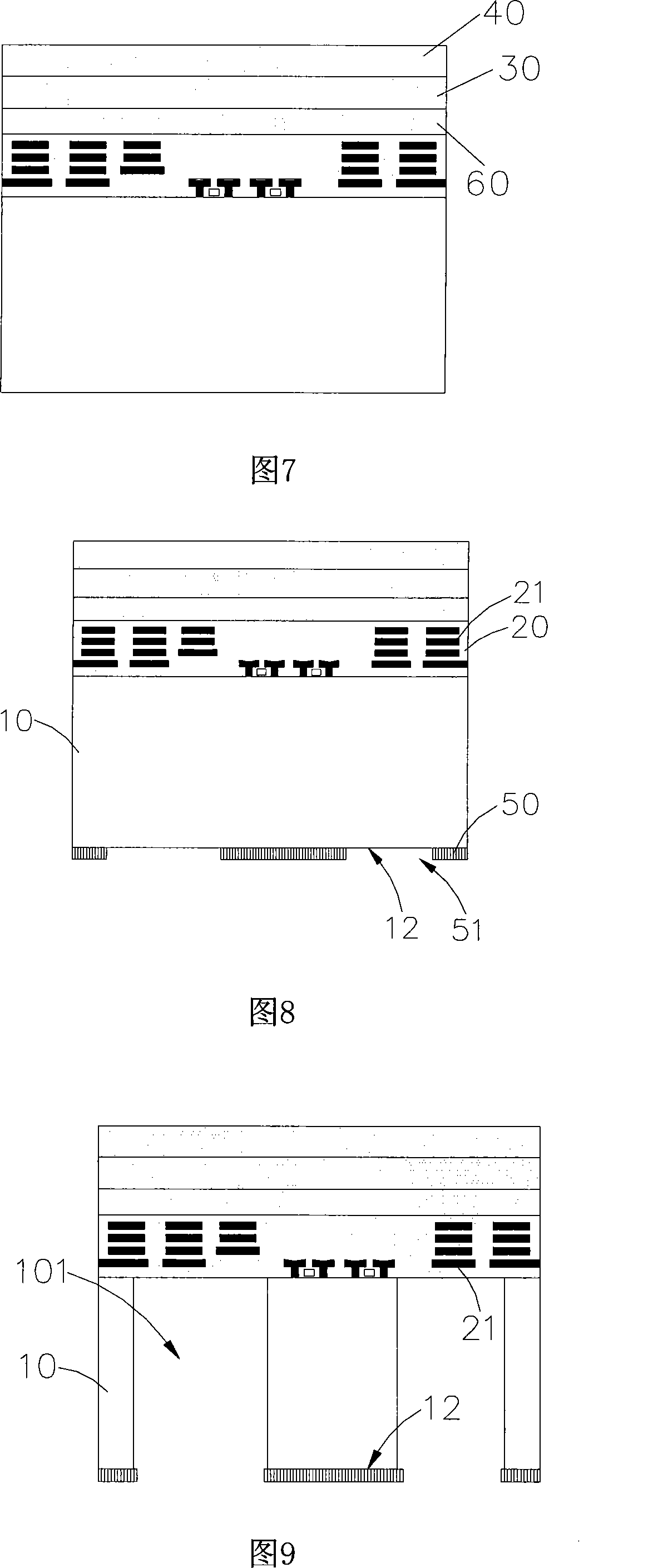

Display panel and display apparatus

ActiveUS20170244061A1Prevent side erosionCapability of the display panel to block ambient moisture and oxygen may be enhancedSolid-state devicesSemiconductor/solid-state device manufacturingOptoelectronicsInorganic layer

A display panel and a display apparatus are provided. The display panel comprises a substrate including a display region and a non-display region; a display element disposed in the display region of the substrate; and at least one bank disposed in the non-display region of the substrate and surrounding the display region. The at least one bank comprises at least one inorganic layer and at least one metal layer, and the at least one inorganic layer encapsulates the at least one metal layer.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD +1

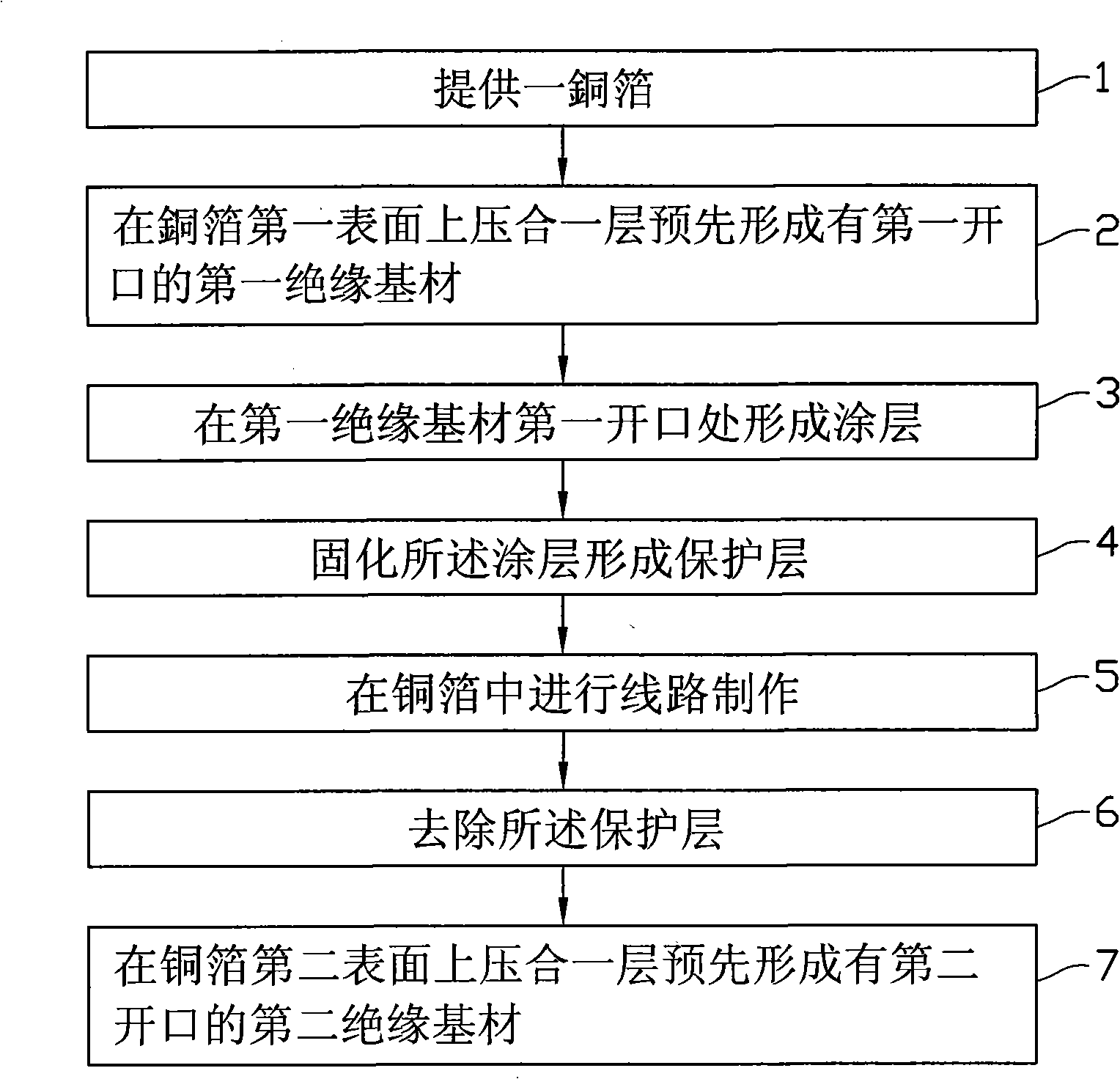

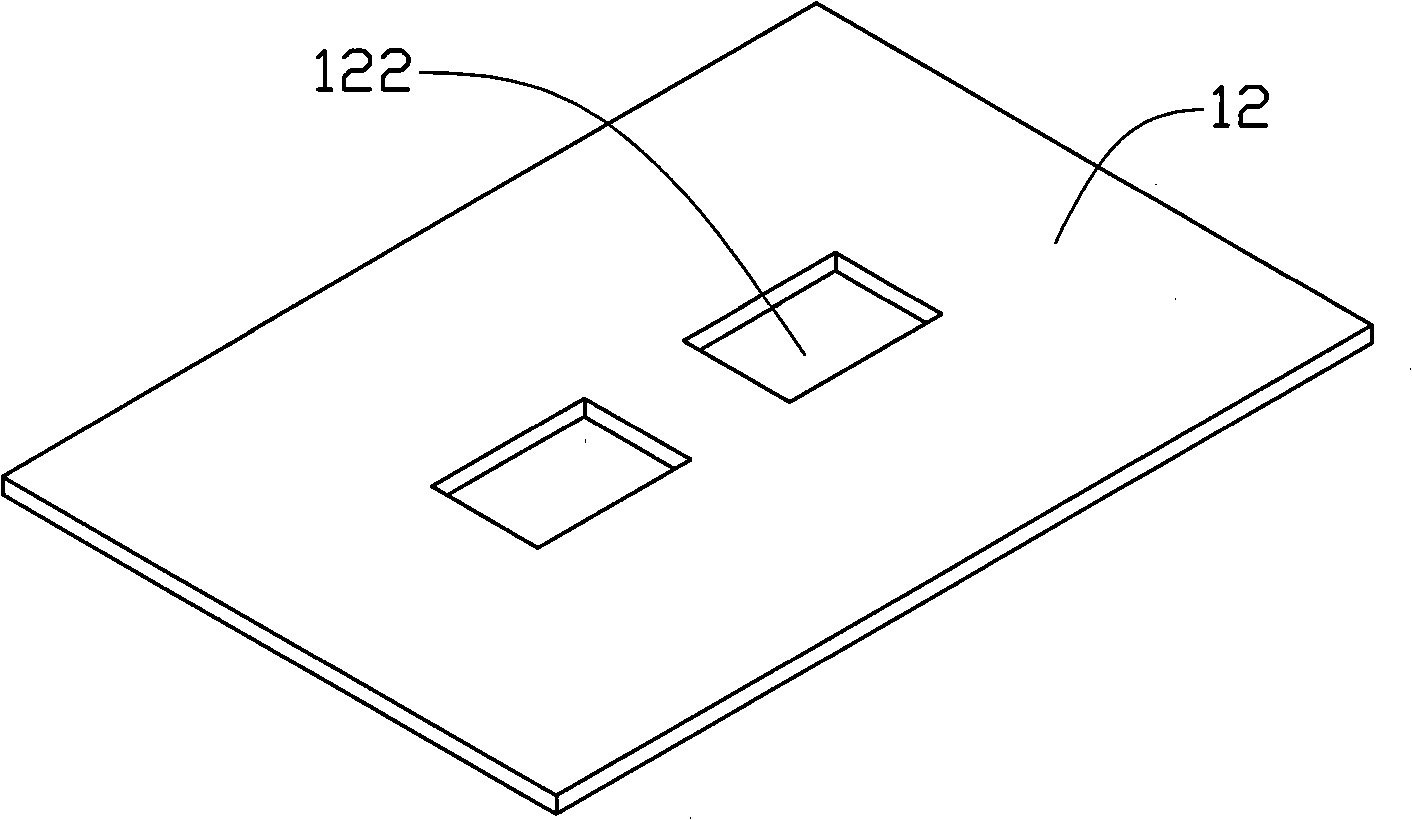

Manufacturing method of hollowed-out PCB

InactiveCN101360397APrevent side erosionPrinted circuit aspectsNon-metallic protective coating applicationCopper foilProtection layer

The invention relates to a preparing method of a skeleton circuit board, which includes steps as following: a copper foil is provided, and the copper foil includes a first surface and a second surface which are opposite; a layer of first insulating substrate with pre-shaped first opening is pressed on the first surface of the copper foil; a protection layer is formed at the opening of the first insulating substrate so as to fully cover the copper foil exposed from the first opening; a circuitry can be made in the copper foil; the protection layer at the first opening is removed; a layer of the second insulating substrate with pre-shaped second opening is pressed on the second surface of the copper foil, and the first opening is corresponding to the second opening. The preparing method of the skeleton circuit board can prevent the etching liquor from entering into the copper foil to near a side surface of the insulating substrate so as to cause the circuitry lateral erosion or over erosion.

Owner:AVARY HLDG (SHENZHEN) CO LTD +1

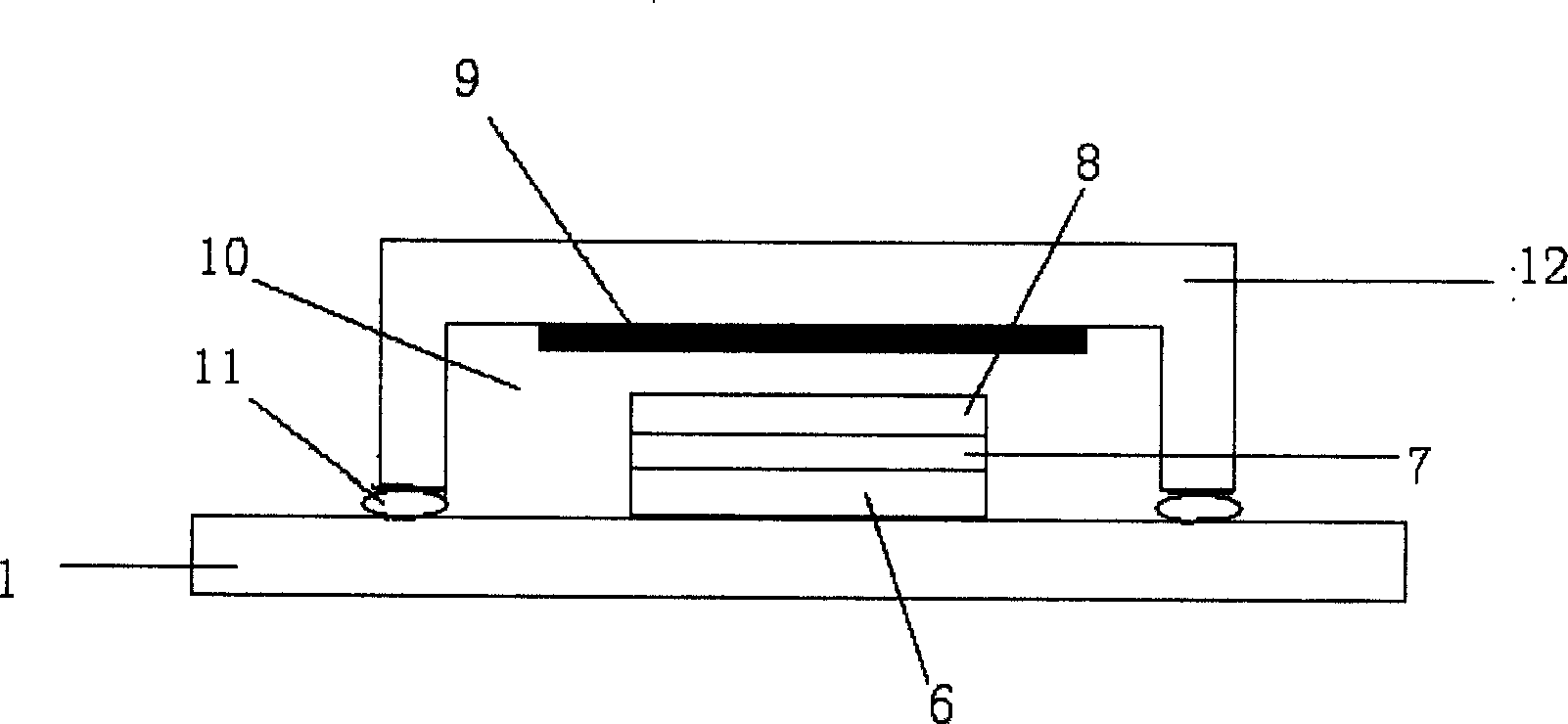

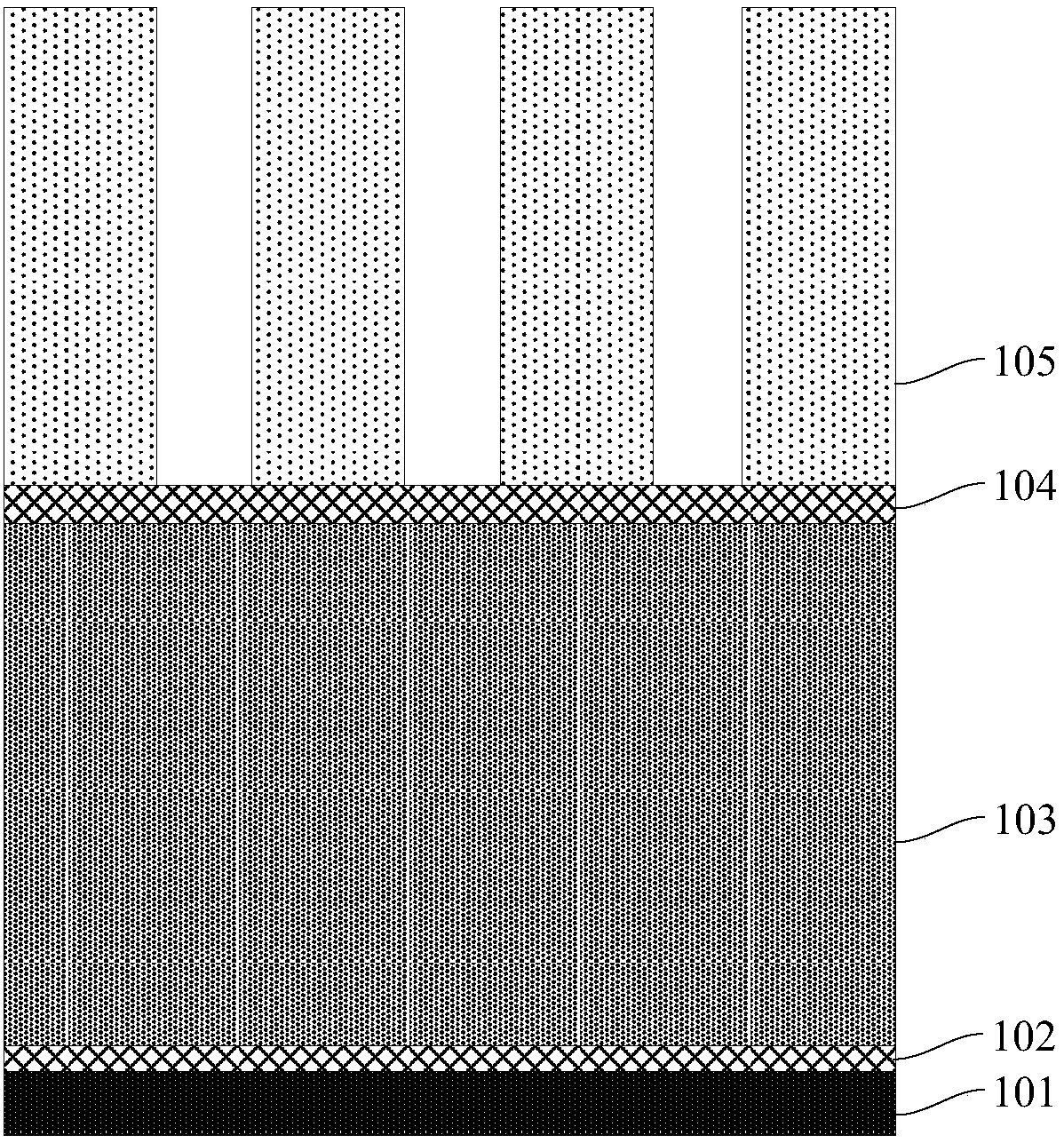

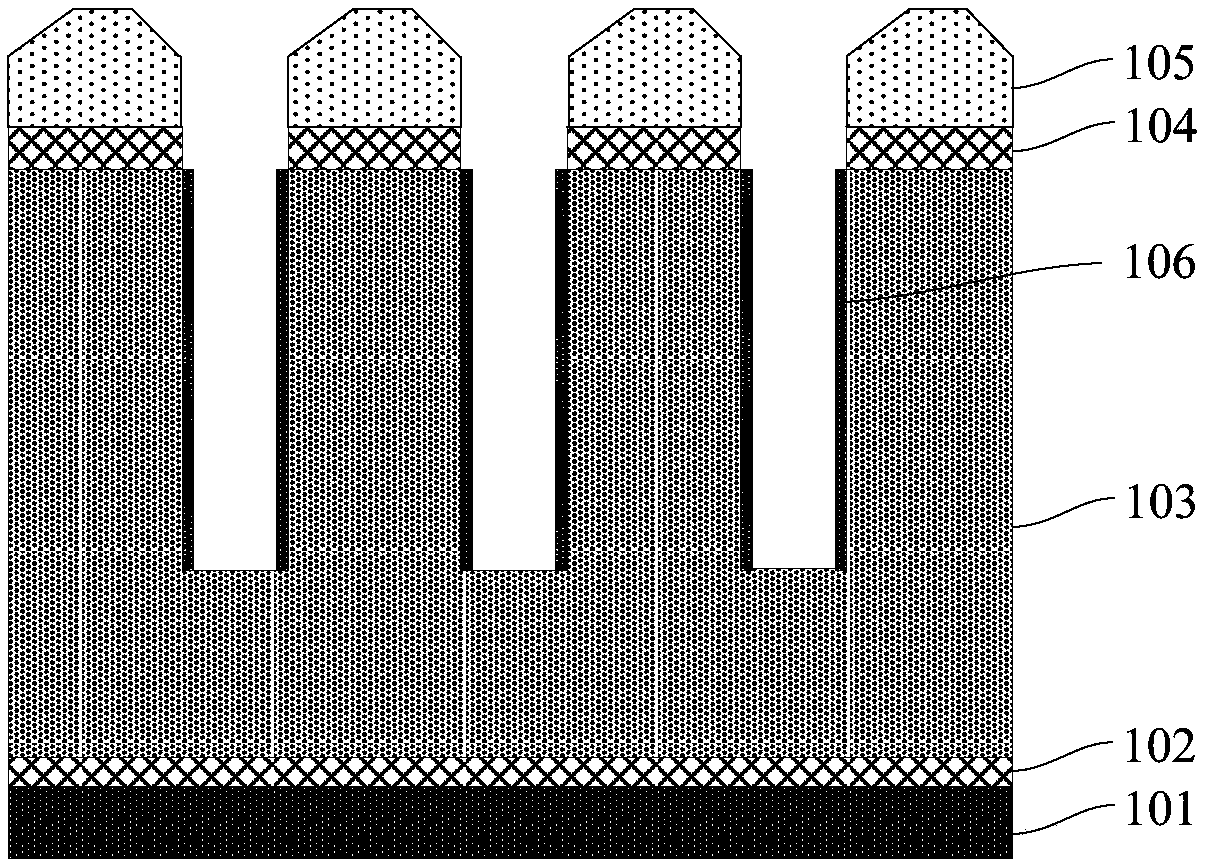

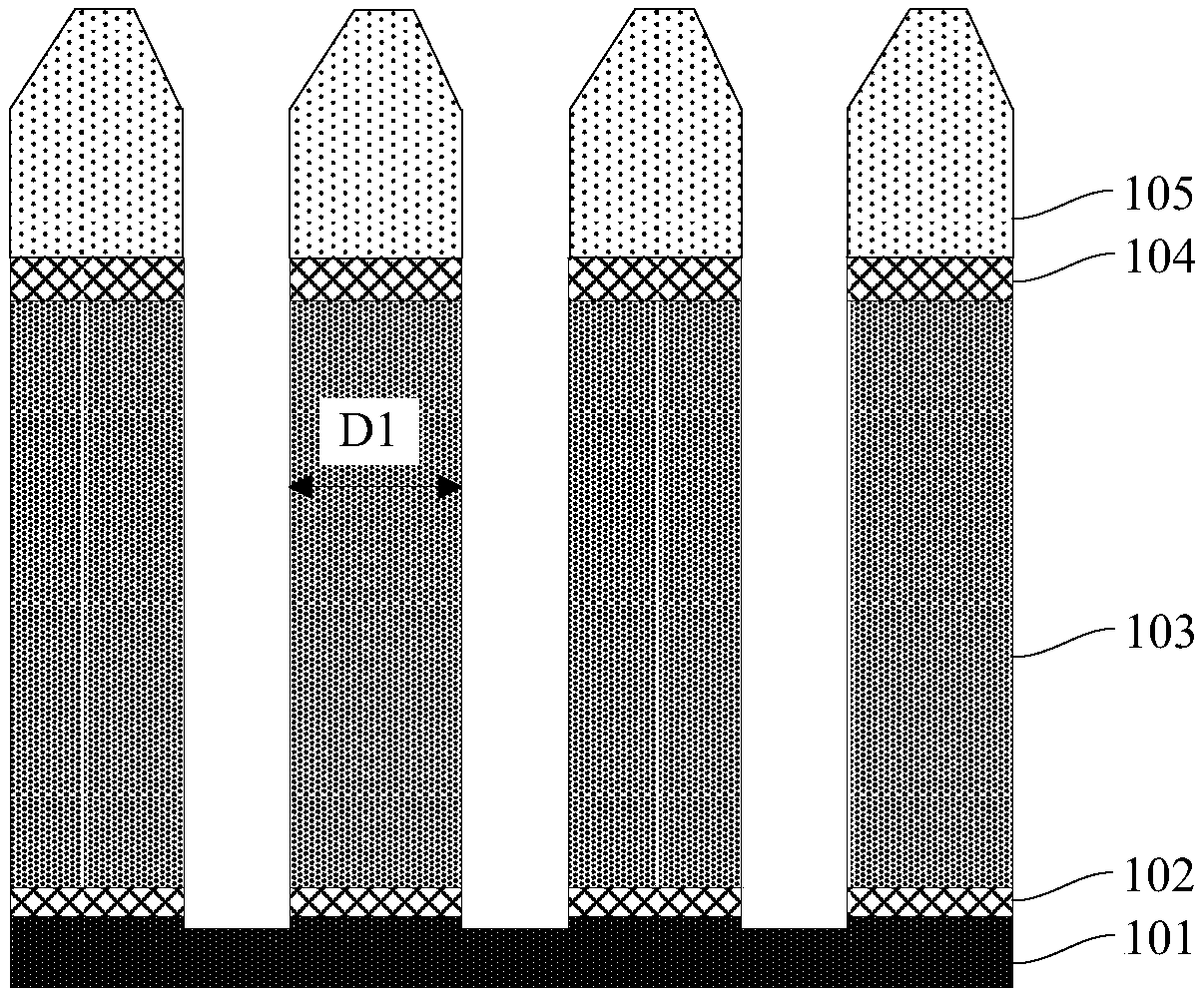

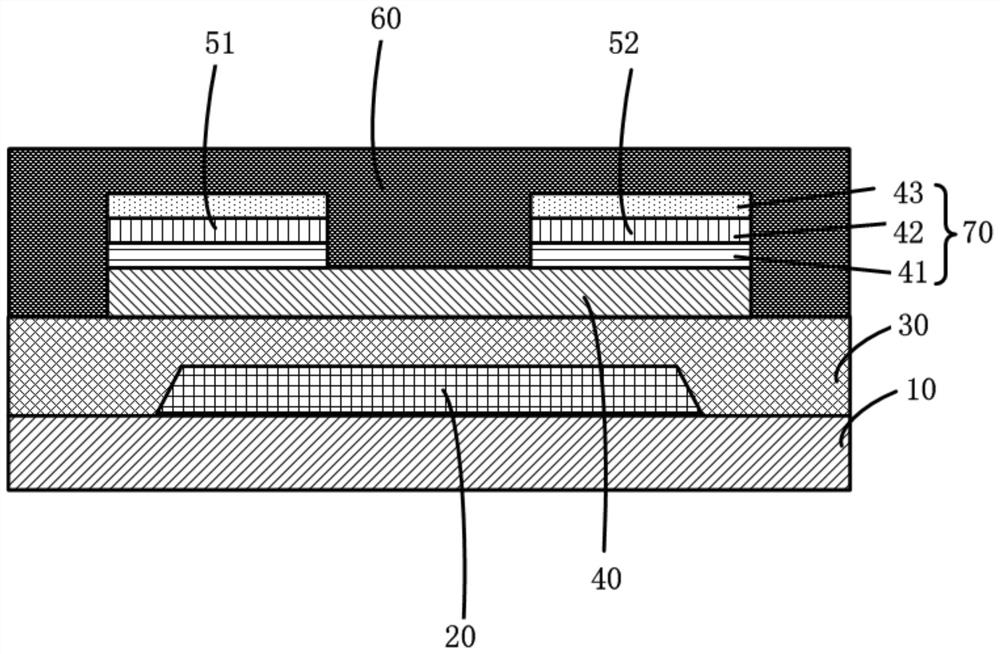

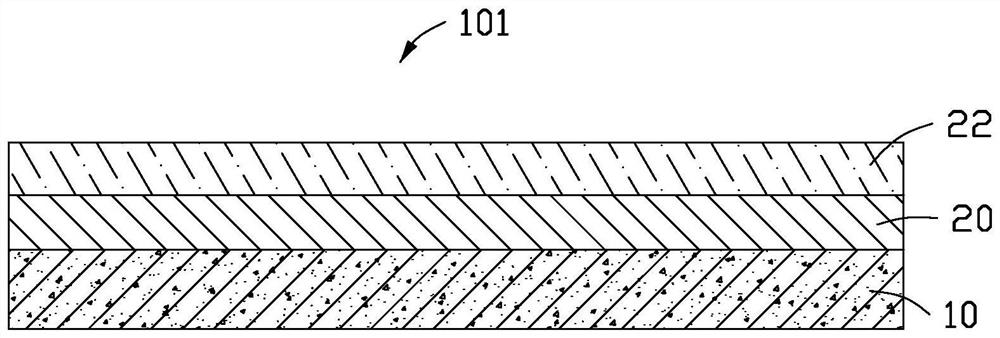

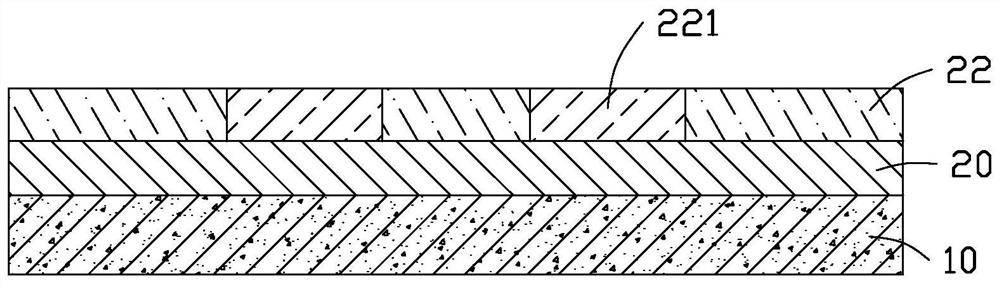

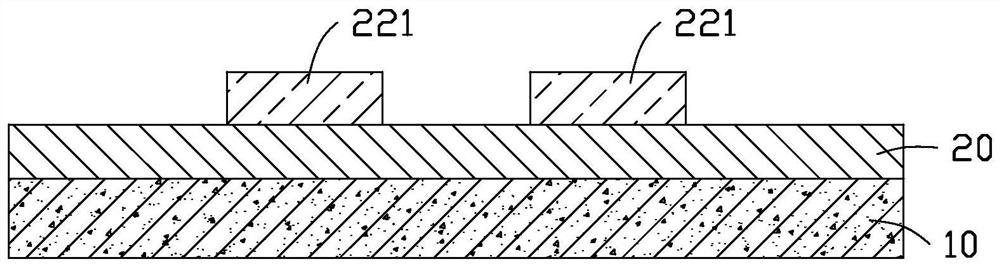

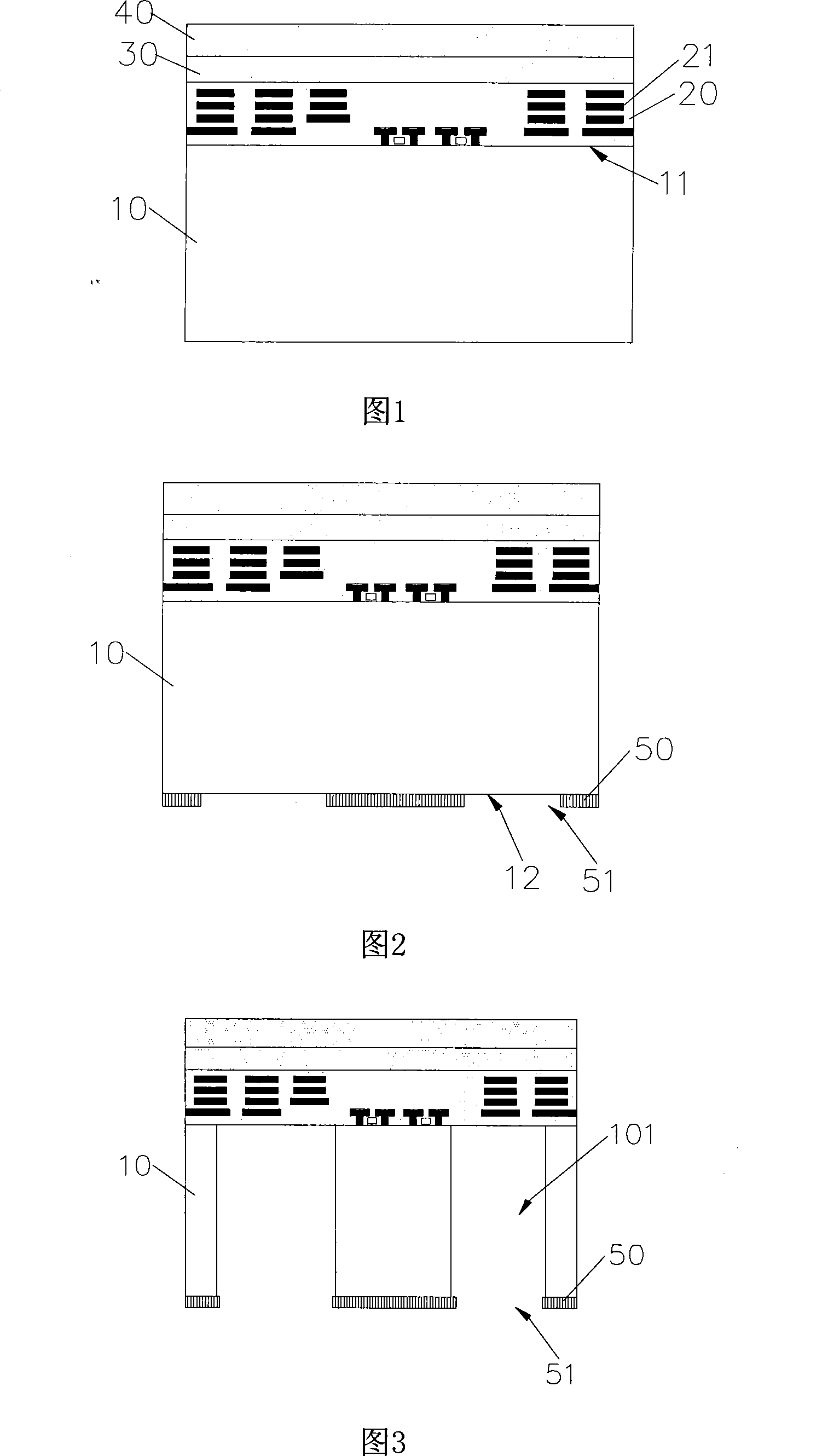

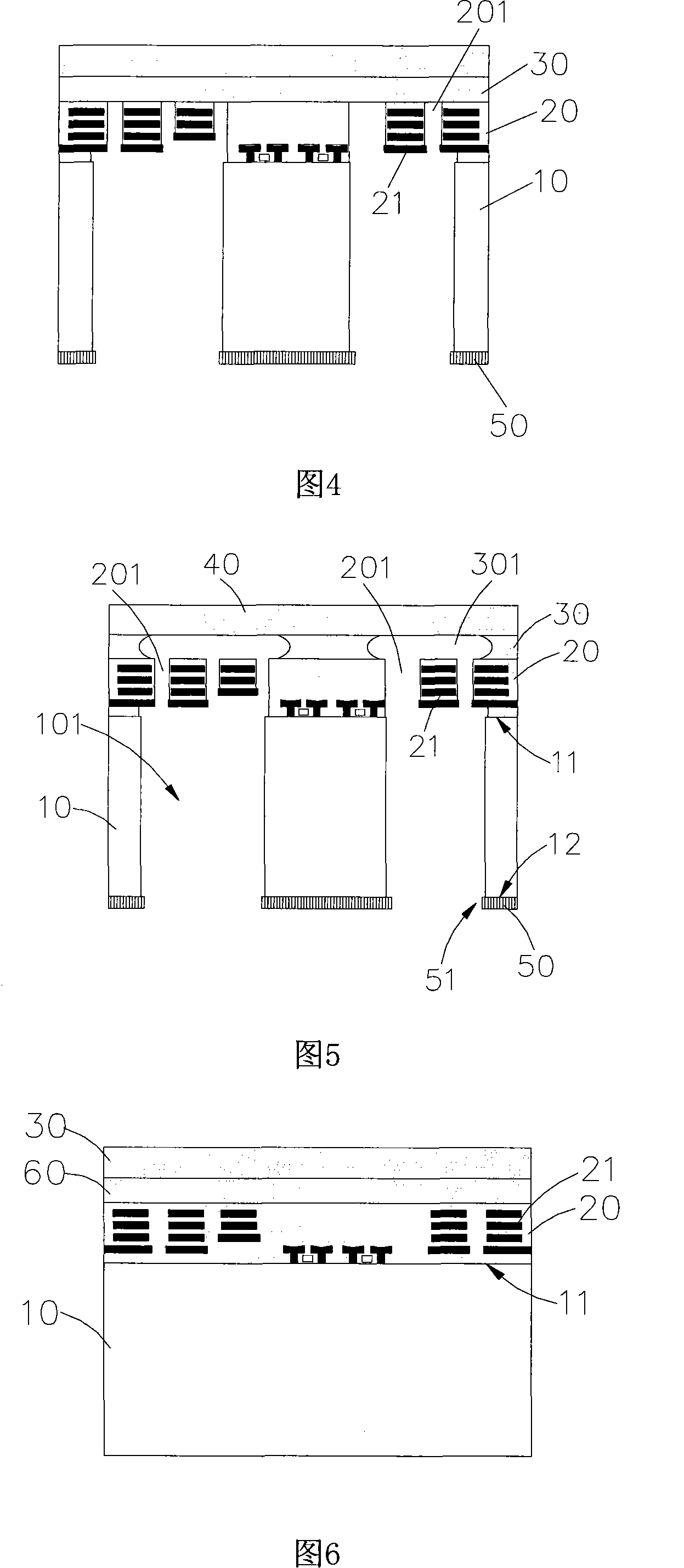

High-stability OLED device and preparation method thereof

InactiveCN109888116APrevent side erosionSolve the phenomenon of "undercut"Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringAuxiliary electrode

The invention provides a high-stability OLED device and a preparation method thereof. The high-stability OLED device comprises a substrate and a packaging cover plate 10, wherein the substrate is divided into a pixel region and a packaging region; the substrate and the packaging cover plate are connected through a sealing medium; a first electrode layer, an organic light-emitting layer and a second electrode layer are overlapped on the pixel region on the substrate; and a buffer layer is arranged between the first electrode layer and the substrate. Through the arrangement of the buffer layer,the lateral erosion phenomenon caused by dry etching of the auxiliary electrode layer is solved, and meanwhile, metal ions of the glass substrate are blocked from permeating into the first electrode layer, and electrochemical corrosion is avoided; by adding the auxiliary electrode, the brightness uniformity of a screen body is improved; a pixel defining layer is simultaneously arranged on the first electrode layer and the auxiliary electrode layer and is in direct contact with the buffer layer, so that a very good surrounding structure is formed for an effective pixel region and / or pixels of the OLED, volatile gas outgas is prevented from being released into the pixels to cause pixel shrinkage, and the reliability of the screen body of the OLED is improved.

Owner:GUAN YEOLIGHT TECH CO LTD

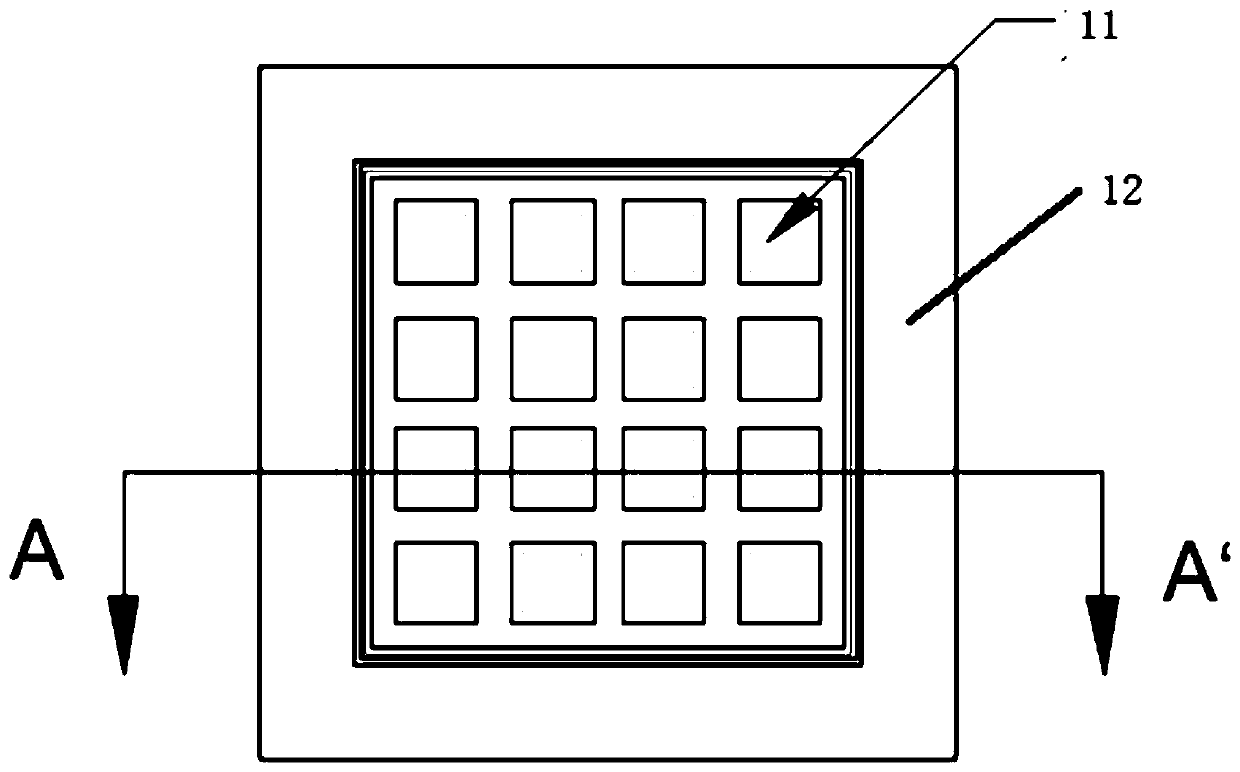

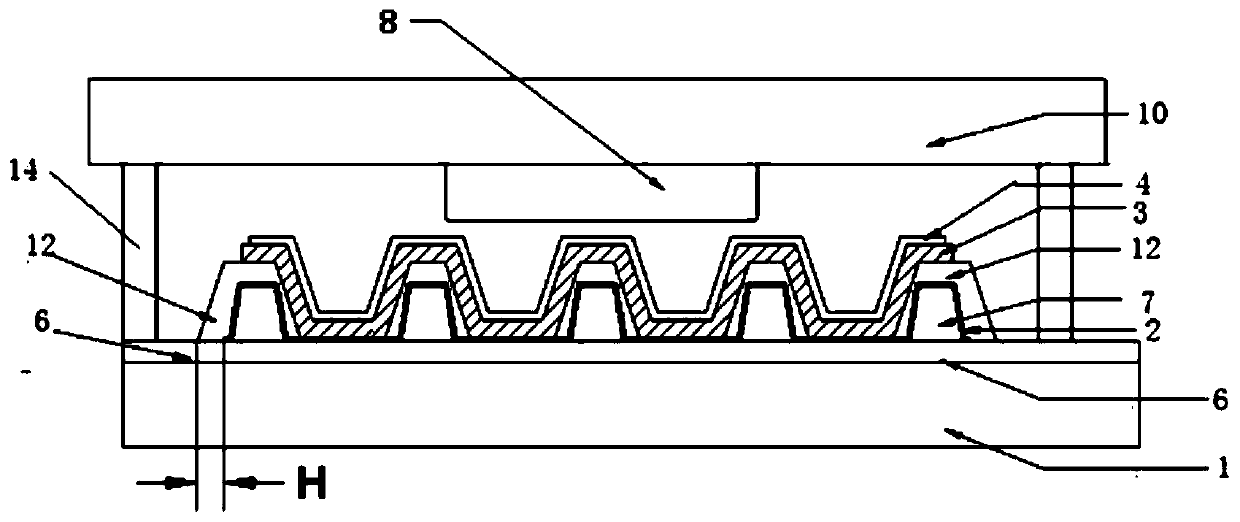

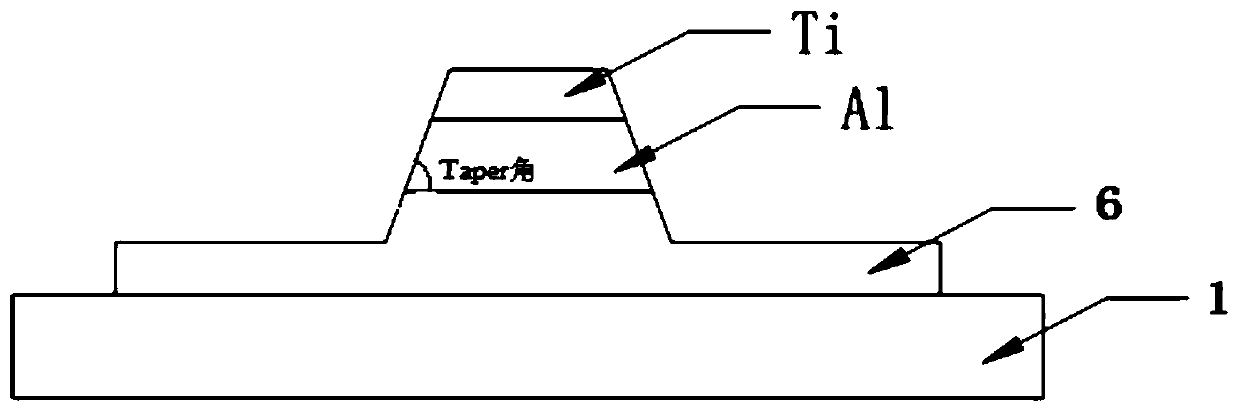

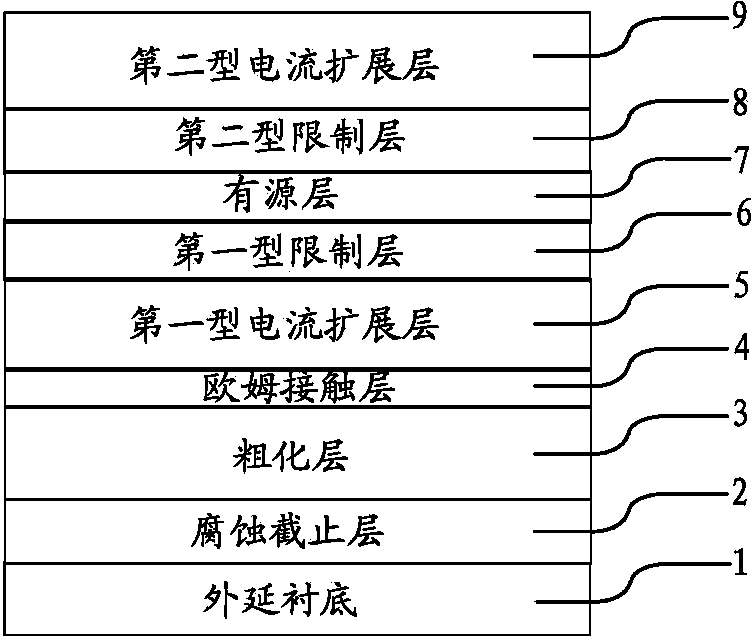

Manufacturing method for infrared light emitting diode with embedded extended electrode

InactiveCN104201268ATroubleshoot falling technical issuesPrevent side erosionSemiconductor devicesPower flowOhmic contact

The invention discloses a manufacturing method for an infrared light emitting diode with an embedded extended electrode. The manufacturing method for the infrared light emitting diode with the embedded extended electrode includes that forming a corrosion resisting layer, an armoring layer, an ohmic contact layer, a first current extension layer, a first limit layer, an active layer, a second limit layer and a second current extension layer on an epitaxial substrate in sequence; forming a metal reflector layer on the second current extension layer through evaporation; bonding a metal reflecting layer to a base plate; removing the epitaxial substrate and corrosion resisting layer to expose the armoring layer; forming an extended electrode pattern channel in the surface of the armoring layer, wherein the channel is deep enough to expose the ohmic contact layer; evaporating metal material in the channel to form the extended electrode; manufacturing a bonding pad electrode at the surface of the armoring layer, and communicating the bonding pad electrode with the extended electrode; evaporating a back electrode at the back of the base plate, removing protecting layers of the bonding pad electrode and extended electrode, and shredding to obtain the infrared light emitting diode with the embedded extended electrode. The manufacturing method for the infrared light emitting diode with the embedded extended electrode is capable of improving the reliability of the extended electrode, obtaining better current extension effect and improving the light emitting efficiency of the infrared light emitting diode.

Owner:XIAMEN CHANGELIGHT CO LTD

Mask for glass etching and its use for glass etching

This invention relates to a new type of mask used in glass etching and its application in it, in which, said new mask includes at least two layers of structures, one is mask material, the other is a glue layer, the mask material is placed above the glue layer and connected with an etched glass via the glue layer, said new mask can be bond on the etched glass stably and not easy to be corroded by acid and the mask is fixed in the etching of glasses.

Owner:SHENZHEN TCL IND RES INST

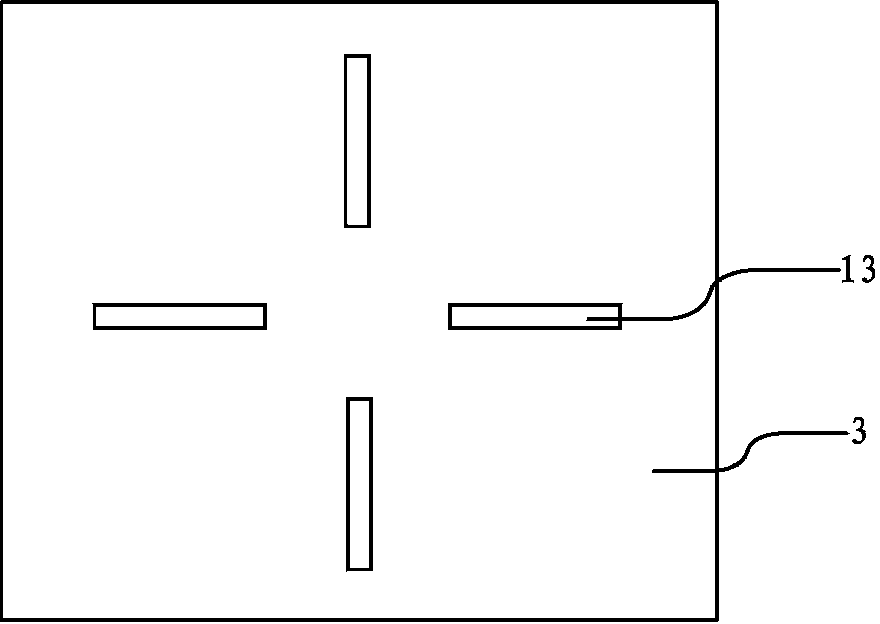

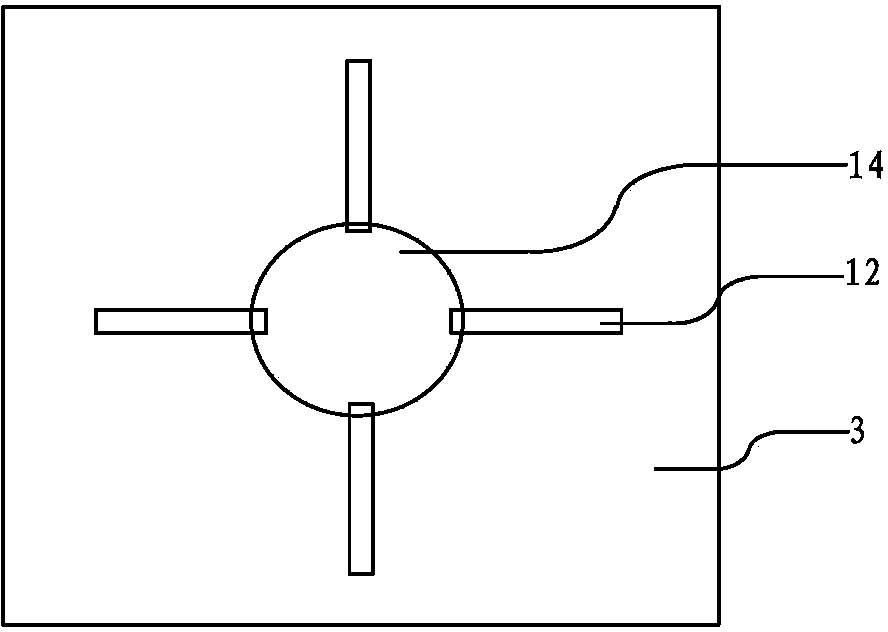

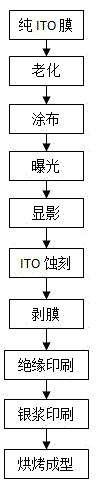

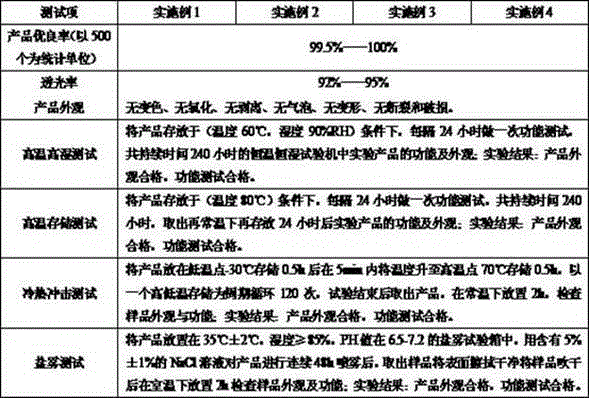

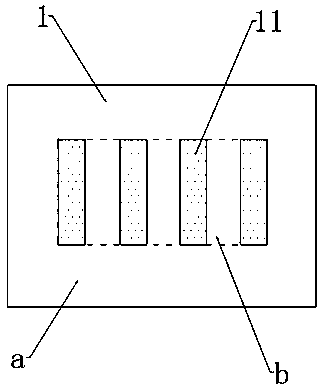

Process for manufacturing single-layer multi-point capacitive touch screen with pure ITO membrane structure

InactiveCN104820535AReduce etching processAvoid side erosion problemsInput/output processes for data processingPhysicsChemistry

The invention relates to a process for manufacturing a single-layer multi-point capacitive touch screen with a pure ITO membrane structure and belongs to the technical field of touch screen manufacturing. The process sequentially comprises the steps of the cutting of an ITO membrane of a predetermined dimension, ageing, coating, exposure, developing, etching, membrane striping, insulating printing, silver paste printing and baking. The pure ITO membrane is adopted to serve as a raw material; compared with the adoption of a copper plating ITO membrane for a traditional yellow light process, a copper etching process is omitted, original partial printing of silver paste jumpers is modified into silver paste printing of a whole metal layer, silver wires are utilized to replace copper wires, the lateral erosion problem of copper etching is avoided, and chemicals used for etching and lateral erosion restraint are saved. In the aspect of the process, a manufacturing process is simplified, resources in the aspects of manpower, energy and auxiliary materials can be saved, and the rejection rate is reduced.

Owner:GUANGDONG TAITONG SCI TECH

Method for silk-screening solder resist ink on PCB with small-spacing bonding pads

ActiveCN110475434APrevent side erosionPrevent fallingFinal product manufactureNon-metallic protective coating applicationResistScreen printing

The invention discloses a method for silk-screening solder resist ink on a PCB with small-spacing bonding pads. The method comprises the steps of: performing silk-screening the solder resist ink on the surface of a PCB twice, performing silk-screening the solder resist ink in a bonding pad area for the first time, and performing silk-screening the solder resist ink in a position outside the bonding pad area on the PCB for the second time, wherein the first silk-screen printing of the solder resist ink comprises the following steps of: S1, silk-screen printing of ink: silk-screen printing of ink is performed on a position between the adjacent bonding pads in the bonding pad area, and the silk-screen printing ink area is expanded to the bonding pads; S2, pre-drying treatment: the silk-screenprinting ink is dried to be a non-sticky object; S3, exposure processing: ink silk-screened in the area between the bonding pads is exposed, and the exposure area is expanded to the bonding pads; S4,developing treatment: the oil ink on the bonding pads and on the outer side of the bonding pads is removed through a developing solution; S5, curing treatment: curing treatment is performed on the ink left by development between the bonding pads and on the bonding pads; and S6, polishing treatment: polishing and removing the ink cured on the bonding pads are performed. The method for silk-screening solder resist ink on the PCB with small-spacing bonding pads is used for PCB silk-screen solder resist ink of small-spacing bonding pads.

Owner:惠州美锐电子科技有限公司

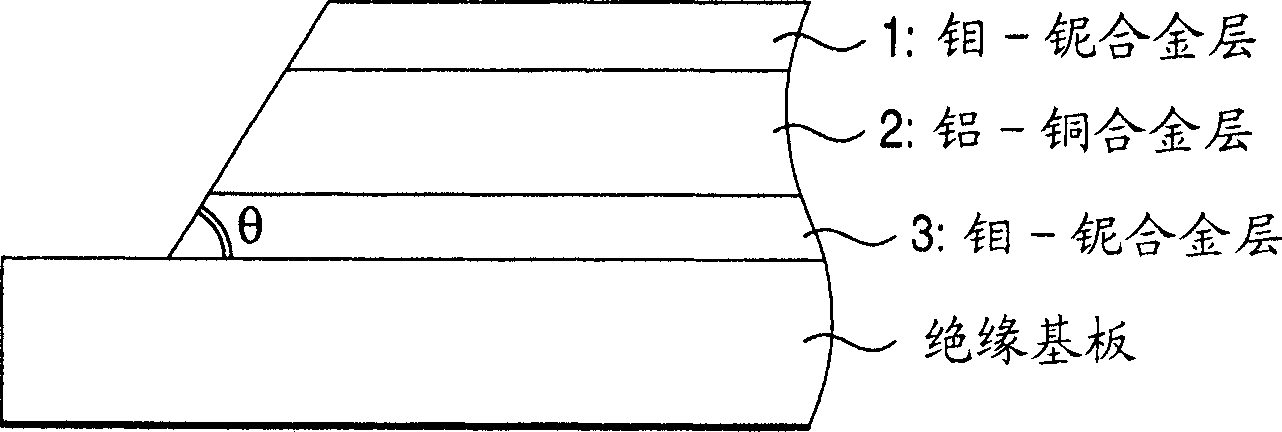

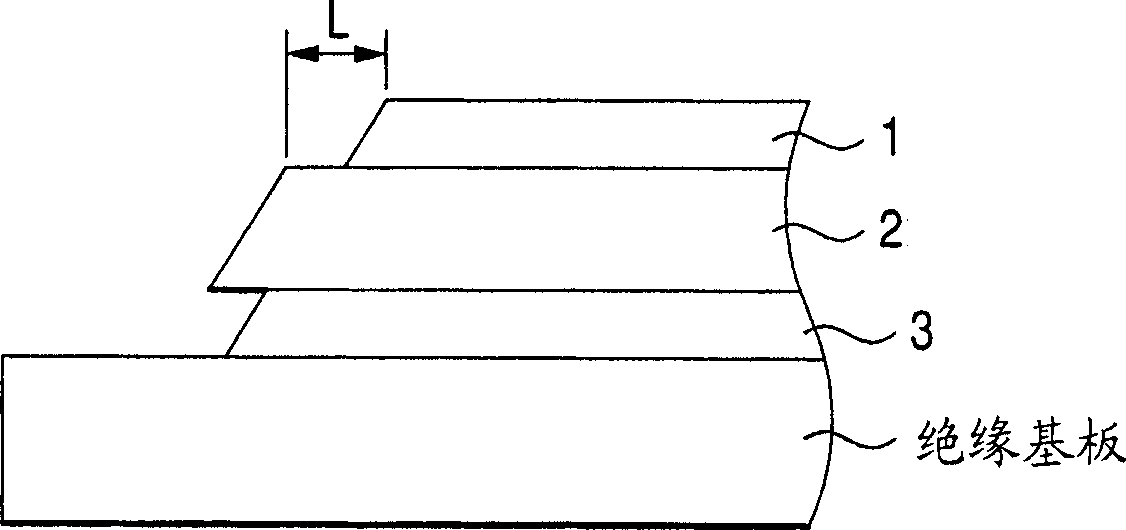

Etchant and etching method

InactiveCN1798874AAvoid undercutPrevent side erosionSemiconductor/solid-state device manufacturingNiobiumVolumetric Mass Density

Fluorescent probes represented by the general formula (I) wherein R<1> and R<2> are each hydrogen or a substituent for capturing a proton, a metal ion, or an active oxygen species; R<3> is a monovalent substituent except hydrogen, carboxyl, and sulfo; R<4> and R<5> are each hydrogen, halogeno, or alkyl; R<6> to R<9> are each alkyl; R<10> and R<11> are each hydrogen, halogeno, or alkyl; M<-> is a counter ion; and before the capture of a proton, a metal ion, or an active oxygen species, the combination of R<1>, R<2>, and R<3> gives the benzene ring to which they are bonded such a substantially high electron density as to make the compound substantially nonfluorescent, while after the capture of a proton, a metal ion, or an active oxygen species, the combination brings about such a substantial lowering in the electron density of the benzene ring to which they are bonded as to make the compound substantially highly fluorescent.

Owner:MITSUBISHI CHEM CORP +1

Method for manufacturing semiconductor micro electromechanical structure

InactiveCN101434375AShorten the timePrevent side erosionDecorative surface effectsChemical vapor deposition coatingEtchingSemiconductor

The invention discloses a method for manufacturing a semiconductor micro electronmechanical structure, which comprises the steps: firstly, at least one insulation circuit layer internally provided with a micro electronmechanical structure is produced on the upper surface of a silicon substrate, and a sacrifice layer and a blocking layer are sequentially produced on the upper surface of the insulation circuit layer from interior to exterior; secondly, an etching blocking layer is made on the lower backface of the silicon substrate, and deep reactive ion etching or wet etching is carried out to the lower backface of the silicon substrate so as to form a space corresponding to the micro electronmechanical structure; and finally etching is carried out to the insulation circuit layer and the sacrifice layer in sequence to lead the micro electronmechanical structure to be suspended. Therefore, lateral erosion can be effectively avoided, the probability of exposure and damage of the micro electronmechanical structure is low, and the final encapsulation cost can be reduced by being integrated with common integrated circuit packaging technologies.

Owner:MEMSMART SEMICON

Manufacturing method of ultra-precision circuit

ActiveCN111050484AAvoid the line thinning problem when the side erosion arrivesAvoid line thinningConductive material chemical/electrolytical removalMultilayer circuit manufactureEtchingLayer thickness

The invention discloses a manufacturing method of an ultra-precision circuit. The method comprises the following steps that: S1, an outer-layer circuit is manufactured on an outer-layer copper surfaceof a production board through a negative film process, and it is ensured that the thickness of the outer-layer copper surface is smaller than a circuit copper layer thickness required by design; S2,a film is pasted on the production board through a positive film process, and exposing and developing are performed sequentially, so that an outer-layer circuit pattern is formed, and the outer-layercircuit manufactured in the step S1 is exposed; S3, the copper layer thickness of the outer-layer circuit on the production board is made to be the circuit copper layer thickness required by design through pattern electroplating; and S4, finally, the film is removed. According to the method, the ultra-precise circuit can be manufactured by adopting a mode of combining the negative film process andthe positive film process; and the problem that the ultra-precise circuit cannot be manufactured due to side etching and side electroplating in a conventional circuit process is solved.

Owner:JIANGMEN SUNTAK CIRCUIT TECH

Metal wire manufacturing method and metal wire isolating method

InactiveCN107910258AEtch rate reductionIncrease residueSemiconductor/solid-state device manufacturingLine widthPhotoresist

The invention provides a metal wire manufacturing method and a metal wire isolating method. The method comprises the steps that 1) an anti-reflection layer is formed on a metal layer; 2) a photoresistlayer is formed on the anti-reflection layer, and an etching window is formed in the photoresist layer; and 3) a halogen-containing gas is used and an alkane-based gas is added to etch the metal layer to separate the metal layer into a number of metal lines. The alkane-based gas reacts with the halogen-containing gas to generate an auxiliary carbon halogen compound, so as to avoid the side etching of the sidewall of the metal lines and reduce the consumption rate of the photoresist layer during the etching process. According to the invention, the added alkane-based gas is used as the source of an etching aluminum by-product CClx, which can effectively reduce the etching rate of the photoresist layer; reduced line width of the metal lines and top damage, which are caused by insufficient residue of the photoresist layer, are avoided; side etching of the sidewall of the metal lines is avoided through the by-product CClx; and the overall width of the metal lines is the same as the targetwidth.

Owner:CHANGXIN MEMORY TECH INC

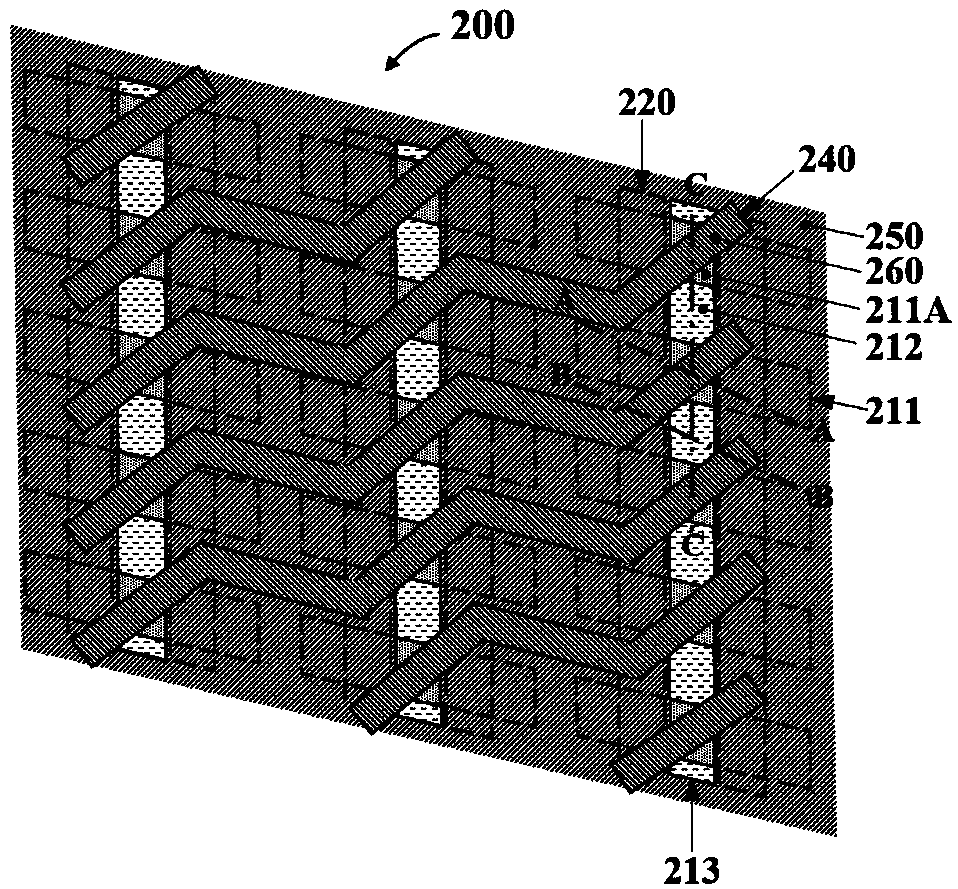

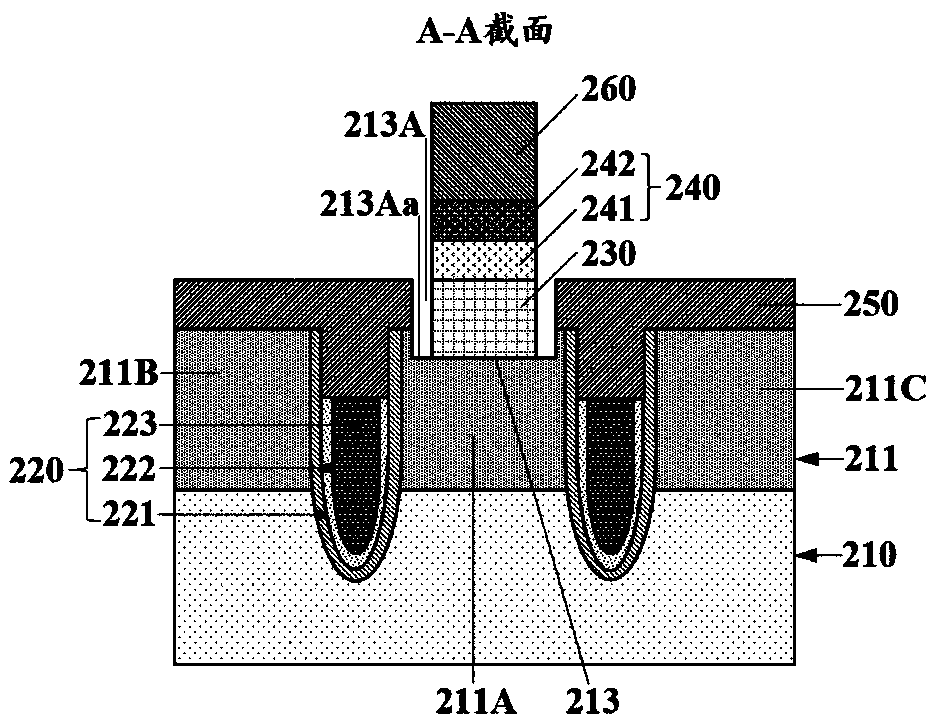

Display panel and display apparatus

ActiveUS10276823B2Prevent side erosionCapability of the display panel to block ambient moisture and oxygen may be enhancedStatic indicating devicesSolid-state devicesOptoelectronicsInorganic layer

A display panel and a display apparatus are provided. The display panel comprises a substrate including a display region and a non-display region; a display element disposed in the display region of the substrate; and at least one bank disposed in the non-display region of the substrate and surrounding the display region. The at least one bank comprises at least one inorganic layer and at least one metal layer, and the at least one inorganic layer encapsulates the at least one metal layer.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD +1

Solid state imaging device and producing method thereof

InactiveUS20060128044A1Low costReduce in quantitySemiconductor/solid-state device detailsSolid-state devicesInterconnectionCover glass

A semiconductor substrate of a solid state imaging device is connected to a cover glass, and then a backgrind is performed so as to make the thickness smaller. On a first face of the semiconductor substrate is formed plural units which is constructed of image sensors and plural contact terminals. At positions of the contact terminals, plural through-holes are formed on the bottom side of the semiconductor substrate, and the contact terminals appear on a second surface of the semiconductor substrate. On an interconnection circuit pattern of the assembly substrate are formed stud bumps. When the semiconductor substrate is assembled onto the assembly substrate, the stud bumps enter into the through-holes to contact to the contact terminals. Thus the interconnection circuit pattern is electrically connected to the image sensors.

Owner:FUJIFILM CORP

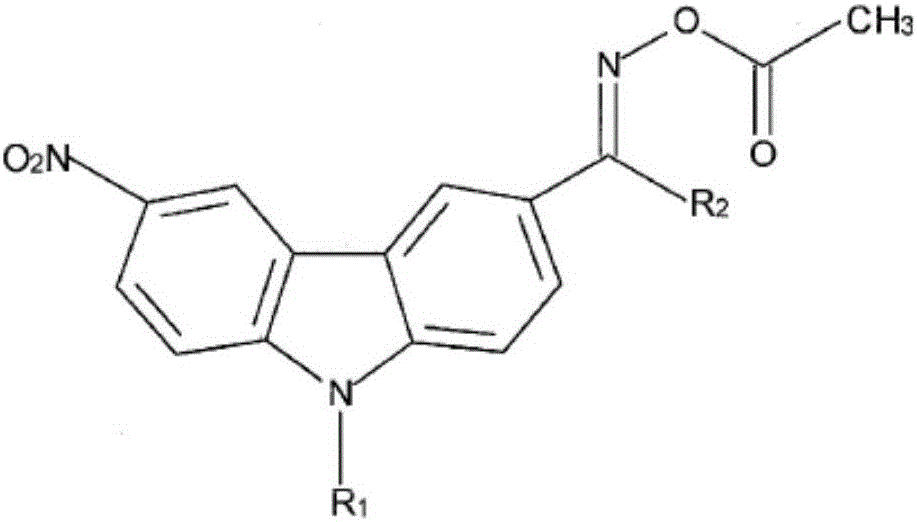

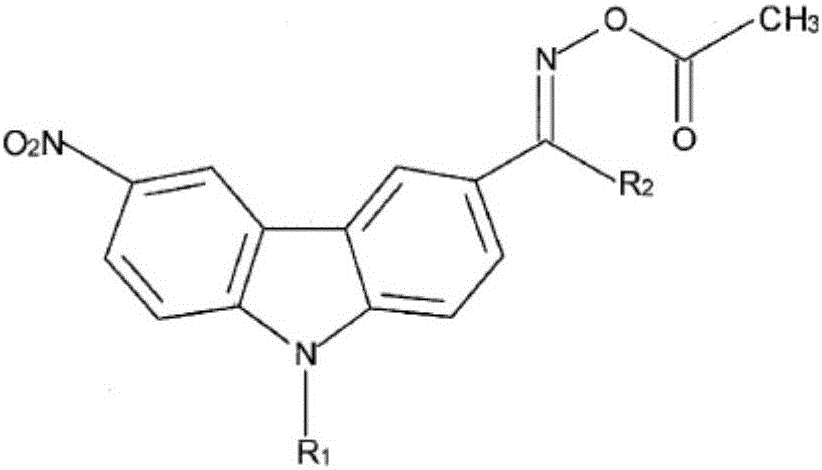

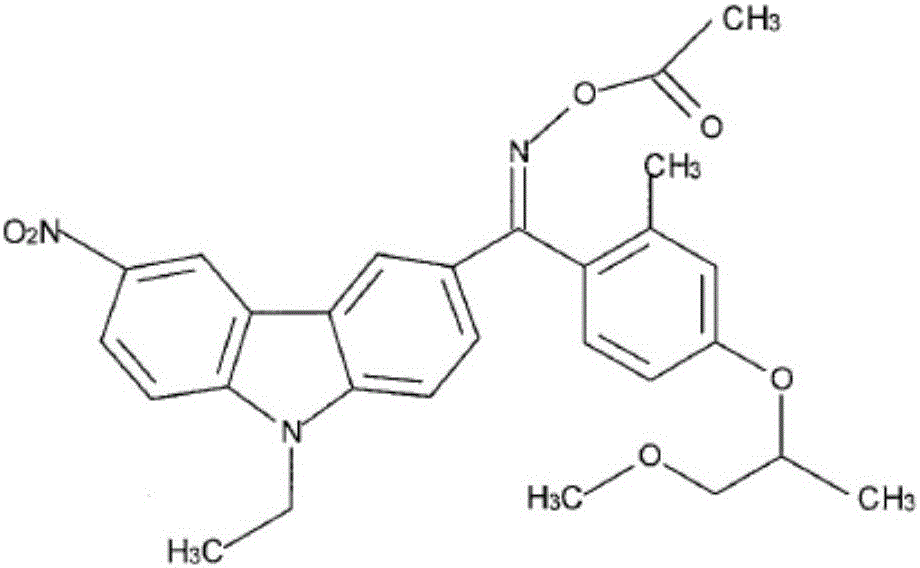

Photosensitive resin composition

InactiveCN106814539AShorten the exposure processHigh sensitivityPhotosensitive materials for photomechanical apparatusEpoxyPhenyl group

The invention aims to provides a photosensitive resin composition. The basic characteristics such as electrical insulation property are not destroyed. The photosensitive resin composition is exposed by a direct scanning device, the inner of the coating has a photo curing property and good sensitivity, the linear shape deterioration of a cured object is avoided, and excellent resolution is obtained. The photosensitive resin composition comprises (A) carboxyl containing photosensitive resin, (B) a polymerization initiator, (C) epoxy compounds, and (D) a coloring agent. The (B) polymerization initiator is represented by a formula, wherein in the formula, R1 represents H, a C1-C17 alkyl group, or a C1-C17 alkoxyl group, and R2 represents a phenyl group substituted by at least one of a phenyl group, a C1-C5 alkyl group, -O-CmH2m-CH3-, and -O-CnH2n-CpH2p-CH3, wherein m, n, and p all represent an integer from 1 to 5.

Owner:TAMURA KK

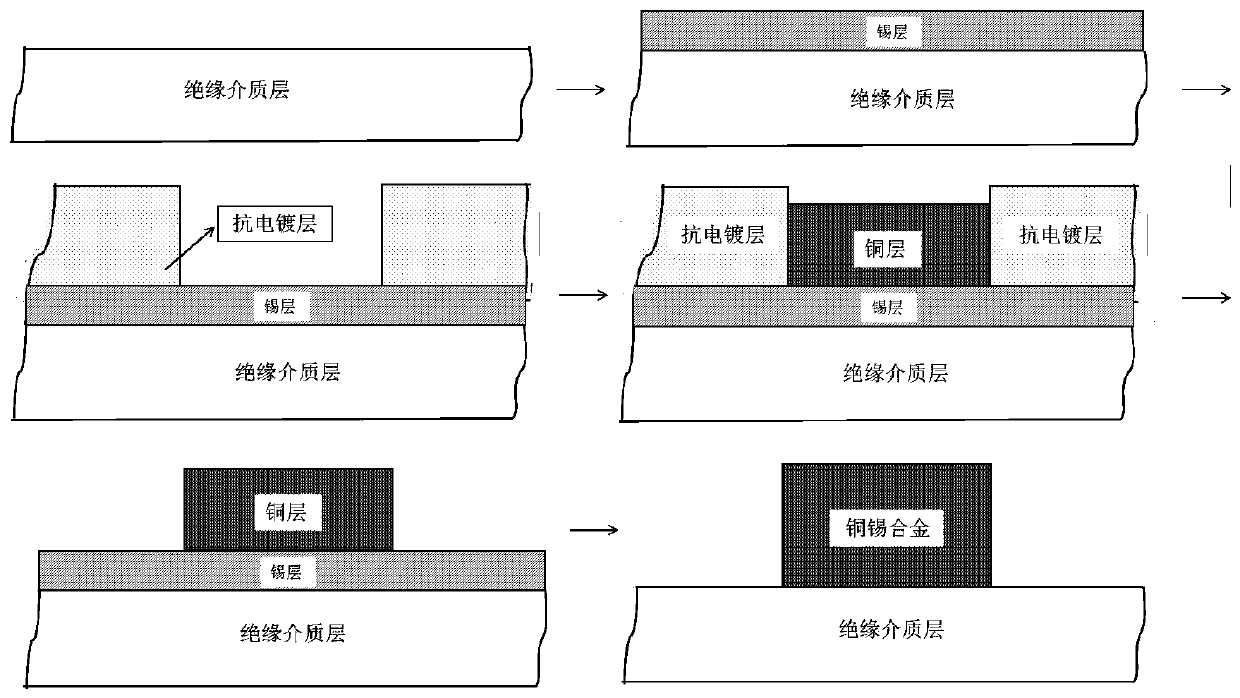

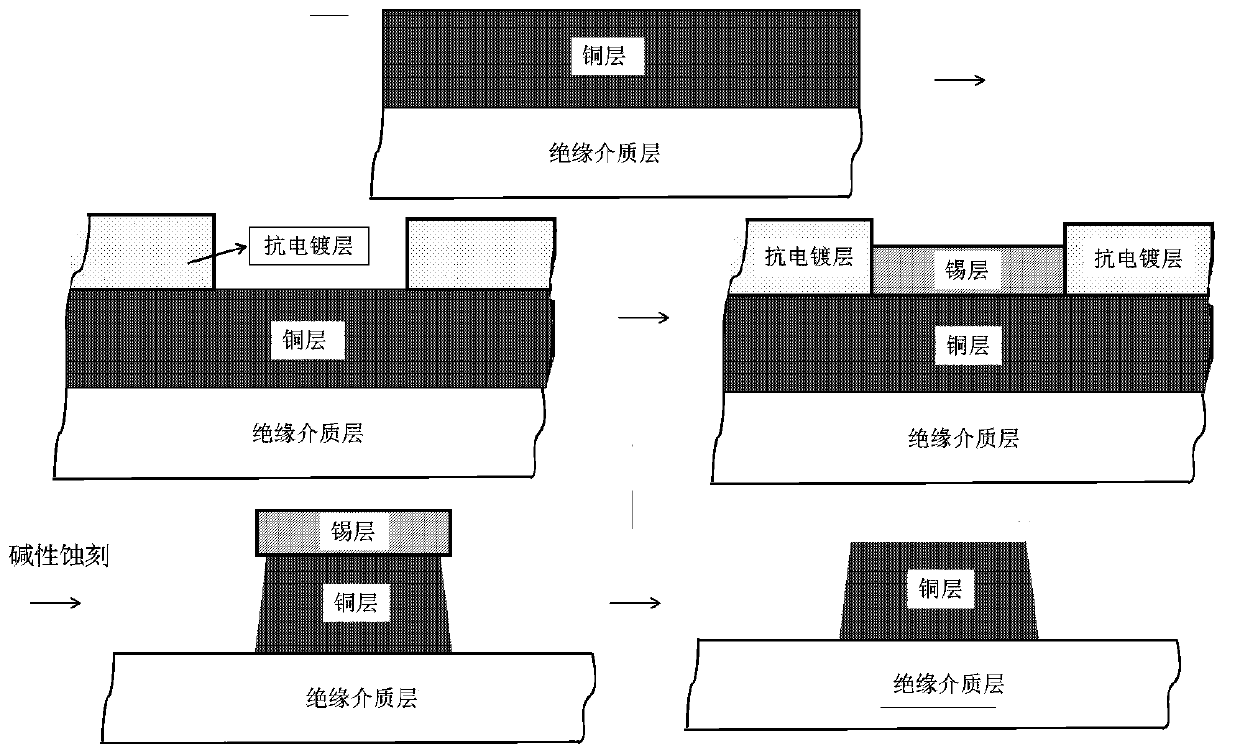

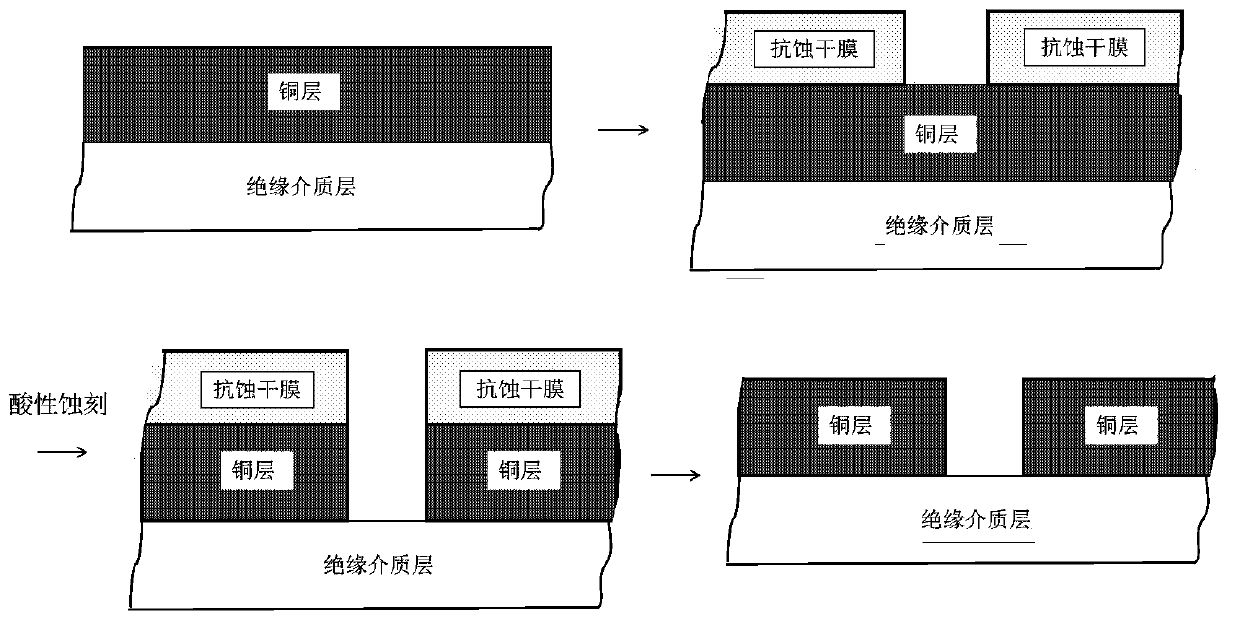

Manufacturing method of printed circuit conductive circuit

PendingCN111405771AAvoid over etchingAvoid poor thermal stabilityConductive material chemical/electrolytical removalElectrically conductiveEtching

The invention discloses a manufacturing method of a printed circuit conductive circuit, and relates to the technical field of printed circuit board manufacturing. The method comprises the following steps: (1) growing a tin seed layer on the surface of a printed circuit insulating substrate; (2) covering the tin seed layer with a patterned dry film; (3) electroplating copper to form a copper conductive circuit; (4) removing the dry film; (5) carrying out heat treatment on the substrate obtained after the treatment in the previous step, so that the copper conductive circuit and the tin seed layer are co-melted into a whole; and 6) etching the tin seed layer to obtain a printed circuit conductive circuit. According to the method, the tin layer etching speed is high, the precision is high, thecircuit is complete and free of side etching, and manufacturing of a high-precision circuit board is facilitated; meanwhile, the copper and the tin are eutectic to form a uniform alloy layer, so thatthe stress between the metals is released, the local defect caused by inconsistent etching speeds of the tin seed layer and the copper conductive wire is prevented, the binding force of the conductive circuit and a bottom layer insulating medium is ensured, and the circuit pattern is good in heat resistance, high in stability and high in reliability.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

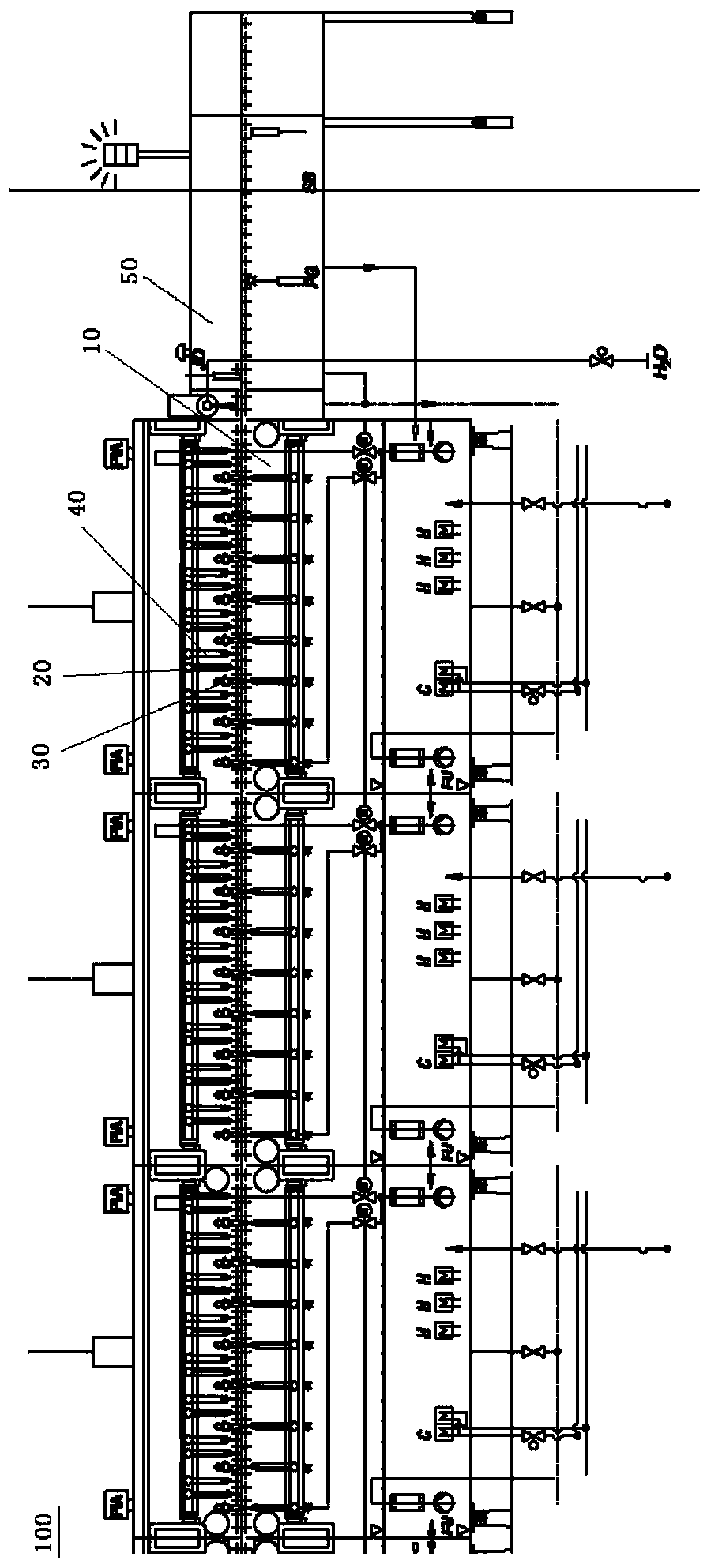

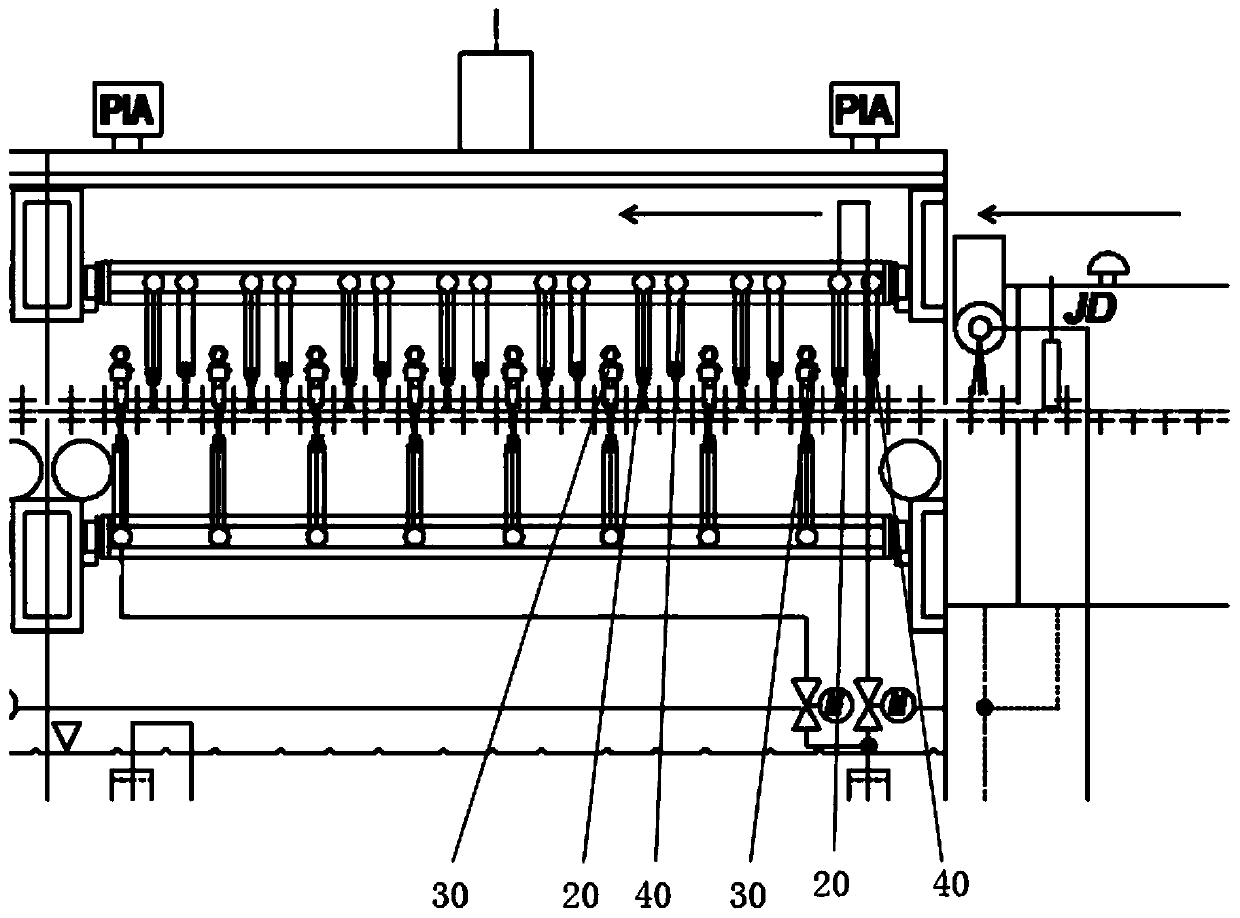

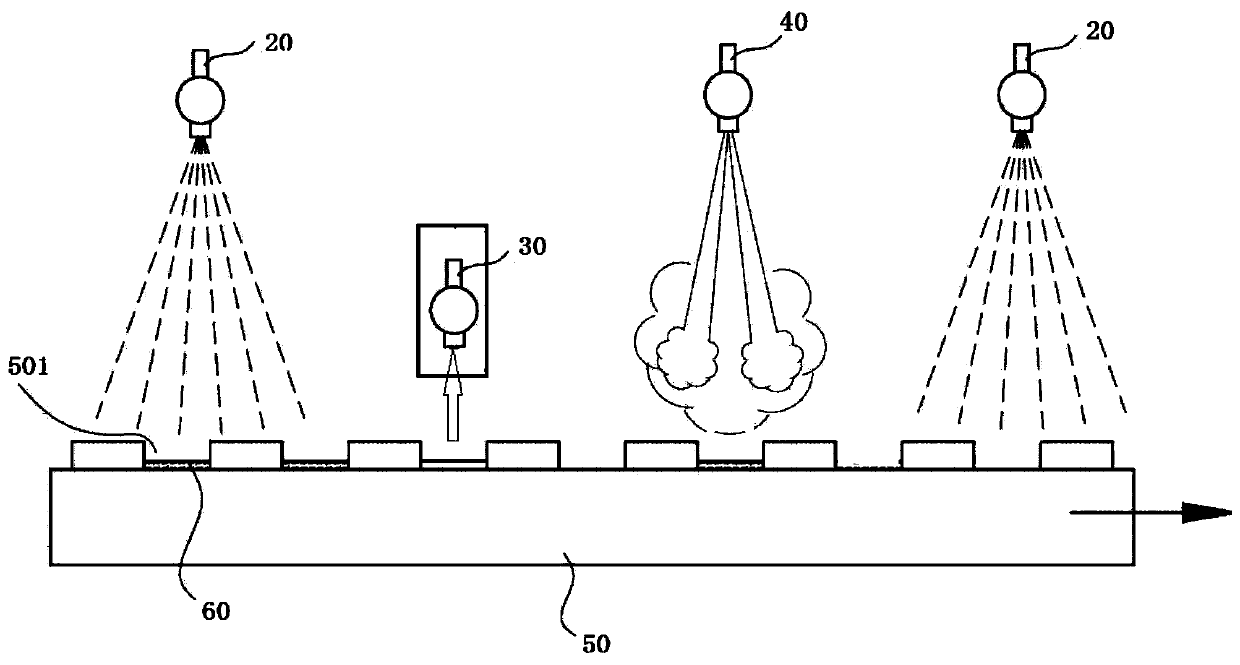

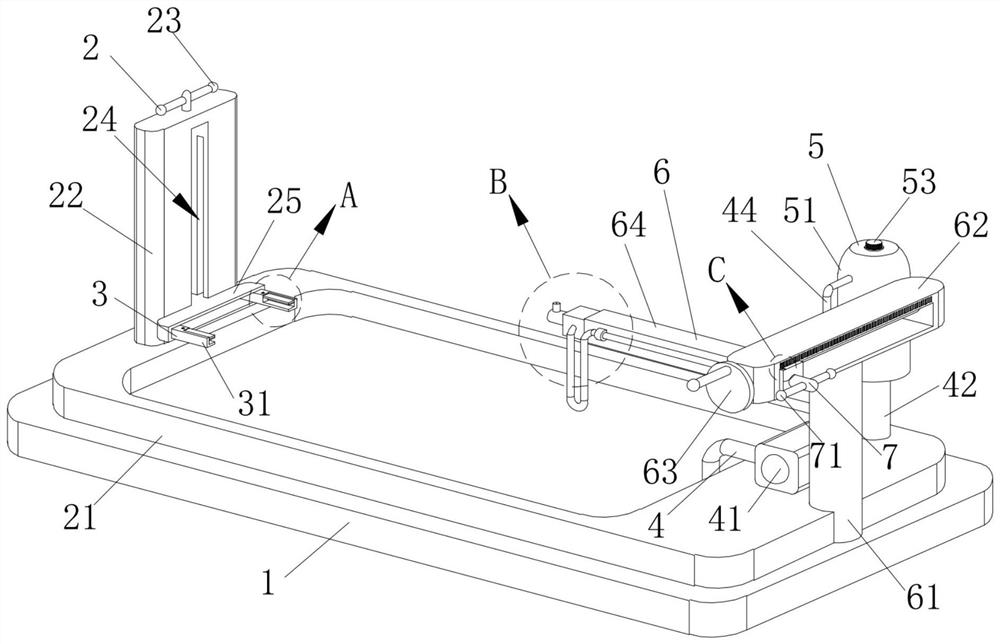

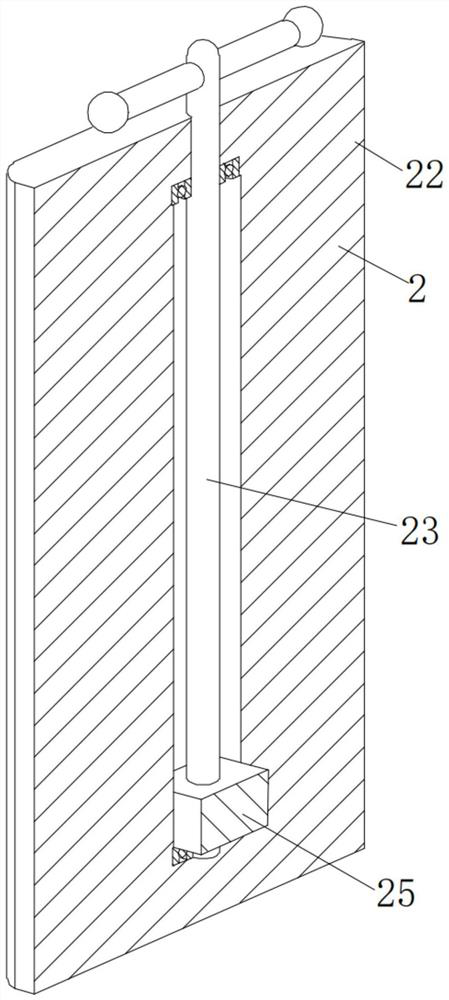

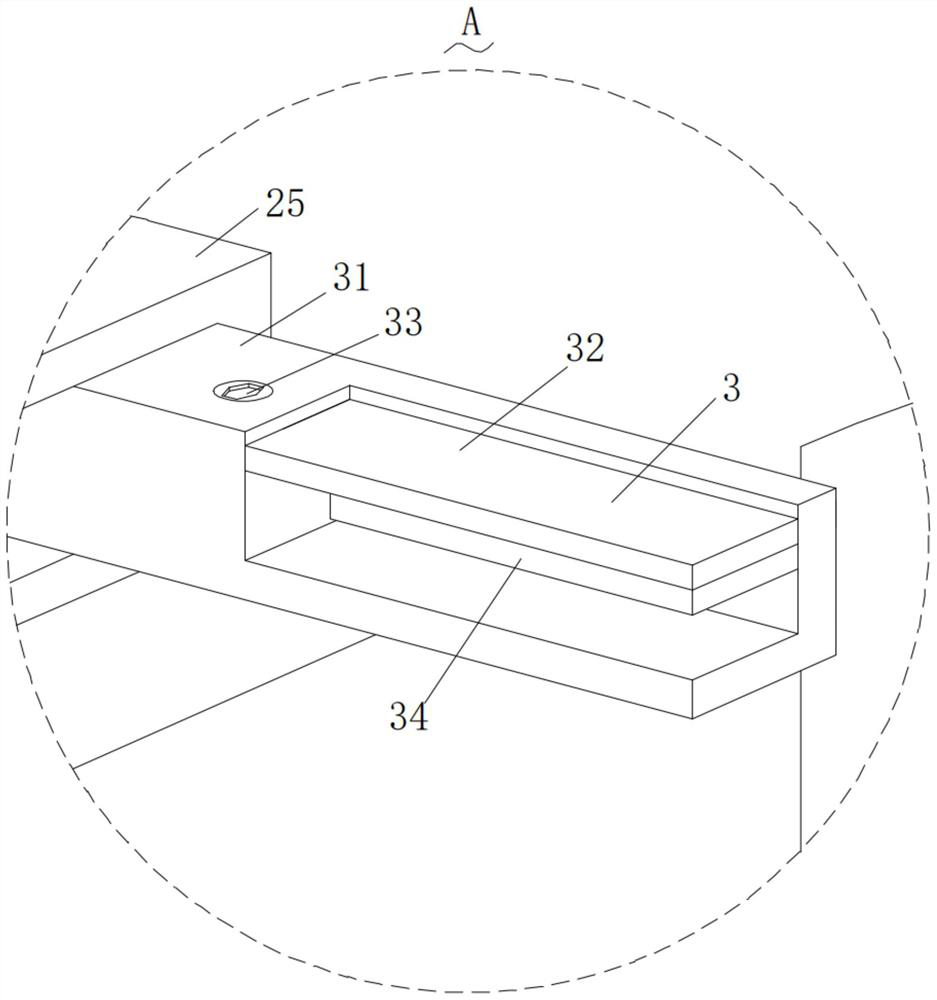

Etching device for circuit board

PendingCN111465203APrevent side erosionImprove responseConductive material chemical/electrolytical removalEtchingEngineering

The invention discloses an etching device for a circuit board. The etching device comprises a conveying device for conveying the circuit board along a preset direction, at least one spraying device, and at least air suction device, wherein any one of the spraying devices is arranged above the conveying device, the spraying device is used for spraying etching liquid to the circuit board, any one ofthe air suction devices is arranged above the conveying device, at least one air suction device is arranged at the downstream of the spraying device corresponding to the air suction devices along thepreset direction, so the air suction device can suck the reacted etching liquid sprayed by the spraying device corresponding to the air suction device. The etching device is advantaged in that by arranging the air suction devices, the etching liquid retained in the sunken area after reaction can be sucked, further lateral etching of the etching liquid retained in the sunken area is avoided, and the fresh etching liquid can better react with the circuit board.

Owner:郑振华

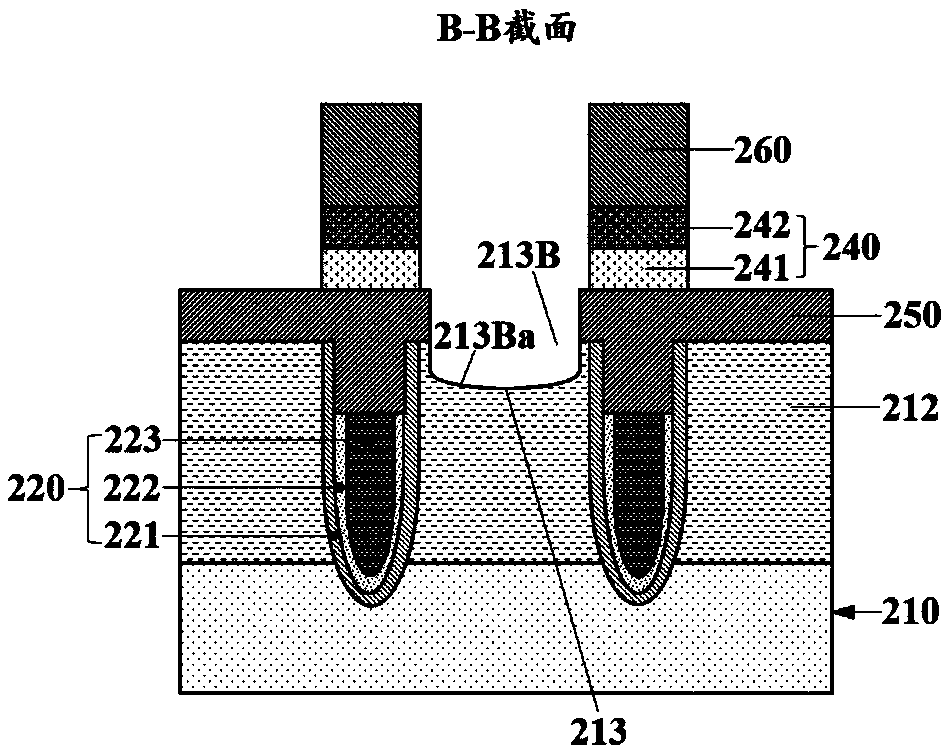

Semiconductor memory

The invention provides a semiconductor memory structure, which comprises a substrate, word lines, bit line contacts and bit lines, and is characterized in that a through channel is formed between every two adjacent word lines, each channel comprises a contact window and an inter-window groove, each inter-window groove is provided with a re-recessed surface relative to the contact window, and the re-recessed depth ranges from 5.8nm to 8.5nm, so that the adjacent bit line contacts are not electrically connected with each other; and the sum of the side etching depths of the bit line contact is indirect proportion to the re-recessing depth of the inter-window grooves in the extension direction of the word lines. The invention further provides another semiconductor memory structure, which is characterized in that the contact window in the channel is provided with a re-recessed surface relative to the inter-window groove, and the re-recessed surface is lower than the surface of an isolationstructure in the channel; and each bit line contact has a vertical sectioning profile in the extension direction of the word lines. By controlling the proportion of the etching agent gas or selectingdifferent etching agents, the problem of serious side etching of the bit line contacts due to the formation of the relatively low re-recessed surface of the inter-window grooves is effectively solved.

Owner:CHANGXIN MEMORY TECH INC

Substrate and preparation method thereof and display panel

InactiveCN111725436APrevent side erosionImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingStructural engineeringMetal membrane

The invention provides a substrate and a preparation method thereof, and a display panel. The substrate comprises: a substrate; a first conducting layer which is formed on the substrate and patternedto form a first metal wire, wherein the first conducting layer is of a multi-film-layer structure composed of first metal and second metal, and the surface, away from the substrate, of the first conducting layer is a first metal film layer, wherein the first metal is not easy to etch, and the second metal is easy to etch; an insulating layer formed on the first conducting layer; and a second conducting layer which is formed on the insulating layer and is patterned to form a second metal wire and a first metal protection wire, and the first metal protection wire covers the side edge, which is not covered by the insulating layer, of the first metal wire. The first metal protection line is arranged on the side edge, which is not covered by the insulating layer, of the first metal line, so that the side edge, which is not covered by the insulating layer, of the first metal line is protected, the first metal line is prevented from being laterally etched in the etching process of the secondconducting layer, and the product reliability and the manufacturing yield are improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

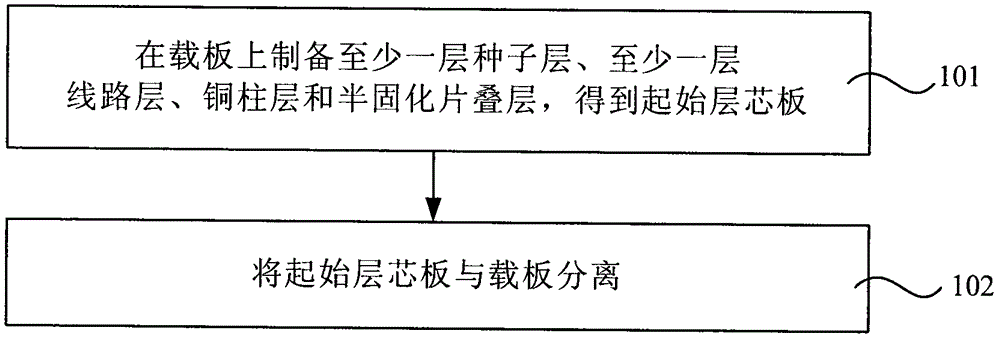

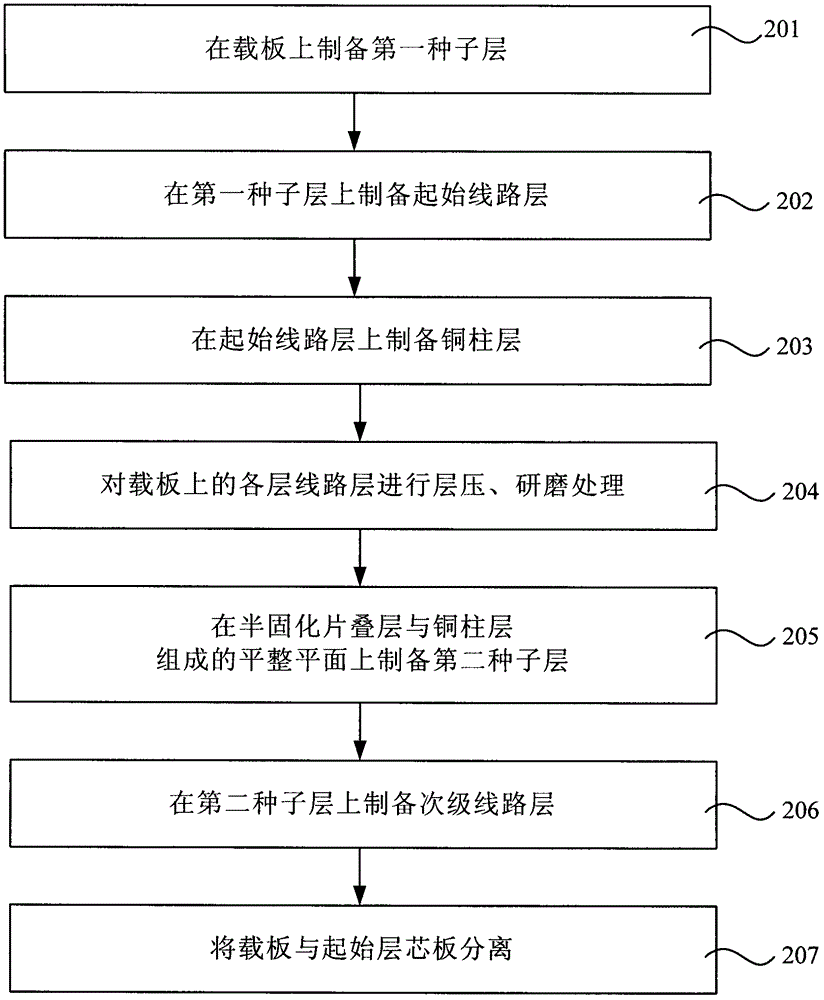

Starting Layer Core Method

ActiveCN102573335BReduce manufacturing costImprove yieldMultilayer circuit manufactureEtchingSurface roughness

The present invention provides a method for manufacturing an initial layer core board, which includes: preparing at least one seed layer, at least one circuit layer, copper pillar layer and prepreg lamination on a carrier plate to obtain an initial layer core board; The starting layer core plate is separated from the carrier plate; the carrier plate is made of stainless steel or aluminum alloy or titanium alloy. The manufacturing method of the starting layer core board provided by the present invention, by selecting the carrier board made of stainless steel with surface polishing, avoids the high roughness of the carrier board made of copper and affects the quality of the circuit layer, which is conducive to reducing the thickness of the seed layer , reduce the manufacturing cost of the starting layer core board, and then use ultrasonic separation technology to separate the carrier board and the starting layer core board, avoiding the side erosion of the circuit layer when the carrier board and the starting layer core board are separated by etching, thus Improve the yield of starting layer core board.

Owner:NEW FOUNDER HLDG DEV LLC

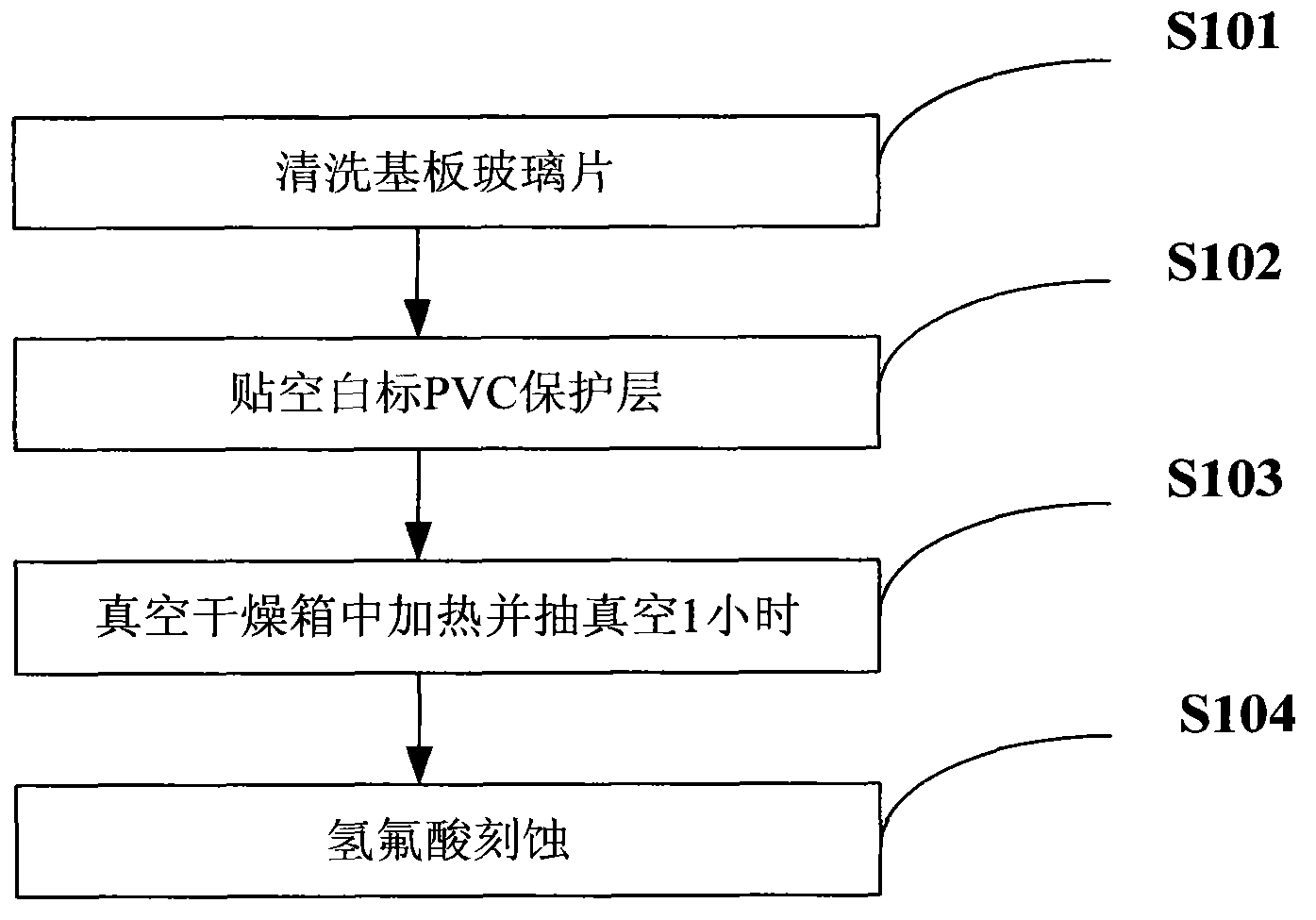

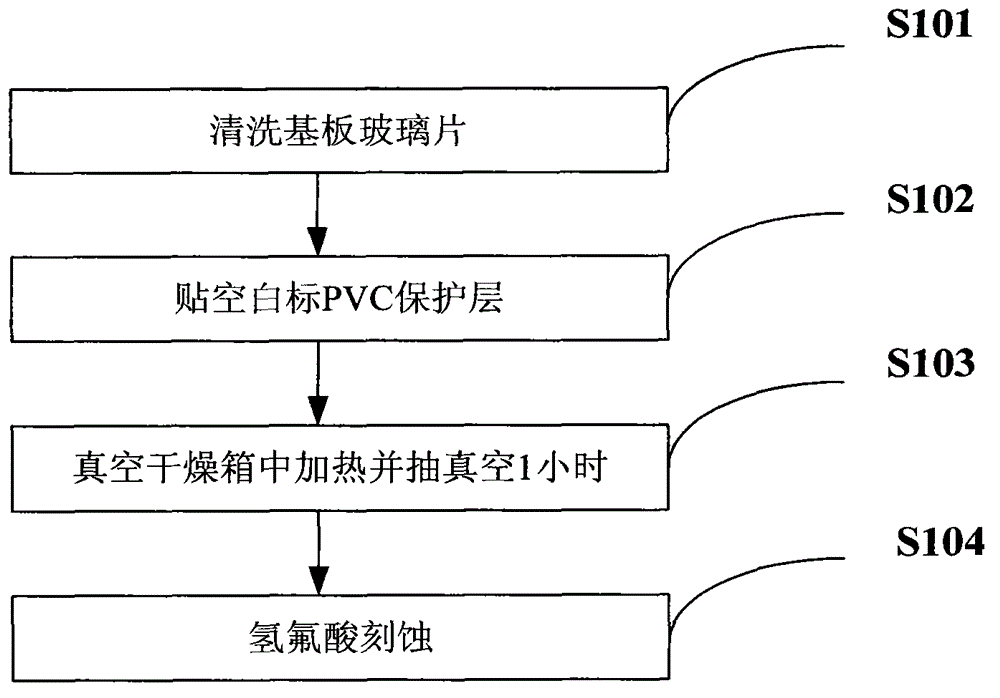

Anti-lateral erosion technology for chemically forming toughened glass cover lens

The invention discloses an anti-lateral erosion technology for chemically forming a toughened glass cover lens. The anti-lateral erosion technology comprises the following steps: cleaning a substrate glass sheet, sticking blank tabs (PVC protective layers); heating and vacuumizing for 1 hour in a vacuum drying oven; and etching with hydrofluoric acid. The invention provides the novel technology widely used for chemically forming a capacitance type touch screen glass cover lens. In the chemical forming process of the capacitance type touch screen glass cover lens, when ineffective parts are etched with hydrofluoric acid, hydrofluoric acid laterally etches from the edge of the protective layers to damage effective parts. By using a vacuum drying technology, the blank tags are heated at a certain temperature and under the standard vacuum environment to ensure the edges of the protective layers to be quickly closed up to effectively prevent the lateral erosion. Through the method, the blank tags are dried quickly, the lateral erosion is reduced effectively, and the processing efficiency and the yield of the glass cover lens are improved.

Owner:城步新鼎盛电子科技有限公司

Etching solution, touch panel and manufacturing method of touch panel

PendingCN113126831APrevent side erosionMeet the needs of narrow bordersInput/output processes for data processingEngineeringTouch panel

The invention discloses an etching solution, a touch panel and a manufacturing method of the touch panel, and the manufacturing method of the touch panel comprises the following steps: providing a substrate which is provided with a display region and a peripheral region; a metal layer and a metal nanowire layer are arranged, the first part of the metal nanowire layer is located in the display region, and the second part of the metal nanowire layer and the metal layer are located in the peripheral region; the patterning step comprises the steps that etching liquid capable of etching the metal layer and the metal nanowire layer is used for forming a plurality of peripheral leads on the metal layer and forming a plurality of etching layers on the second part of the metal layer at the same time, and the etching liquid comprises hydrogen peroxide (0.2-40 wt%), acid (0.2-20 wt%), a metal corrosion inhibitor (0.1-10 wt%) and / or a stabilizing agent (0.1-10 wt%). In addition, the invention also provides an etching solution and a touch panel. Patterning of the metal nanowire layer or the metal layer is directly carried out through the etching liquid, so that the purpose of simplifying the manufacturing process is achieved, and the manufacturing cost is further controlled.

Owner:CAMBRIOS FILM SOLUTIONS CORP

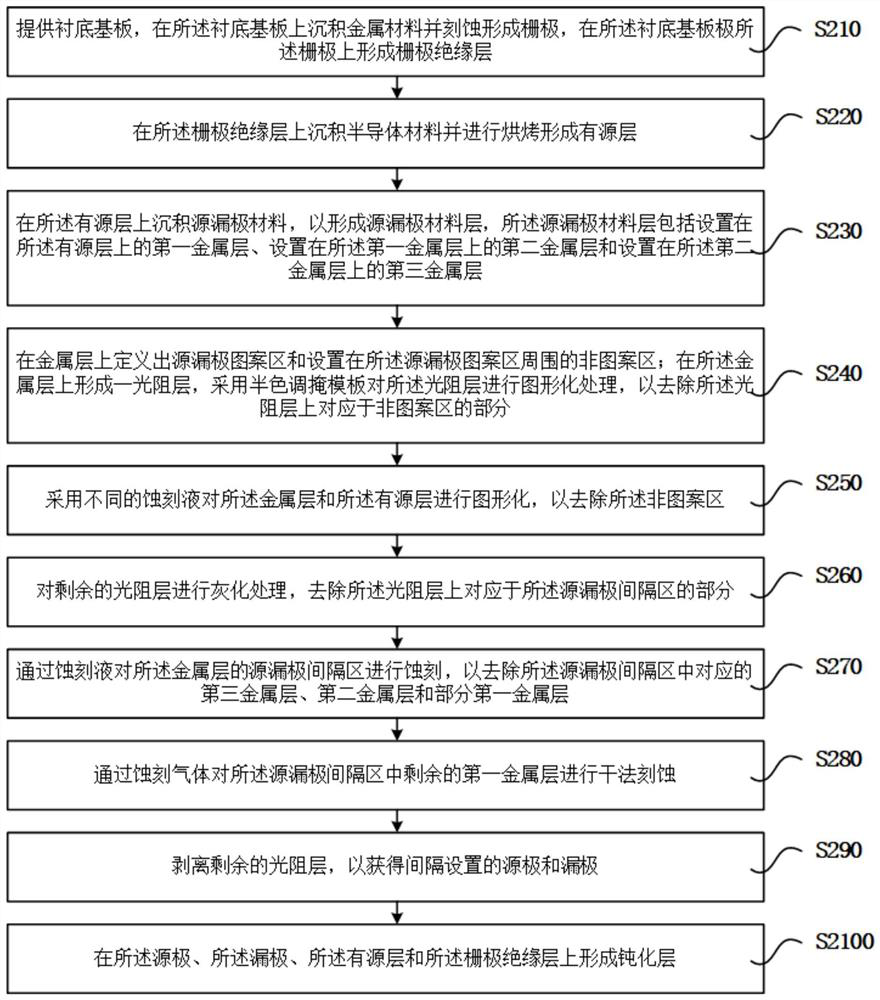

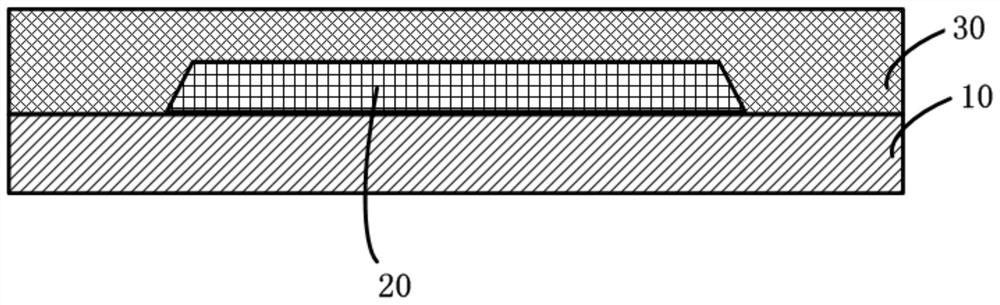

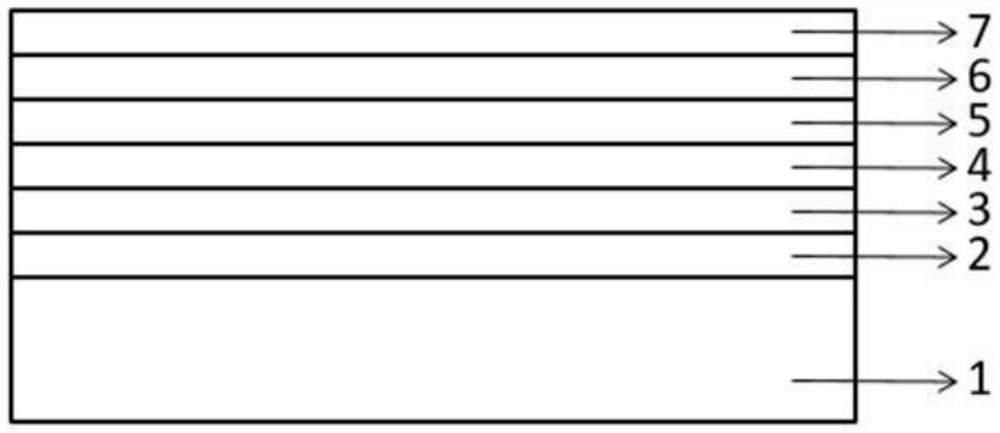

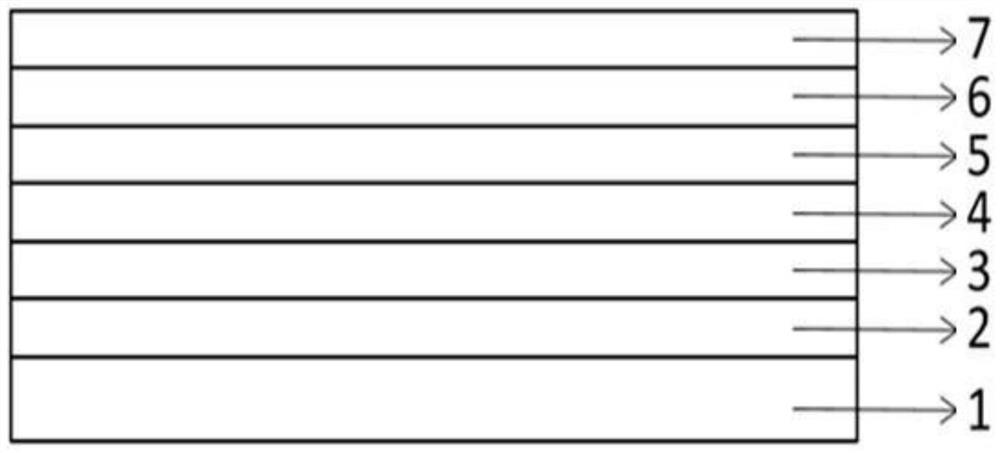

TFT substrate and its preparation method, display device

ActiveCN110676266BThin line widthMeet the needs of devices with smaller form factorsSolid-state devicesSemiconductor/solid-state device manufacturingIndiumPhysical chemistry

The invention discloses a TFT substrate, a preparation method thereof, and a display device, which can make the line width of the copper film layer in the back channel etching-indium gallium zinc oxide type TFT substrate thinner, so that it can be applied to higher resolution At the same time, the molybdenum film layer as the bottom layer of the channel is dry-etched by NF3 and O2 etching gases to prevent the indium gallium zinc oxide film layer from being damaged.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Preparation method of high-brightness infrared light emitting diode core and diode core

PendingCN113328013AImprove luminous brightnessSimple processSemiconductor devicesWaferingOhmic contact

The invention relates to a preparation method of a high-brightness infrared light emitting diode core and a diode core. The preparation method comprises the following steps of thinning a wafer, manufacturing an ohmic contact layer and an electrode layer, manufacturing an electrode pattern, cutting the diode core and coarsening to obtain an adhesive film, an N-surface electrode, a GaAs substrate, an epitaxial layer, an ohmic contact layer and a P-surface electrode from bottom to top in sequence. The epitaxial layer comprises the diode core of the N-type GaAs, the N-type limiting layer, the MQW quantum well layer, the P-type limiting layer, the P-type GaAs and the P-type GaP contact layer from bottom to top, the cost is greatly reduced, and the brightness is obviously improved.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS

Thick copper circuit board and manufacturing method thereof

ActiveCN113630977AReduce thicknessSuppression of the pool effectElectrical connection printed elementsConductive material chemical/electrolytical removalThin membraneLaser ablation

The invention provides a manufacturing method of a thick copper circuit board, which comprises the steps of providing a copper-plated substrate which comprises a base material layer and a first copper layer, and etching the first copper layer to form a first circuit layer; covering the first circuit layer with a filler layer; performing laser ablation on the top layer of the filler layer to expose the first circuit layer; forming a metallized film on the upper surface of the filler layer; forming a second copper layer to the surfaces of the metalized film and the first circuit layer; and etching the second copper layer to form a second circuit layer. According to the manufacturing method of the thick copper circuit board, the filler layer and the metallized film are arranged on the first circuit layer, and the second circuit layer is formed by taking the first circuit layer and the filler layer as references, so that the purpose of thickening the copper layer is achieved, the pool effect can be inhibited, and lateral erosion is avoided. The invention further provides a thick copper circuit board.

Owner:AVARY HLDG (SHENZHEN) CO LTD +1

Etching device of printed circuit board for new energy automobile

ActiveCN113747672AHeight adjustableImprove spraying effectCircuit board tools positioningNew energyEngineering

The invention relates to the technical field of circuit board etching, in particular to an etching device of a printed circuit board for a new energy automobile, which comprises a bottom frame, a lifting structure is mounted on the bottom frame, the lifting structure is connected with a clamping structure, a liquid pumping structure is arranged on the lifting structure, and a heat preservation structure is mounted on the liquid pumping structure. The lifting structure is connected with an adjusting structure, a telescopic structure is mounted on the adjusting structure, and the spraying position can be well and accurately adjusted in the x-axis direction and the y-axis direction through the adjusting structure and the telescopic structure, so that each position of the circuit board can be accurately sprayed; in addition, etching is carried out in a spraying mode, lateral erosion can be effectively prevented, and compared with spraying of a spraying can, the device can etch different circuit boards all the time in a faster and more environment-friendly mode.

Owner:深圳久筑科技有限公司

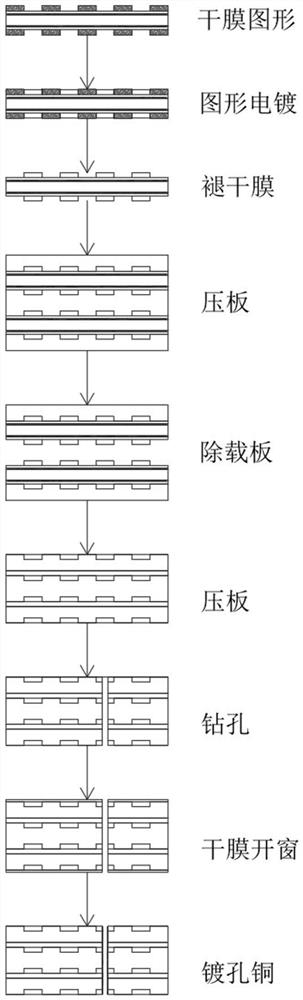

Process for manufacturing graph in circuit burying mode

ActiveCN112165773AReduce intensityPrevent side erosionConductive material mechanical removalAdhesiveStructural engineering

The invention discloses a process for manufacturing a graph in a circuit burying mode. The process comprises the following steps: pasting copper foils to the two sides of a carrier plate through an adhesive; attaching a dry film to the carrier copper foil, and manufacturing a to-be-plated pattern on the dry film; electroplating the carrier core plate to which the dry film is attached; taking downthe dry film on the carrier core plate plated with the copper layer; laminating the plurality of carrier core plates plated with the copper layers; separating the copper layer on the carrier core plate from the carrier plate; pressing the core plate after the carrier plate is taken out again; drilling a hole in the laminated core plate; cleaning and wetting the drilled hole; attaching dry films tothe surfaces of the two sides of the laminated core plate, and forming holes in the drilled positions of the core plate; carrying out metallization treatment on the holes in the dry film openings inthe core plate; and taking down the dry films on the surfaces of the two sides of the core plate. The method has the advantages that the etching side etching problem is avoided, the manufactured circuit better meets the design requirement, and the capacity of a factory for manufacturing a board with a finer circuit is improved under the condition that traditional PCB equipment conditions are not changed.

Owner:GUANGZHOU TERMBRAY ELECTRONICS TECH CO LTD

Anti-lateral erosion technology for chemically forming toughened glass cover lens

Owner:城步新鼎盛电子科技有限公司