Universal computing circuit of neural network accelerator

A general-purpose computing and neural network technology, which is applied in the field of general-purpose computing module circuits, can solve problems such as poor flexibility, long hardware development cycle of convolutional neural network, and platform limitations, so as to reduce complexity, shorten reasoning time, and simplify The effect of the circuit design scheme

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

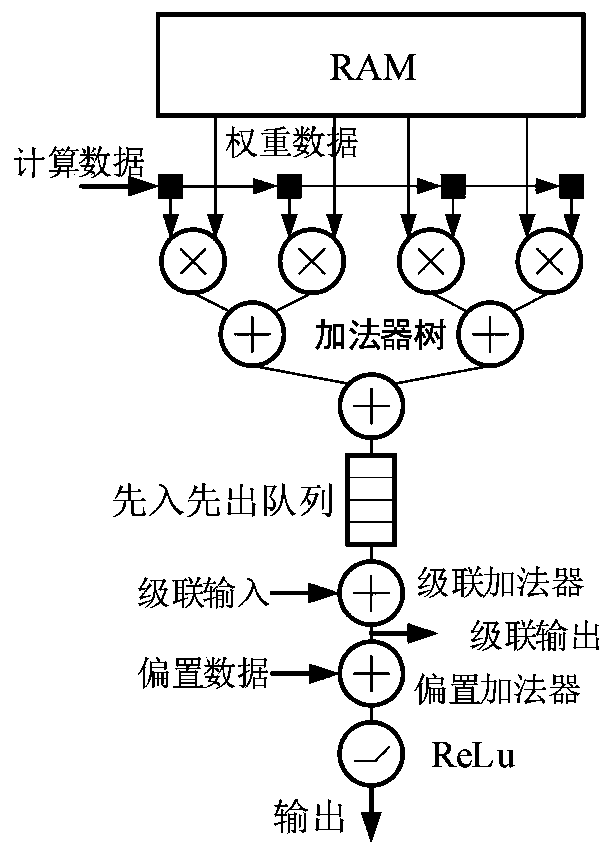

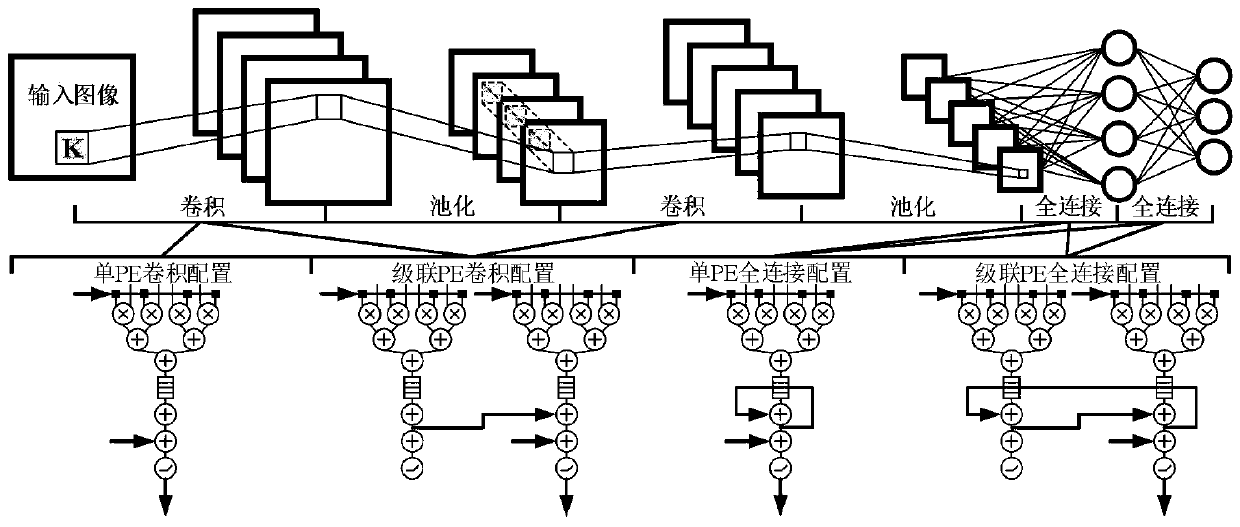

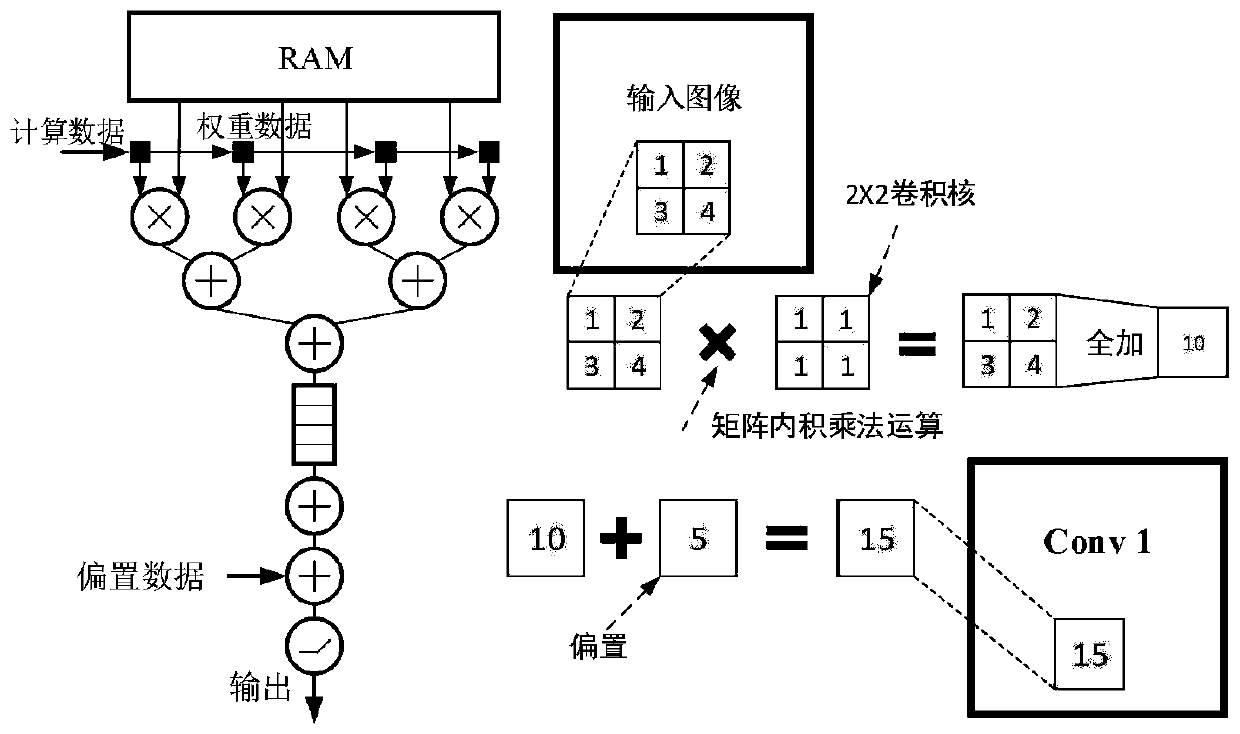

[0040] In this example, if figure 1 As shown, a general computing circuit of a neural network accelerator is composed of m general computing modules PE, wherein any general computing module PE is composed of RAM, 2 n A multiplier, an adder tree, a cascaded adder, an offset adder, a first-in-first-out queue, and a ReLu activation function module; in this embodiment, n=2, thus obtaining 4 multipliers

[0041] In the current cycle, the 4 multipliers obtain the stored weight data from the RAM, and receive and process the calculated data input from the outside, and then pass the 4 products in the current cycle to the adder tree;

[0042] The adder tree accumulates the 4 products in the current cycle, and after obtaining the accumulated sum in the current cycle, it is stored in the first-in-first-out queue;

[0043] The first-in-first-out queue will accumulate and read the current cycle and pass it to the cascaded adder, and the first-in-first-out queue will play the role of cachin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More